-

First production Batch!

08/31/2015 at 07:51 • 10 comments![]()

Now we have some board to spare, until today I only had one for testing, as form the first assembly round we assembled only 4 and 3 from those I sent to Pasadena..

-

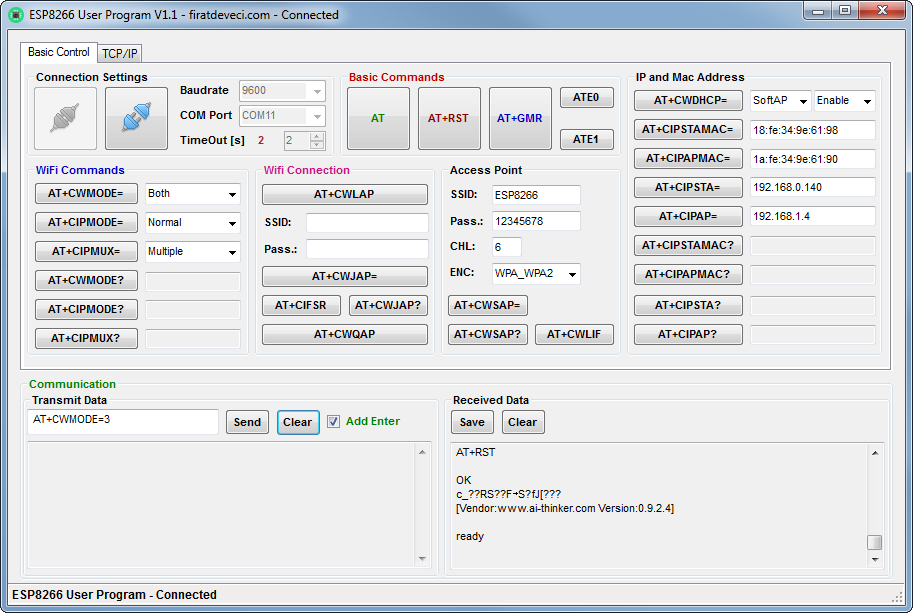

WiFi test with ESP8266

08/23/2015 at 17:11 • 0 comments![]()

The socket for ESP8266 is connected to the FPGA only, so we need to connect the ESP to UART for testing first.

This is just a "wiring" code for FPGA, creates wires from ESP to UART pin of FT2232H.

// ICEd UART to ESP8266 // What it does: connects FTDI channel B pins to ESP8266 UART module top( // RGB LED output LED_R, output LED_G, output LED_B, // Small SMD LED (green) output LED_small, // output ESP_TXD, input ESP_RXD, output ESP_RESET, input ESP_GPIO0, output ESP_GPIO2, // FTDI FT2232H Channel B input BDBUS0, output BDBUS1 ); assign LED_R = BDBUS0; assign LED_G = ESP_RXD; assign LED_B = 1'b1; assign ESP_GPIO2 = 1'b1; assign LED_small = ESP_GPIO0; assign ESP_TXD = BDBUS0; assign BDBUS1 = ESP_RXD; endmodule // topSure pin constraints too, then load the FPGA, and ready to test.First test worked - the only issue was wrong baudrate setting!

-

First Application with IceStorm toolchain

08/22/2015 at 11:28 • 0 commentsTime to test out IceStorm for some real project, I already had VHDL code that converts ICEd board to DIPSY programmer by making proper connections to the FTDI USB Chip on ICEd board. IceStorm supports verilog so here we go:

// ICEd as DIPSY programmer // What it does: connects FTDI channel B pins to DIPSY socket // so that Lattice and or other tools can see DIPSY UL1K SPI // Interface on FTDI channel B MPPSE pins module top( // RGB LED output LED_R, output LED_G, output LED_B, // Small SMD LED (green) output LED_small, // DIPSY Socket output DIPSY_MOSI, input DIPSY_MISO, output DIPSY_SCK, output DIPSY_SS, output DIPSY_RESET, input DIPSY_DONE, // FTDI FT2232H Channel B input BDBUS0, input BDBUS1, output BDBUS2, input BDBUS4, output BDBUS6, input BDBUS7); // We create "WIRES" here, they will be real connections! assign LED_R = 1'b0; assign LED_G = 1'b1; assign LED_B = 1'b1; assign LED_small = 1'b1; assign DIPSY_SCK = BDBUS0; assign DIPSY_MOSI = BDBUS1; assign BDBUS2 = DIPSY_MISO; assign DIPSY_SS = BDBUS4; assign DIPSY_RESET = BDBUS7; // optional assign BDBUS6 = DIPSY_DONE; endmodule // topThats it: the "assign" assigns input to output creating an electrical connection. But how does the code know to what pins those names belong? I was wondering too, but IceStorm tools support IceCube PCF constraints file:

# ############################################################################## # Constraint for ICEd board to be used DISPY in socket Programmer # ############################################################################## set_io BDBUS2 7 set_io BDBUS6 1 set_io BDBUS7 10 set_io DIPSY_RESET 45 set_io DIPSY_SS 49 set_io BDBUS0 9 set_io BDBUS4 3 set_io DIPSY_DONE 52 set_io DIPSY_MISO 39 set_io LED_B 97 set_io LED_R 99 set_io BDBUS1 8 set_io DIPSY_MOSI 41 set_io DIPSY_SCK 38 set_io LED_G 98 set_io LED_small 96This file does map symbolic names to the physical package pins.So how to compile?

REM IceStorm binary have to be ..\bin and ..\share ..\bin\yosys.exe -q -p "synth_ice40 -blif top.blif" top.v ..\bin\arachne-pnr -p top.pcf top.blif -o top.txt ..\bin\icepack top.txt top.binThis is script for Windows, for Linux it may be little different. First command does synthesis, then there is place and route and bitgen. As result we get a 32K binary file. This binary files contains the "configuration" that creates the actual electrical connection inside the FPGA package connecting some inputs pins to output pins.Did it work?

Yes, compiled once, tried once and worked first try. Both the same code with compiled with ICEcube as the version compiled with IceStorm.

True respect to IceStorm !

-

Progress on Documentation

08/22/2015 at 09:02 • 0 commentsIt is still not much but it is progressing, initial document wiki is setup

https://wiki.trenz-electronic.de/display/OSHW/TE0888+-+ICEd

Components for the next batch have arrived so we will assemble all PCB we have from first PCB order.

-

ICEd testing

08/18/2015 at 19:18 • 0 commentsICEd is mostly compatible to Lattice ICEstick, same FPGA many I/Os are at same pins, so a lot of code that works on ICEstick would also work on ICEd without changes.

Examples:

- yosys example "rot" compiled with ICEstorm (rot.bin) would blink the RGB LED on ICEd

- j1a.bin from swapforth would work also

Note when trying j1a.bin then need check the terminal setting because of DTR use for reset. With putty there would be possible no output, using parallax terminal I got response (UART setting 115200)

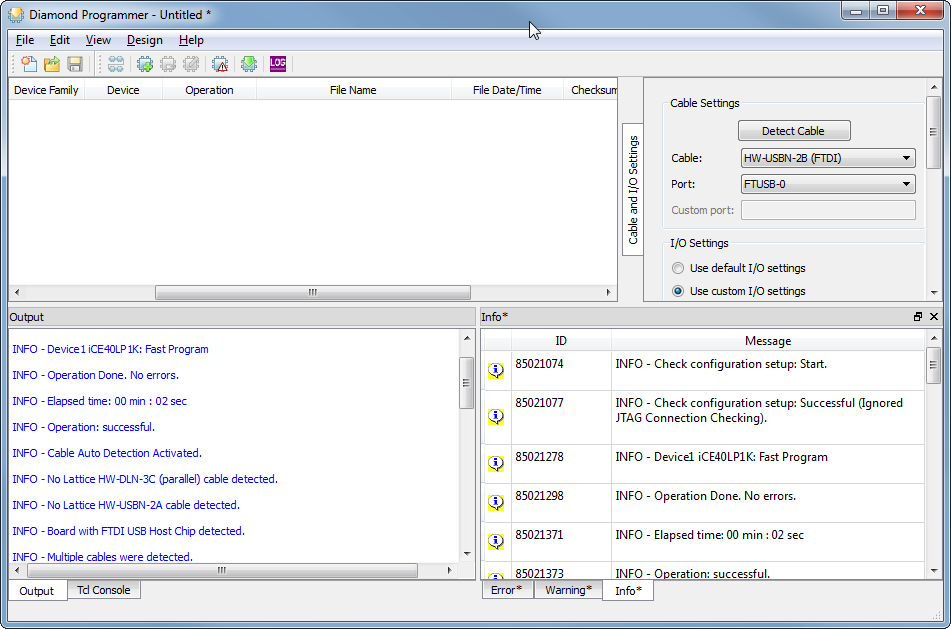

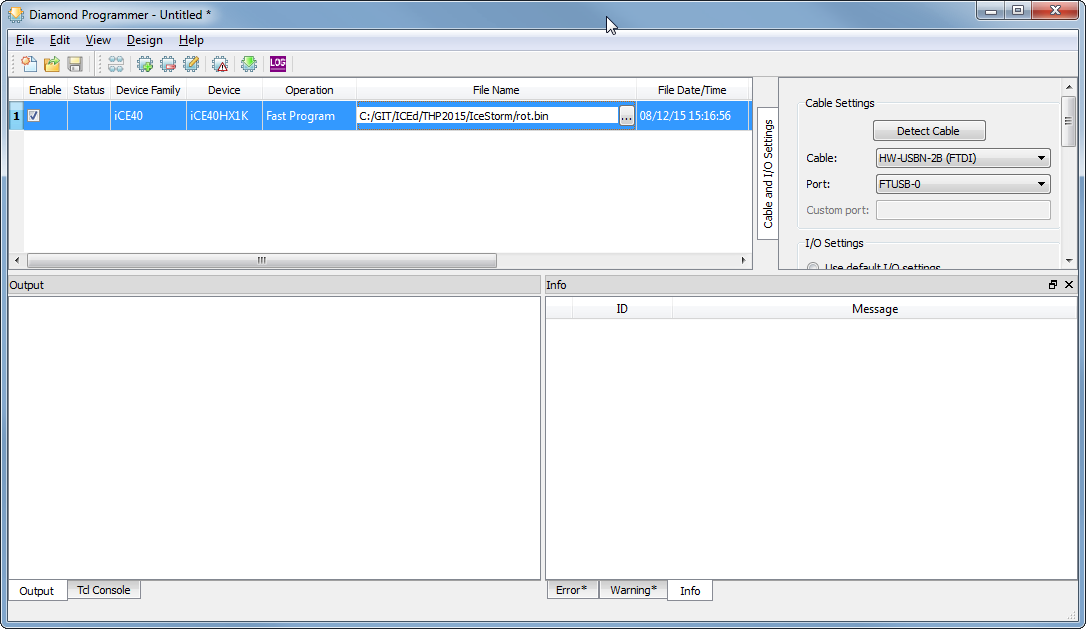

Step 1:

Connect micro USB Cable to ICEd

Step 2:

Click detect, make sure FTUSB-0 is selected as Port

![]()

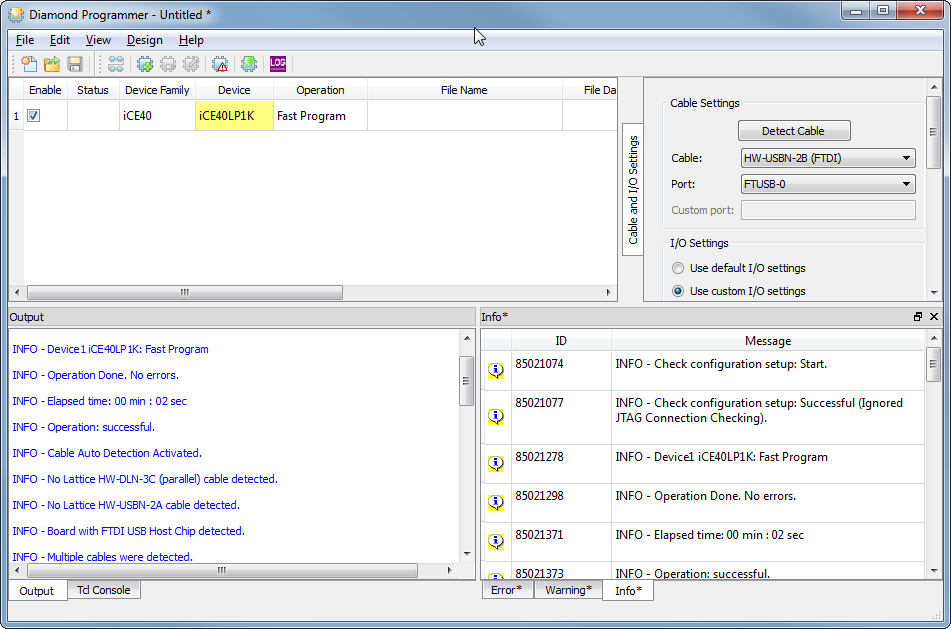

Step 3: Click scan

![]()

Step 4:

Click on the Yellow cell and select HX1K from drop down

![]()

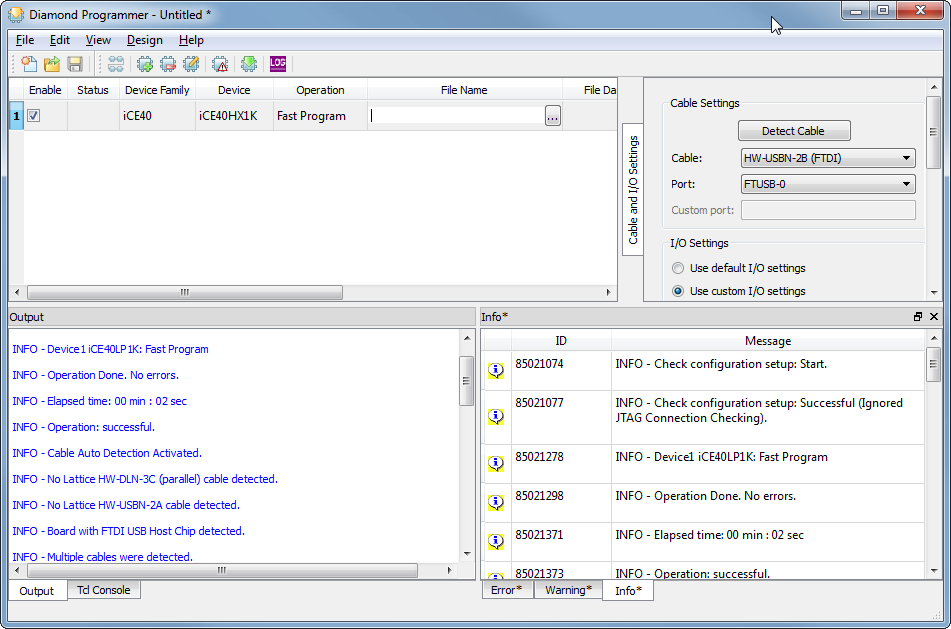

Step 5: Select say rot.bin from IceStorm project

can also grab here

https://github.com/AnttiLukats/ICEd/tree/master/THP2015/IceStorm

![]()

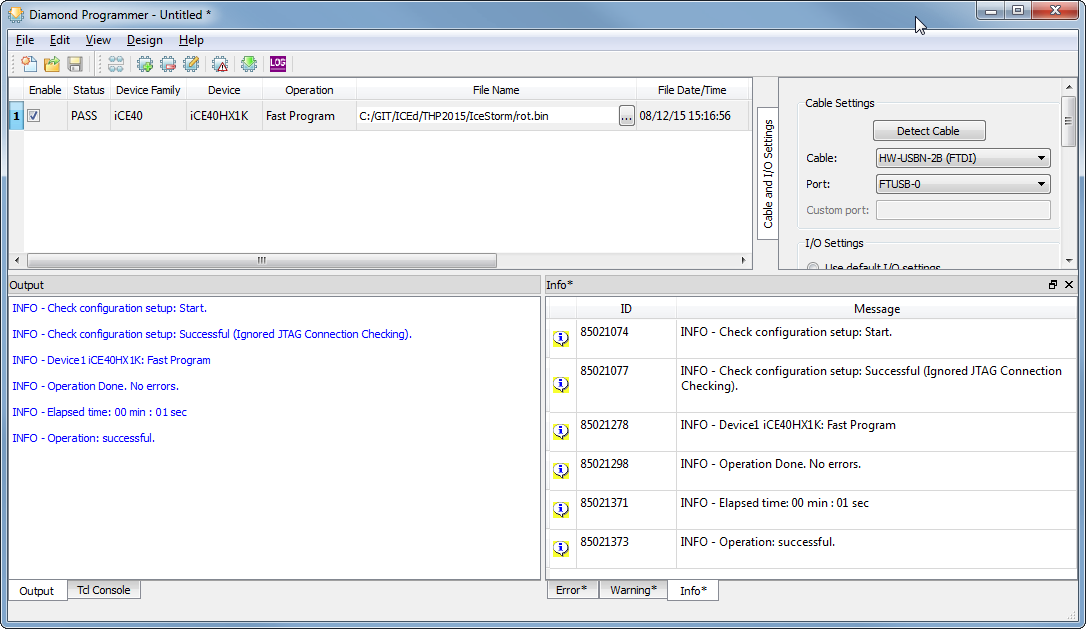

Step 6:

Click on green arrow, this will load the code into the HX1K configuration RAM

![]()

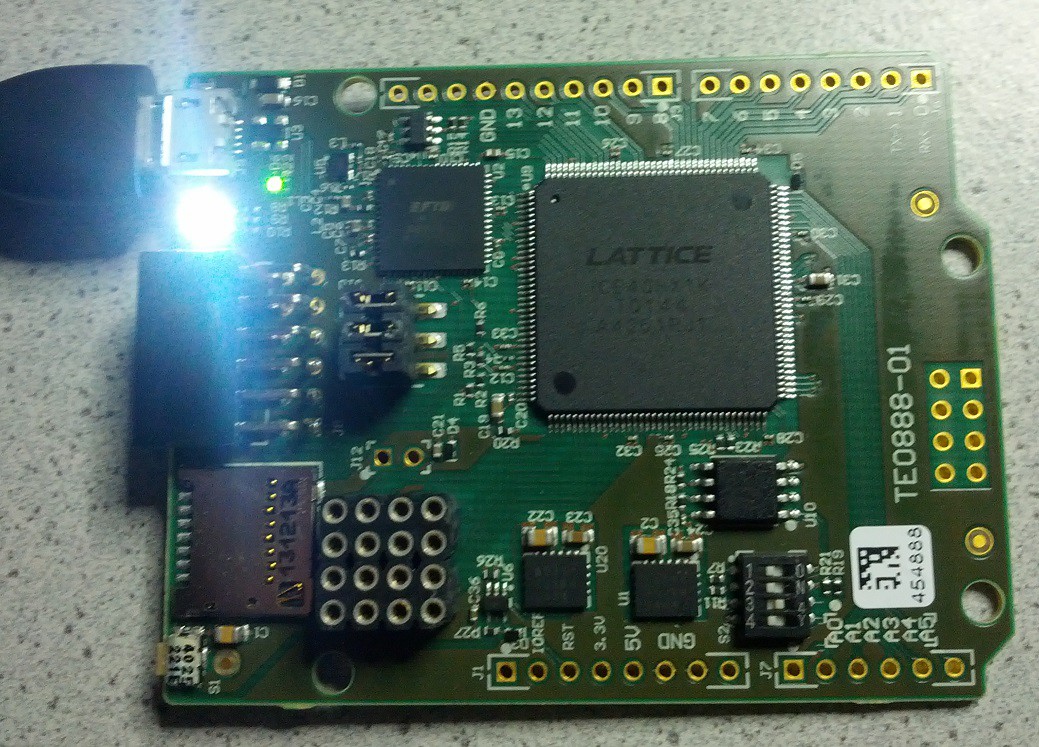

FPGA on ICEd is configured OK

![]()

Both the RGB LED and the small green SMD LED should blink: rot.v does toggle 5 LEDs (on ICEstick) ICEd has those 5 LEDS mapped to RGB LED and that small green one.

-

First production batch

08/17/2015 at 20:20 • 0 commentsThe remaining PCBs from the first PCB batch are also now in SMD Assembly, so we can soon send free samples to the project IceStorm folks.

This is amazing, you start a simple shell script that runs 3 programs, and from verilog you get ready FPGA bitstream in seconds. No need to install gigabytes of FPGA vendor tools, or ask for license or anything.

Just works.

-

Pushed to github

08/17/2015 at 18:43 • 0 commentsFull CAD source codes and generated files include BOM pushed to the project main github repo

https://github.com/AnttiLukats/ICEd

ups the repo path was wrong, fixed now

-

Porting the open FPGA toolchain to windows

08/14/2015 at 16:13 • 0 commentsIt is looking promising so far, most libraries needed to be included to compile all the parts that make up the FPGA toolchain are been compiled succesfully, hopefully the code gets fully compiled. Then there is no longer need to have extra VM for the FPGA toolchain, for those who work on non linux hosts.

Of course Lattice tools work on Windows OK.

-

J1a soft-cpu is running Forth!

08/12/2015 at 20:24 • 0 commentshttp://www.excamera.com/sphinx/article-j1a-swapforth.html

It just will work, 1:1 no changes, can take the precompiled j1a.bin, load it, and then you get the terminal to the forth system.

-

Open FPGA toolchain tested, working!

08/12/2015 at 14:14 • 0 commentsrot.v demo from ICEstorm, compiled, tested just working:

ICEd = an Arduino Style Board, with ICE FPGA

DIPSY-EPT Emulator and Programme Tool - Open Source Hardware for Open Source FPGA Toolchain

Antti Lukats

Antti Lukats