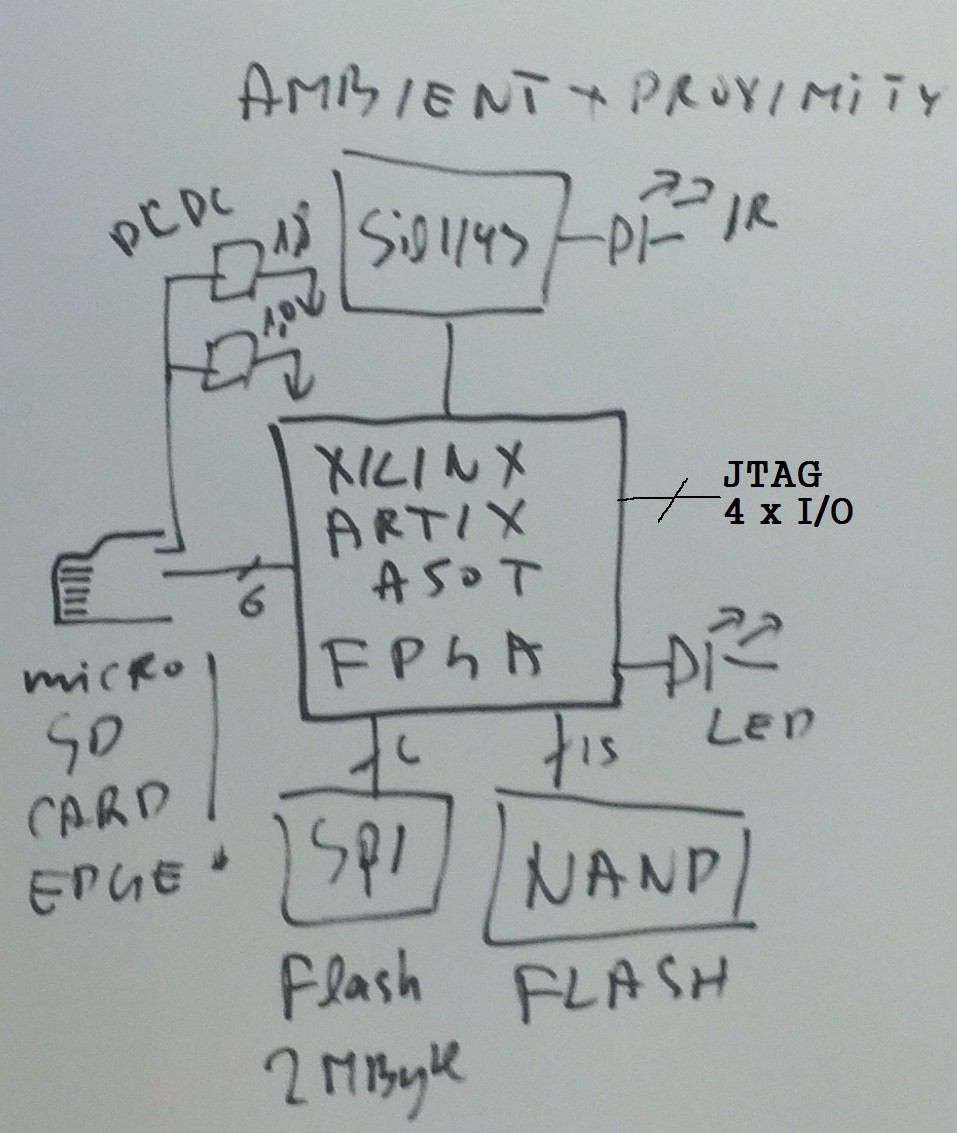

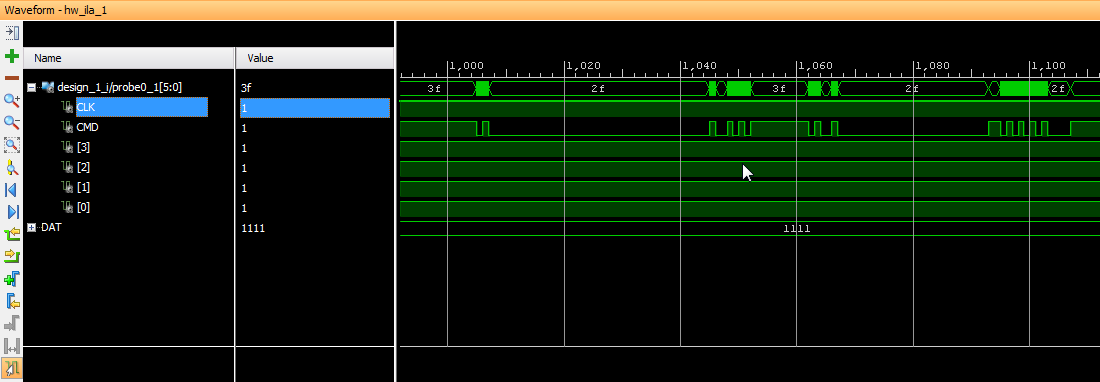

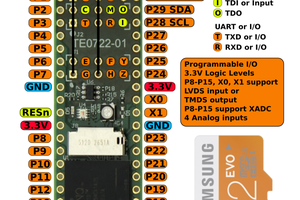

System Diagram

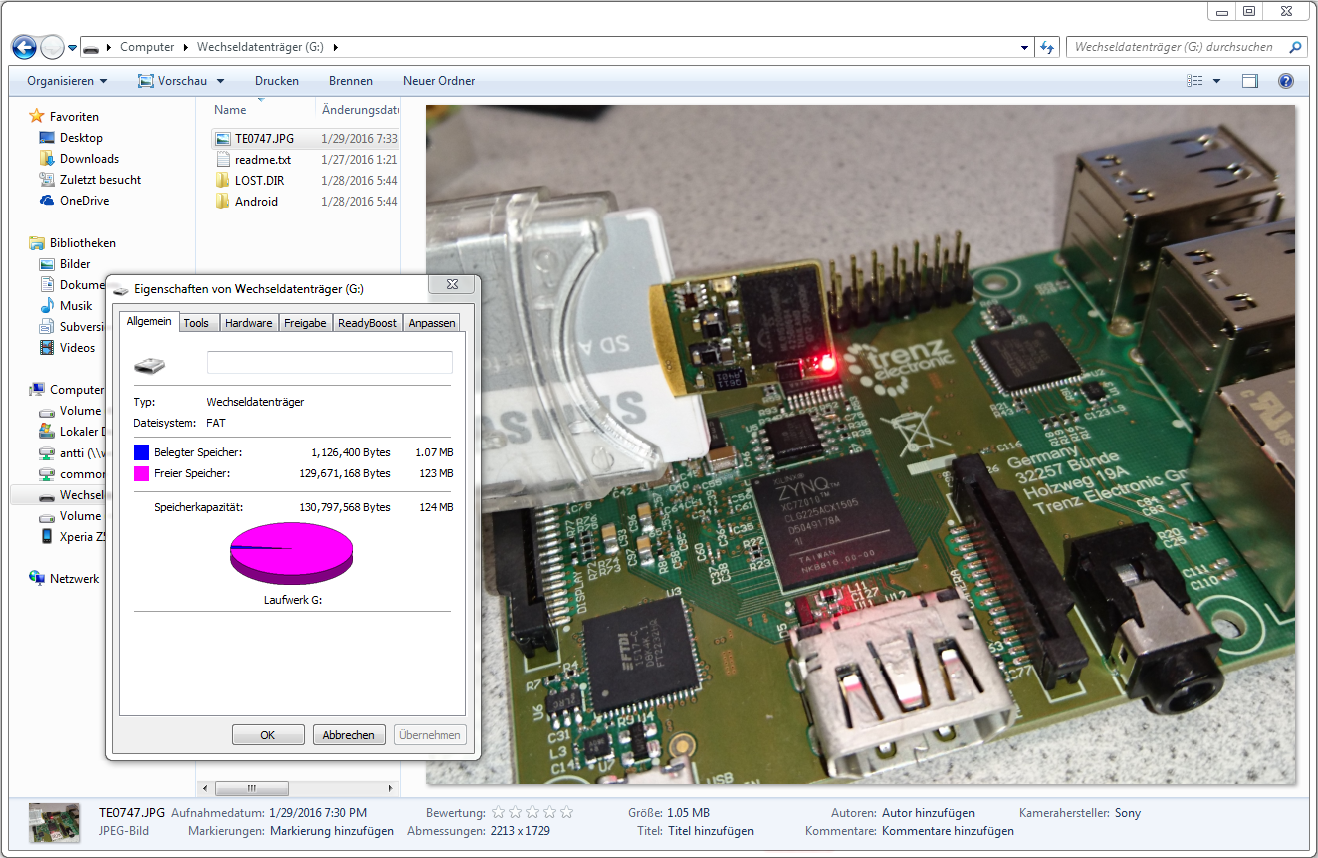

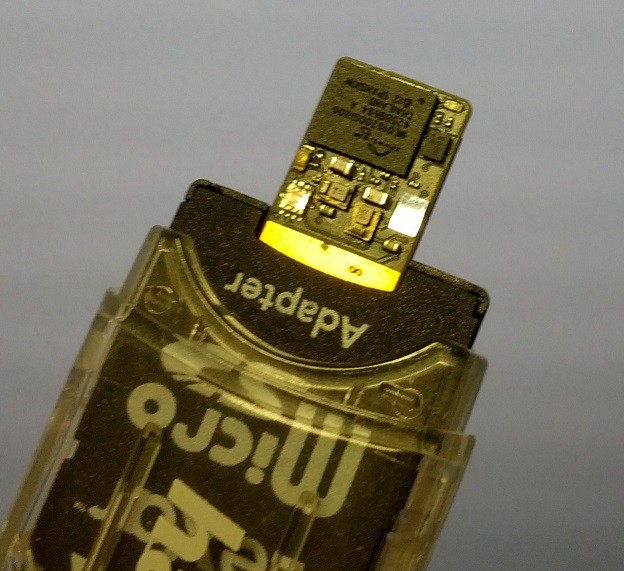

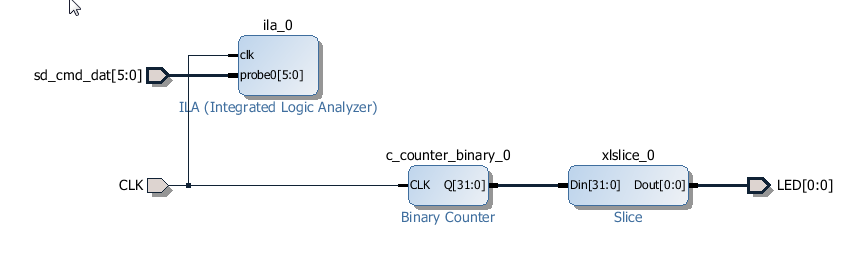

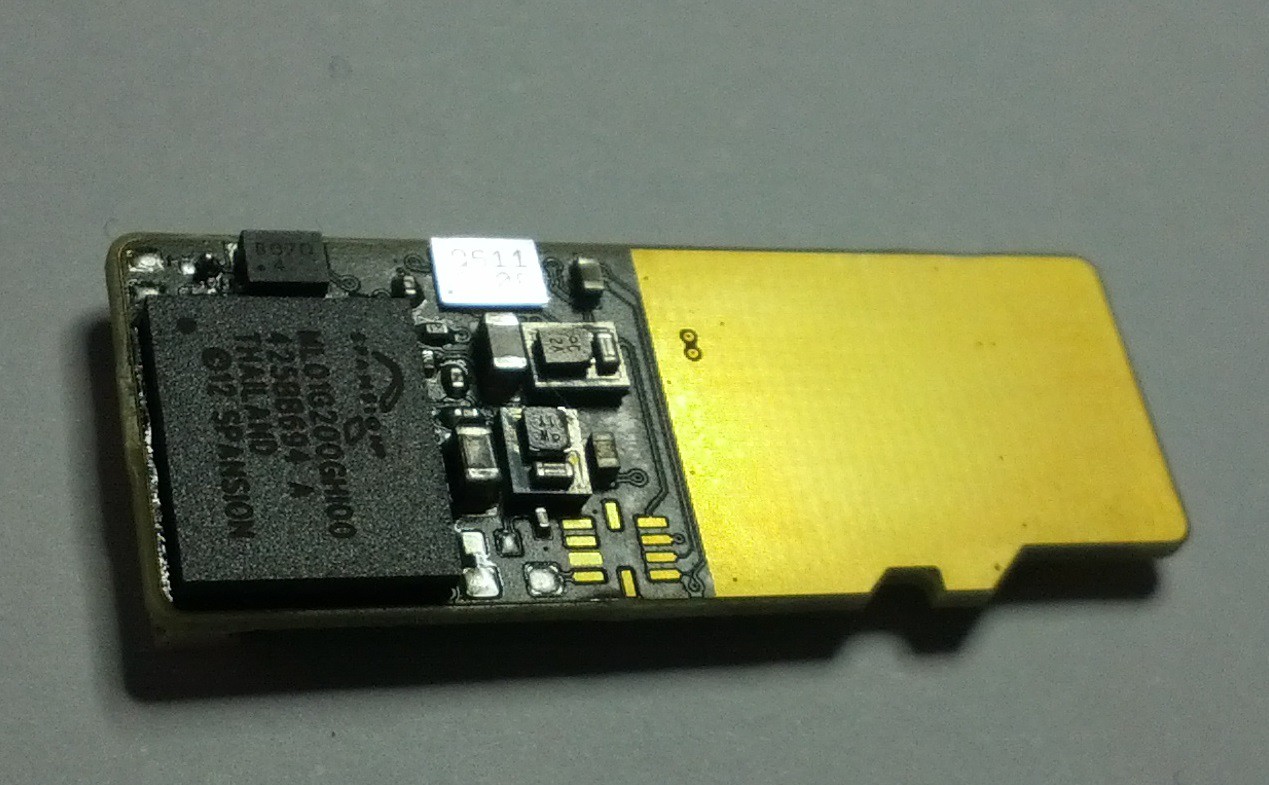

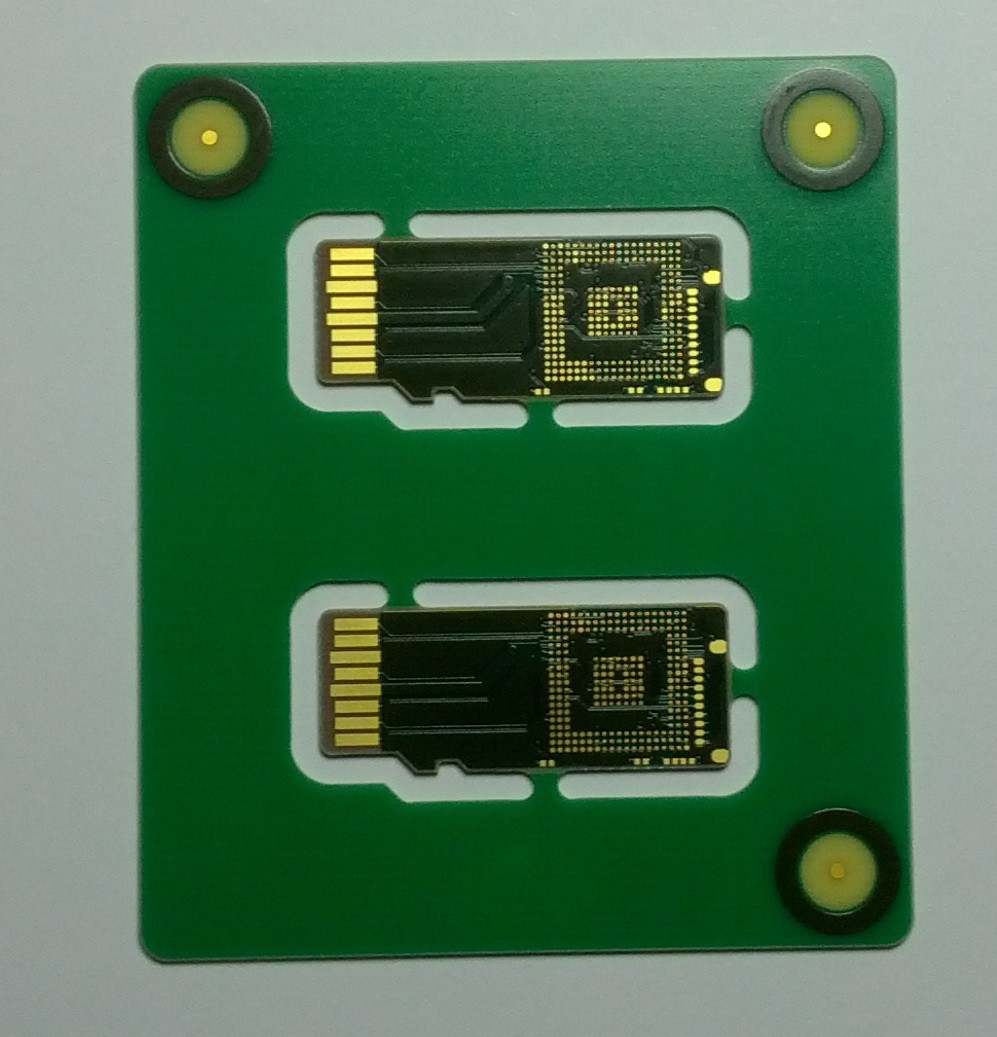

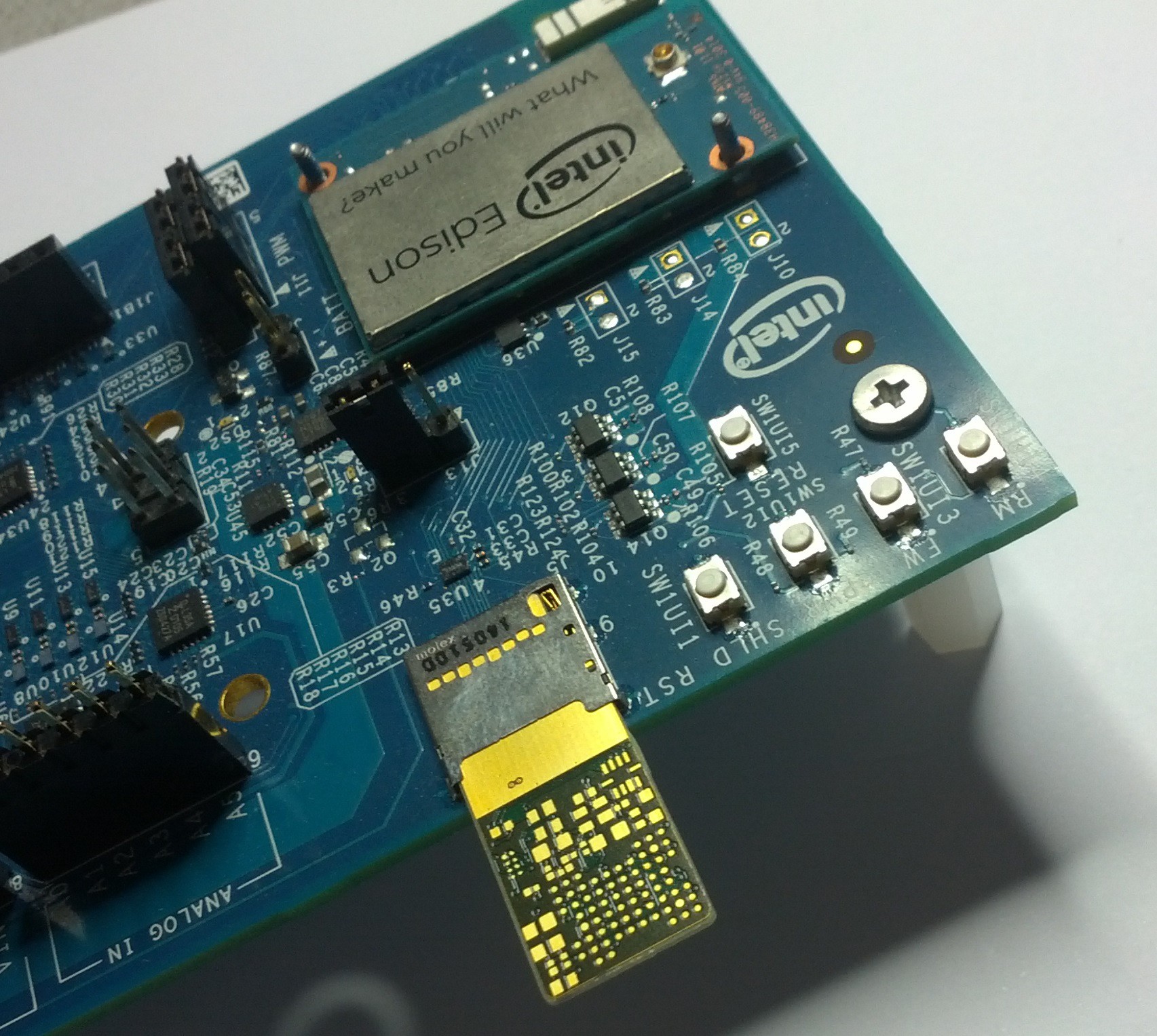

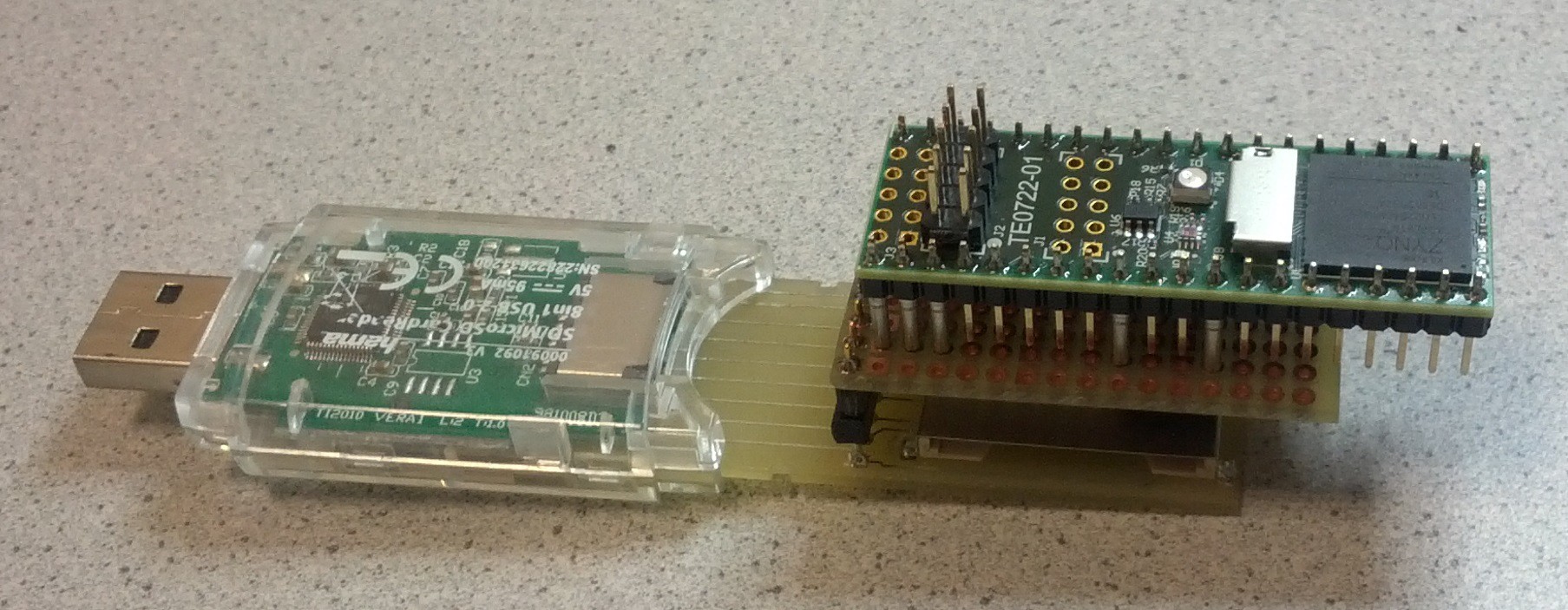

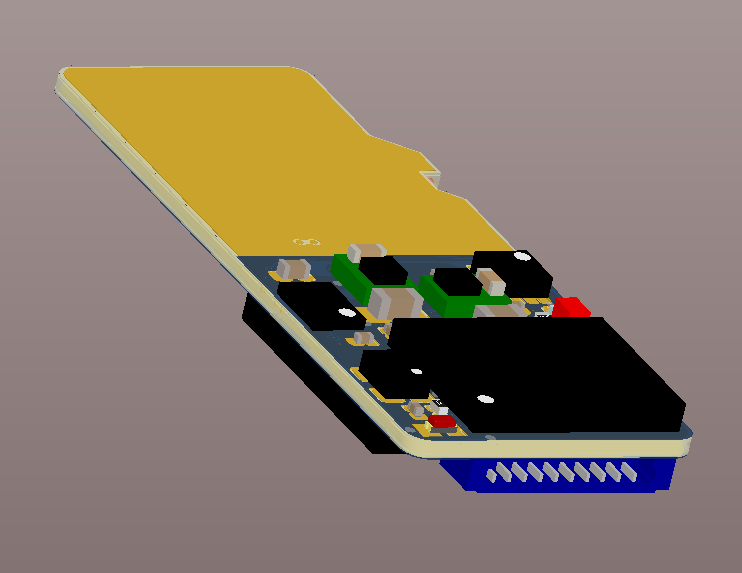

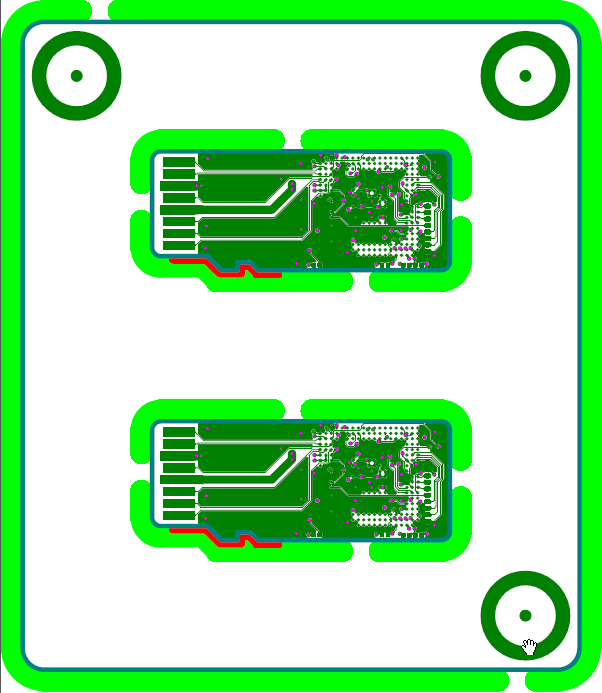

Fits into Micro-SD slot, 4 Layer PCB, Xilinx Artix FPGA A15T to A50T, Murata DCDC Regulators, SiTime MEMS oscillator, 2MByte Micron SPI Flash, NAND Flash, one LED, ambient light sensor, 10 pin extension header with 4 I/O's and JTAG (JTAG pins can be used as 3 input only pins),

Designed to run google geophyte HDL

Licenses

- CERN OHL

- Hardware design

Antti Lukats

Antti Lukats

Ziv Barcesat

Ziv Barcesat

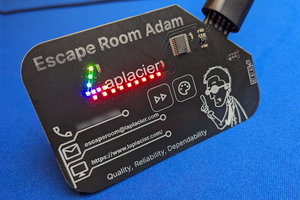

Adam Billingsley

Adam Billingsley

It looks like you have a 22µF ceramic capacitor. Considering that the capacitance of an MLCC will decrease with voltage applied, it is only a fraction of the 100µF recommended in the 7 Series FPGAs PCB Design Guide (UG483). How did you know it was enough?