This continues the previous log P5A: the ALU/Execution Units board and the operands

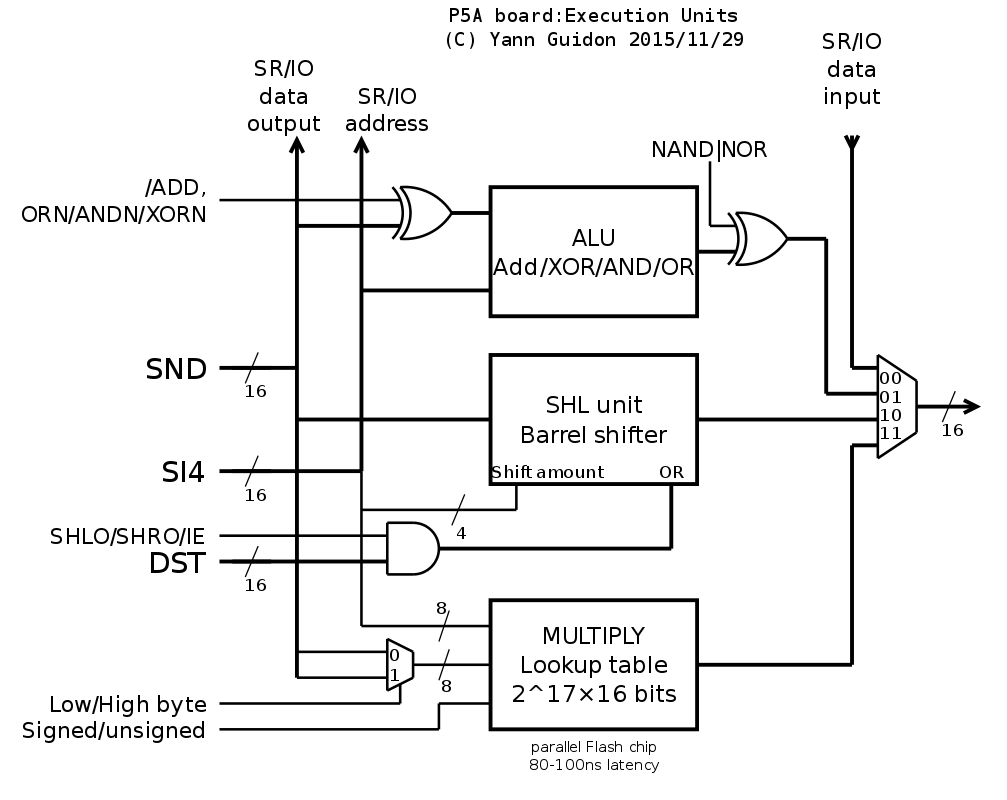

Once the 2 operands are selected and latched, the Execution Units can work. This YASEP has 3 EUs:

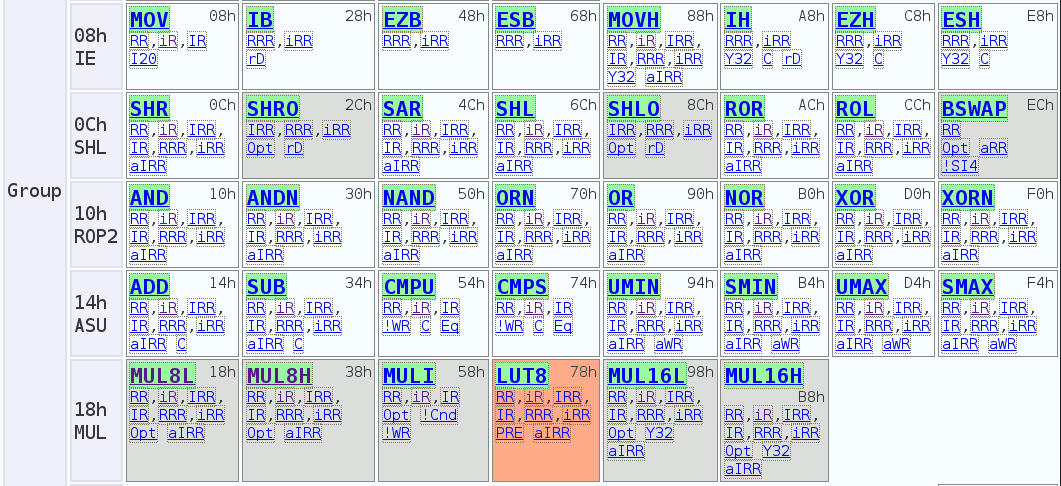

- ASU does all the ADD/SUB and ROP2 instruction groups: ADD, SUB, CMPU/S, UMIN, UMAX, SMIN, SMAX, as well as AND, ANDN, NAND, OR, ORN, NOR, XOR, XORN

- The SHL unit performs bit shuffling (see previous logs) such as SHL, SHR, ROL, ROR with optionnal OR for bitfield insertion/extraction. It is also suitable for some Insert/Extract instructions (MOV, IB, EZB). ESB (Extract Signed Byte) requires a little bit more logic.

- The MUL unit is simply a multiply table in this implementation, stored in a 128K×16bits Flash memory. Signed and unsigned results are stored. A MUX2 at the input saves some instructions when computing larger numbers.

Overall, these 3 units perform most of the defined opcodes:

The P5A board has another distinctive feature: this is where you plug all the extensions, including SR (Special Registers) or IO (external memory, peripherals...). A MUX4 steers all those data to the output (8× 74HC253 with tristate output)

Yann Guidon / YGDES

Yann Guidon / YGDES

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.