32 bit MIPS CPU

A five stage CPU core based on the MIPS instruction set

A five stage CPU core based on the MIPS instruction set

To make the experience fit your profile, pick a username and tell us what interests you.

We found and based on your interests.

lambdaCPU v4.circProcessor file, requires installation of logism to work.- 412.75 kB - 07/10/2016 at 03:54 |

|

|

lambdaCPU instructionset.xlsxI used this to design the instruction decoder, useful if you want to write codesheet - 10.28 kB - 02/21/2016 at 21:34 |

|

|

lambdaCPU code.txtNotes for code (for reference only, may have errors, so if you want to run one of the programs, load it from the looptest.txt or hilotest.txt files)plain - 1.32 kB - 02/21/2016 at 21:18 |

|

|

lambdaCPU looptest.txtCode that tests the branch prediction (only backwards); right click on ROM labeled "program" in logisim, select load image, and choose this file to run the program. To change value that code counts to, change the lower two bytes of the first instruction to the desired value.plain - 52.00 bytes - 02/21/2016 at 21:16 |

|

|

lambdaCPU hilotest.txtCode that tests the accumulator registers; right click on ROM labeled "program" in logisim, select load image, and choose this file to run the program.plain - 102.00 bytes - 02/21/2016 at 21:15 |

|

Debugging

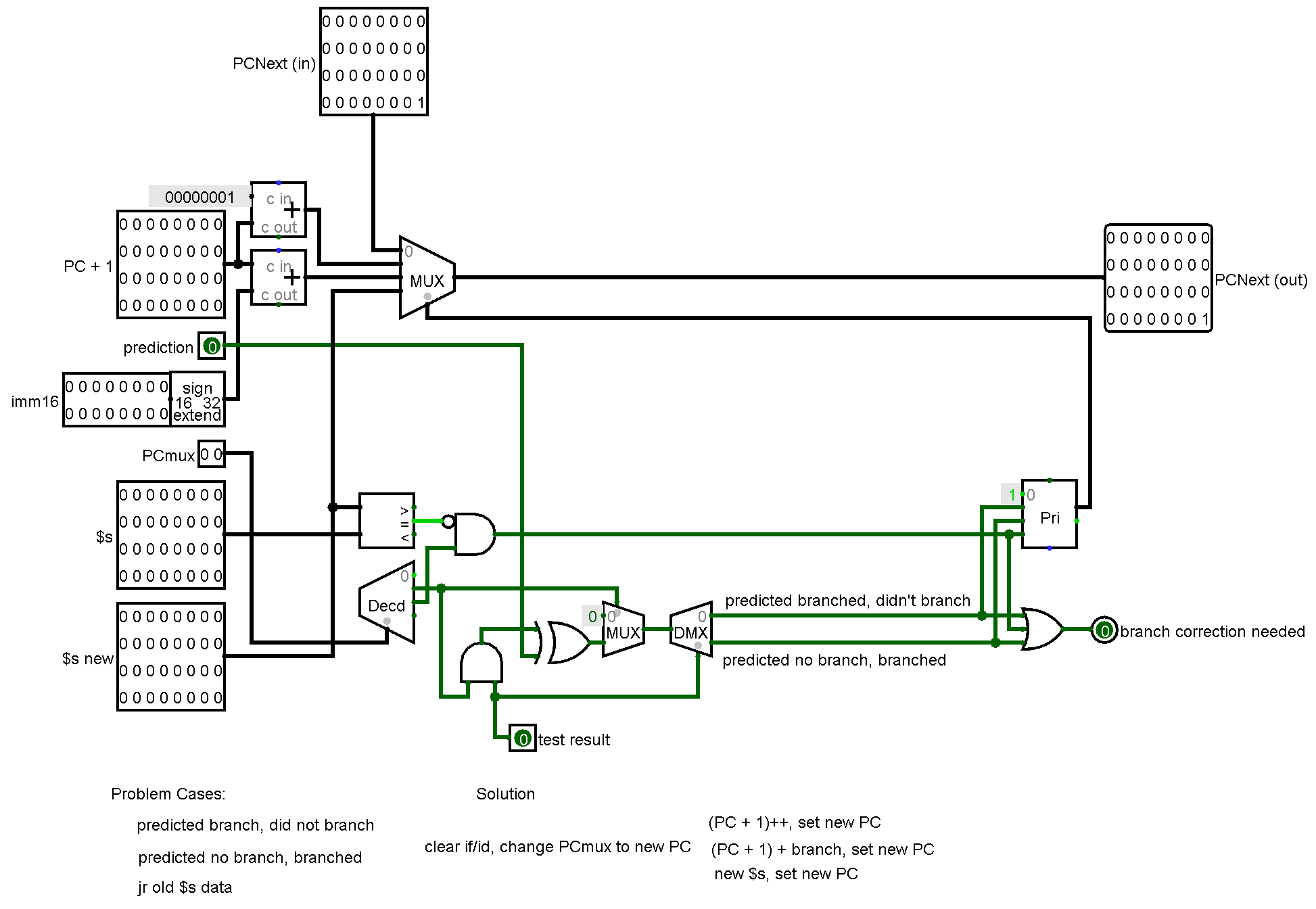

As I was running some test code, I discovered that stale register data was being used to execute the jump register instruction. The fix for this was simple; I added a "new $s" signal from the forwarding registers to the branch correction. In addition, I also tidied up and simplified the branch correction.

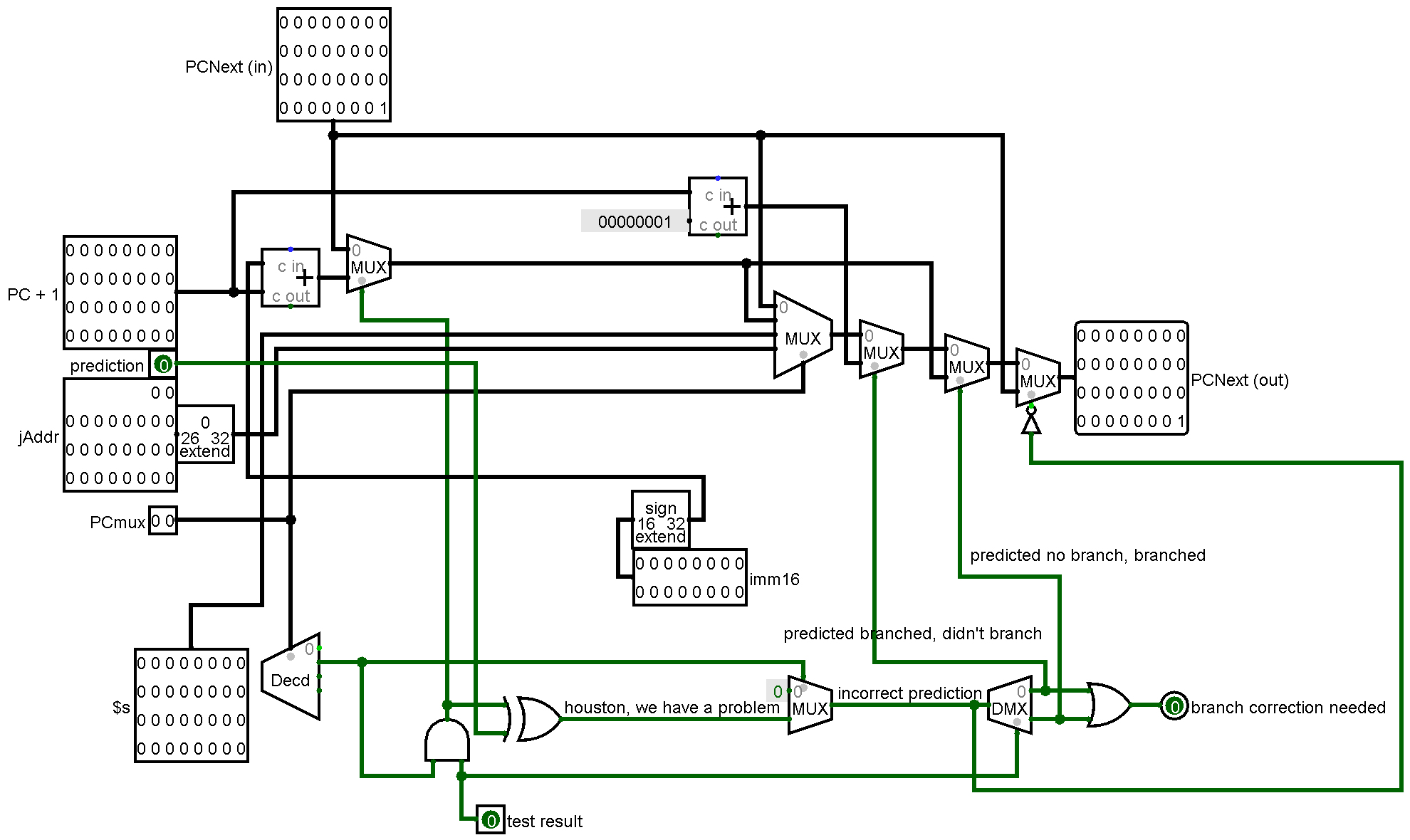

Old Branch Correction

New Branch Correction

This simplified design is not only easier to understand, but it is also faster because there is no longer a chain of multiplexers that the "PCNext" signal has to propagate through.

Create an account to leave a comment. Already have an account? Log In.

Become a member to follow this project and never miss any updates