-

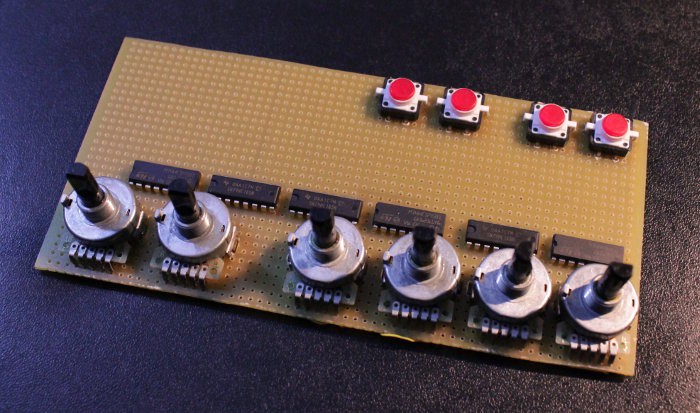

The (semi-aborted) front panel

05/01/2016 at 18:13 • 0 commentsI recently started hacking a control interface for the system but is soon got out of hand. For example, I thought that I could get the whole thing, (buttons, ALU, display and dividers) on the same pretty narrow board.

It turns out, I can't really. I added a "bypass" system with '165 and '595 shift registers to read the buttons, and override their value, to provide external control (and debouncing, or even smooth fading) and there is not even a TIL311 or #DYPLED in sight.

So I moved the frequency/signal processing to another board behind it.

Then, other projects happened.

Anyway, I'm now having a pretty cool clock source and some PLLs so the story is not over. Yet.

-

Alternatives

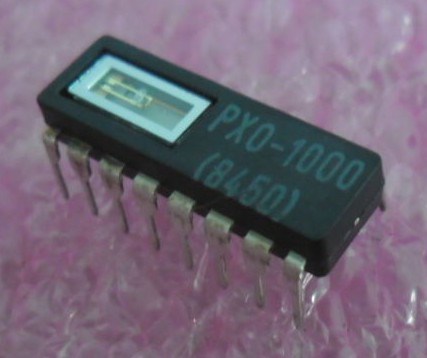

04/25/2016 at 19:46 • 7 commentsI just discovered this chip : the STATEK PXO-1000 integrated quartz oscillator with integrated predividers.

http://pdf.datasheetarchive.com/datasheetsmain/Datasheets-8/DSA-154595.pdf

Yes it's pretty practical to hack a tiny frequency generator with a minimum part count. I ordered a few of these antiques that don't seem to grow old.

Of course "I could do this with a PIC" but the total absence of programming is worth it :-)

In the same vein, after a hint from @K.C. Lee, I got myself a bunch of PLLs.

Actually it's called a "zero-delay clock buffer" with 8 outputs but the CYPRESS CY2308SC-4 also works as a frequency doubler that can output between 10MHz and 133MHz.

By playing with the feedback signal, not only I can smooth the signal (reducing the jitter) but also bring the frequency much higher. I expect my Rb source to output 20MHz, which will be halved by the ALU, but I can reach up to 120MHz :-)

Another discovery from http://www.jmargolin.com/vgens/vgens.htm :

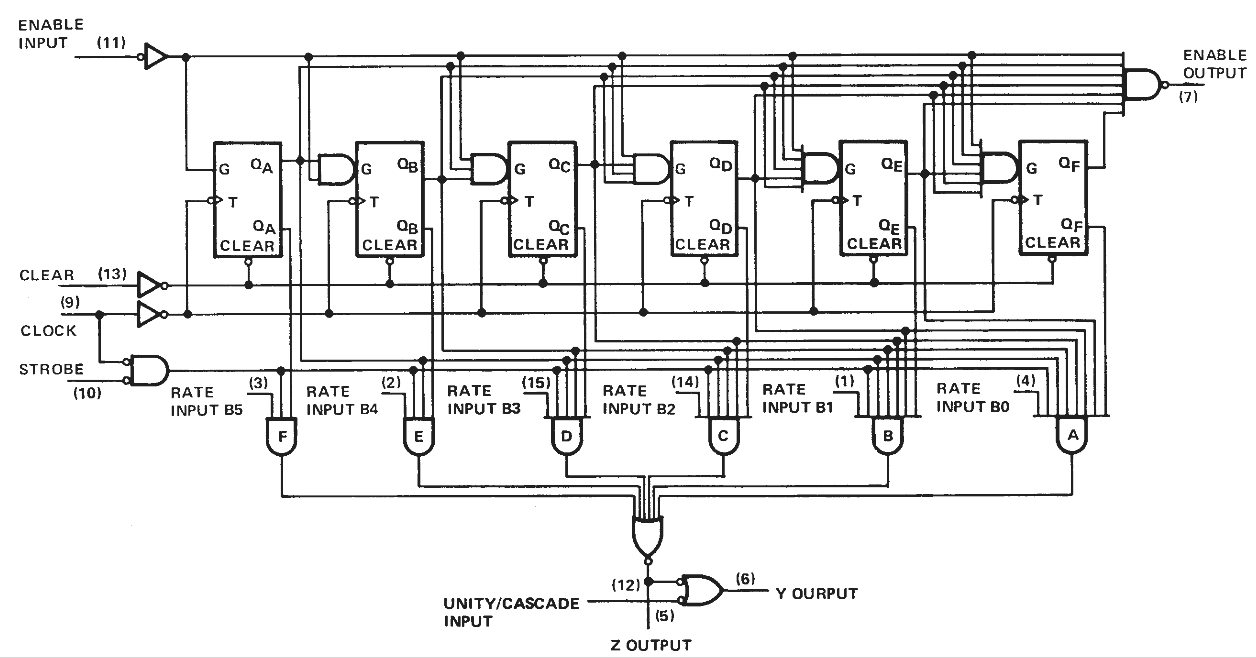

"The BRM used by Atari was the 7497. The 7497 is a 6-bit BRM. With a digital input of 63, it will produce 63 output pulses for every 64 input clocks. With a digital input of 1 it will produce one output pulse every 64 input clocks. Two 7497s were chained together to produce a 12-bit BRM. The data sheet for the 7497 is available here (PDF 282KB)."

So yes there is a simpler, faster (better) way to perform the frequency division.![]()

Of course, all of this would run faster, better and take less power if I just used a A3P250.

-

Project rebirth ?

04/15/2016 at 00:00 • 0 commentsThe circus of the sub-projects continues !

I couldn't wait to complete this project and #ScoPower was hacked in one hour. So why bother anymore ?

Well, ScoPower led to #Active scope probe with no dedicated power supply and at one point I'll have to check the frequency response, so I need a frequency generator that is able to sweep though low and high frequencies.

There is a problem, though : this frequency generator can only output a square wave, up to 40MHz.

Now I have different solutions:

- get a DDS module (Nooelec has one for 15$)

- Use a FPGA to do the DDS thing, my Actel chips can go pretty high if well designed, and I can learn to control the PLL. There would be a 8-bit output (representing a sine stored in blockram) going to a fast/video DAC

- Do it the hard way with discrete parts (but it would not have the same performance)

-

Doubling the frequency

03/28/2016 at 20:39 • 4 commentsI had overlooked a little detail in my initial system analysis.

Even though the input frequency can reach 40MHz (due to the internal 25ns cycle time), the maximum possible output frequency is 40/2=20MHz, which could be better.

It is not possible to go higher with this circuit. However, with 2 parallel circuit, there must be a way... One ALU is read during the input clock low phase, the other is read during the high phase.

Mathematically it's not a problem because the system is highly linear. Since one accumulator increases its value by N at each cycle, it should advance by 2N after 2 cycles. Now if there are 2 separate accumulators, both advance by 2N. The system could be extended to even more phases (powers of 2 work best) if needed.

How would it work ?

- Accumulator A is reset to 0

- Accumulator B is reset to the advance value N

- Both advance with the value 2N (N is shifted left by 1 position, MSB is ignored, LSB is 0)

I'm sure I'm reinventing the wheel but... it's fun and doesn't cost me much. The only critical thing is to keep the accumulators in synch so they must be loaded simultaneously. Manual changes will require the push of a button (to load the A and B registers), until I automate this.

Assuming the input clock's duty cycle is 50%, A's MSB is output on the low phase and B's MSB is output on the next high phase. The output jitter would be only 12ns now :-)

I'm sure the performance, speed, consumption etc. would be much better with a FPGA (Most FPGA even have a configurable PLL) but it would be cheating :-D

-

Notes on using a pipelined ALU for frequency division

03/28/2016 at 08:08 • 0 commentsInitially, I wanted to use a 74F381 (4-bits ALU) and a 74HC574. Then I tried to extend the 4-bits add function to 8 bits but cascading is hard because there is no carry output, but propagate and generate signals. The Generate signal could be used alone when the carry input is not used but apparently it needs an inverter. From there, it went downhill.

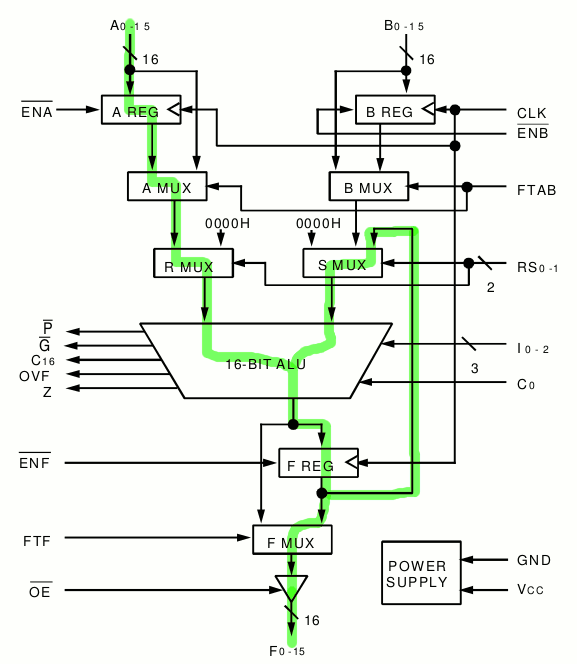

Then, looking at my notes at https://hackaday.io/project/8121-discrete-yasep/log/28438-what-chips-for-the-alu I saw that I had the ideal solution. From the datasheet :

The IDT7381 is a high-speed cascadable Arithmetic Logic Unit (ALU).

These three-bus devices have two input registers, an ultra-fast 16-bit ALU and 16-bit output register. With IDT’s high-performance CMOS technology, the IDT7381 can do arithmetic or logic operations in 25ns. The IDT7381 functionally replaces four 54/74S381 four-bit ALUs in a 68-pin package.

The two input operands, A and B, can be clocked or fed through for flexible pipelining. The F output can also be set into clocked or flow-through mode. An output enable is provided for three-state control of the output port on a bus.

The IDT7381 has three function pins to select 1 of 8 arithmetic or logic operations. The two R and S selection pins determine whether A, B, F or 0 are fed into the ALU. This ALU has carry-out, propagate and generate outputs for cascading using carry look-ahead.The advantages are pretty significant :

- only one chip is needed for all the functions (computation and latching)

- it's 16-bits wide (and not just 4 or 8 bits)

- it draws less power

- it's faster (it easily reaches 40MHz, providing a 20MHz square signal output).

- No programming is required, just set the 16-bits divider value on the A port and get the divided frequency on the MSB of the result (F15 bit).

- The remaining output bits could be used to address a fast SRAM to generate arbitrary waveforms (I would need a fast DAC, such as a RAMDAC. Oh wait: I have RAMDACs).

- Another pretty useful feature is the ability to latch the inputs. This provides a glitch-free frequency change, since my hex rotary switches are pretty dirty. From there on, it's possible to cut the connexion between the rotary switches and the port, under software control, with 74HC165 and 74HC595, to smooth the frequency changes with a microcontroller or a Pi.

The chip would be used this way :

![]()

The connexions are:

- Input B : unused, tied to GND.

- Input A : Division ratio, 16 bits coming from the rotary switches and the 74HC595.

Value 0 is detected as "bypass" value. It should be FFFF (with the carry input set) but then the digital reading would be harder to interpret. - Output : divided frequency on F15

- /ENB : pointless, tied to GND.

- /ENA : one pulse low to latch the new frequency. Tied to GND initially for manual operation, such that it is updated at every cycle.

- FTAB : GND (flow-through disabled)

- /ENF : GND (enable the F register during every cycle)

- FTF : GND (no flow-through, should reduce the jitter)

- CLK : clock input (40MHz, can it go faster ?)

- /OE : GND (enable the F port output)

- C0 : GND (Carry in. I thought about feeding a noise generator/LFSR to add jitter, let's see later)

- C16, OVF, Z, P, G : open/unconnected

- RS0, RS1 : 00 (select operands A and F)

- I0, I1, I2: 110 (addition)

It's actually pretty simple : except I0 and I1 all fixed inputs are GND :-)

Quick & Dirty Frequency Generator

Because I need it, I can and I'm cheap. So maybe I'll do.

Yann Guidon / YGDES

Yann Guidon / YGDES