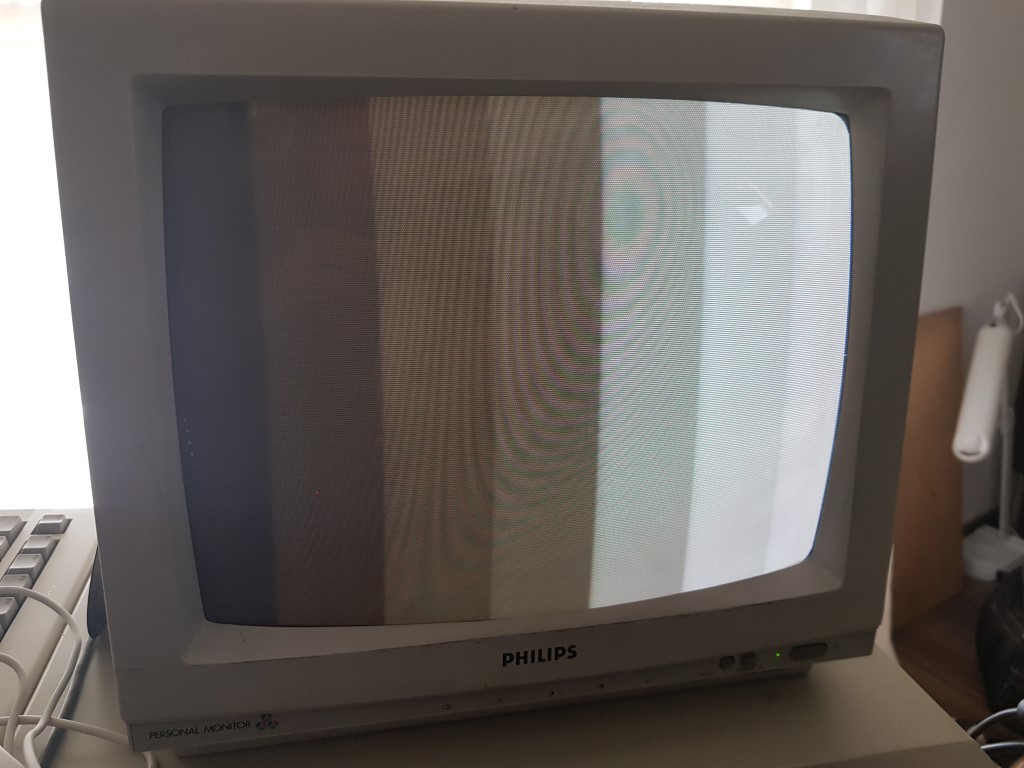

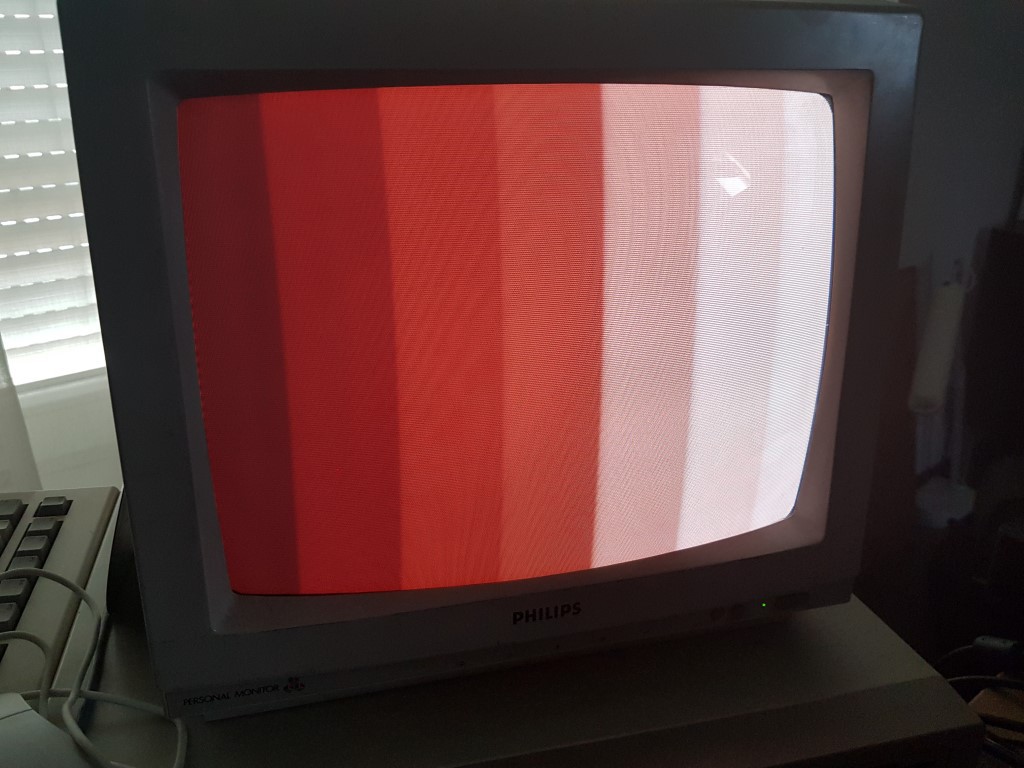

The idea of the project came when my 30 years old Commodore Plus 4 has suddenly died and I suspected that TED was the main cause. After an extensive troubleshooting it turned to be that the 8551 ACIA chip was the guilty one and I have fixed it, however by that time this project has been born in my head. I have checked the internet and was surprised that no one has created a TED FPGA core before.

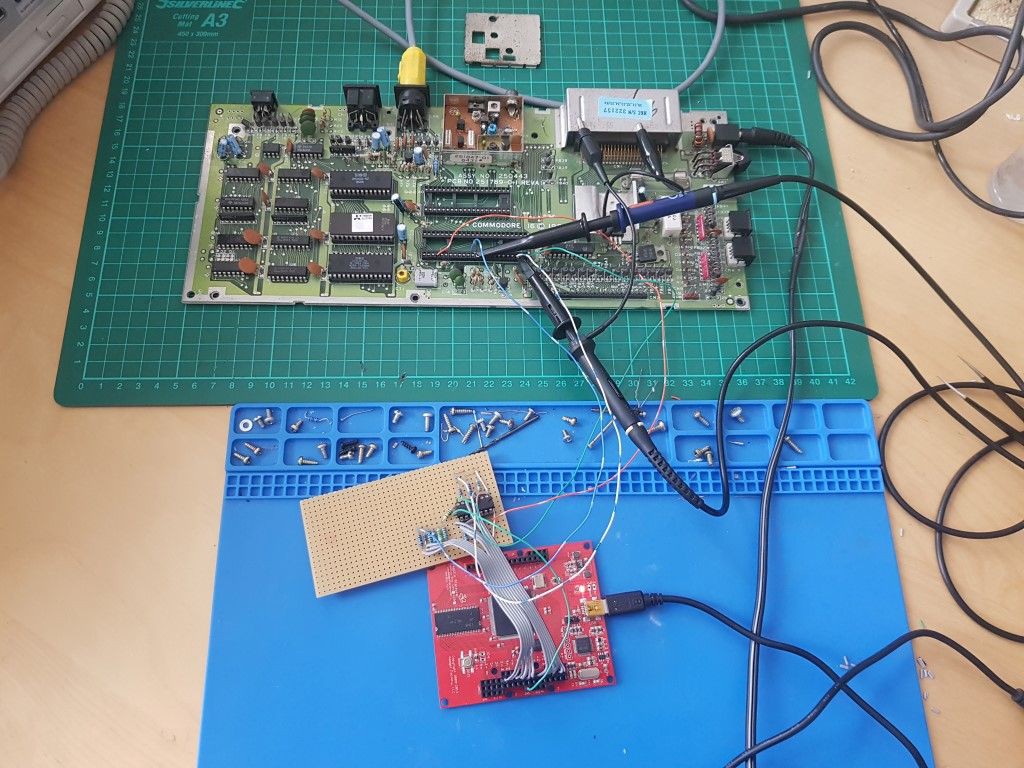

Although there are some TED documents available on the internet, they are incomplete, not precise and do not fully describe the inner secrets of the chip. There is no point in creating a chip which is not cycle exact, doesn't emulate TED scan lines and events properly. An extensive research started on the hardware using own written test codes, logic analyzer, oscilloscope and source code analysis of Plus 4 emulators. I quickly realized that due to the inner multiplexed architecture of TED certain events are initiated at the specified time (described in 7360R0 preliminary data sheet) however they happen later in time after 1-2 single clock cycles. This behavior was emulated in certain emulators like Plus4emu, which made the emulator code much more difficult to understand.

Two years of analyzing the hardware, documents and code writing has led me to a working TED chip which is capable of running most of the programs and demos the same way as the original hardware. The project is not finished though, I am planning to refine it further and make it available to everyone.

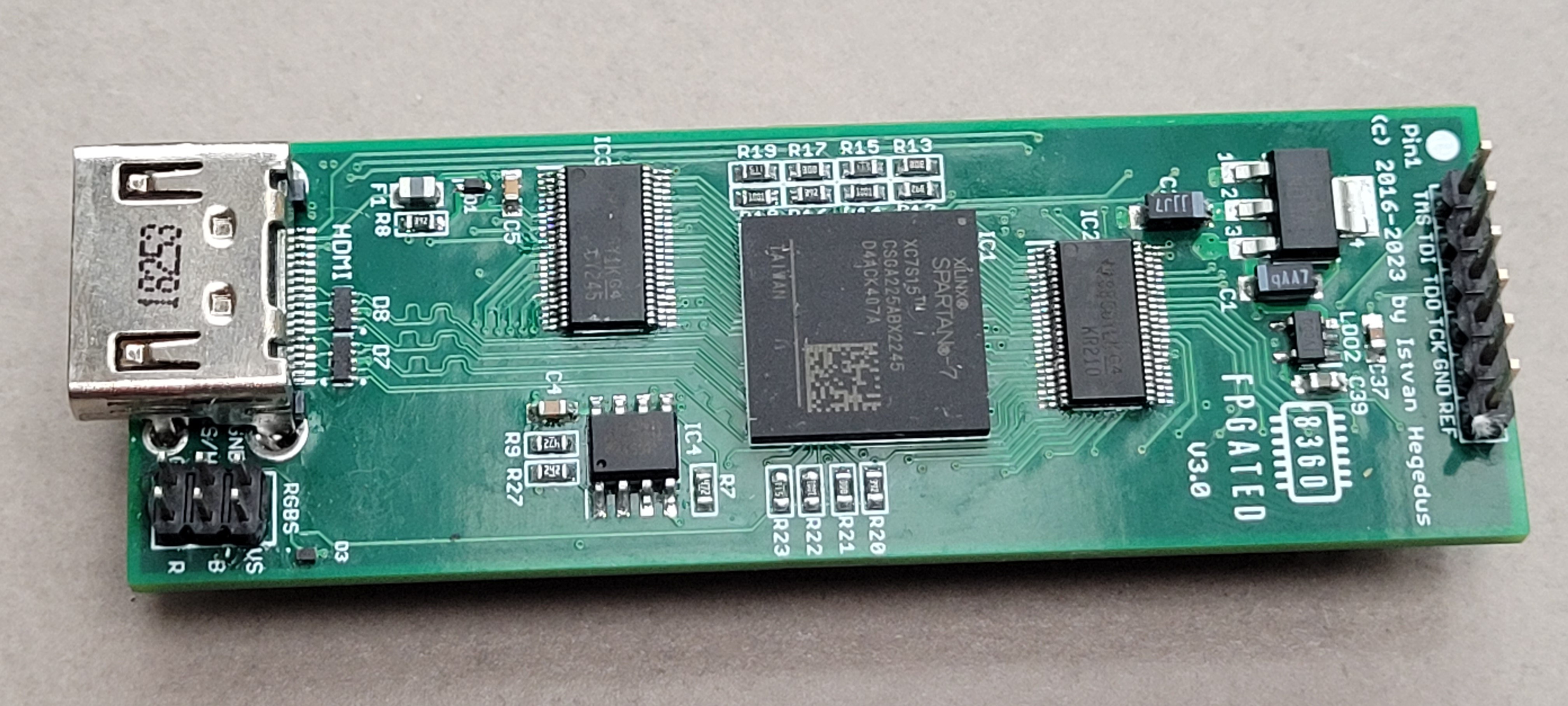

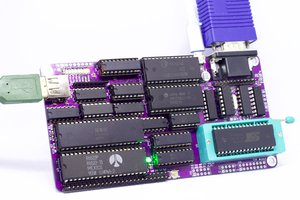

The code is written in verilog language and uses Gadget Factory's Papilio One 500k developer board. This board has a Xilinx Spartan 3E 500k FPGA which is more than enough for implementing a whole Commodore computer except its main memory. The FPGA has only about 40Kbyte RAM which is not enough for a 64Kbyte computer especially if we think of the 16K Kernal and Basic ROMs. The TED core module doesn't use any Xilinx specific HW blocks or macros so it is very easy to reuse on other Vendor's FPGAs. Later on I have continued the development on the more advanced Papilio Pro board with Spartan6A FPGA and onboard sdram. Although I wanted to implement the TED chip , it was clear that I need to implement other supporting components (CPU, ROM, keyboard matrix) to test the chip on the FPGA board. As several 6502 CPU FPGA codes exists I did not want to reinvent the wheel and decided to use a publicly available one which has illegal opcode implementation also. I have chosen Peter Wendrich's 6502 vhdl code from the fpga64 project. Peter has confirmed via email that I can use the CPU part of his code for my FPGATED project and include its source in FPGATED sources.

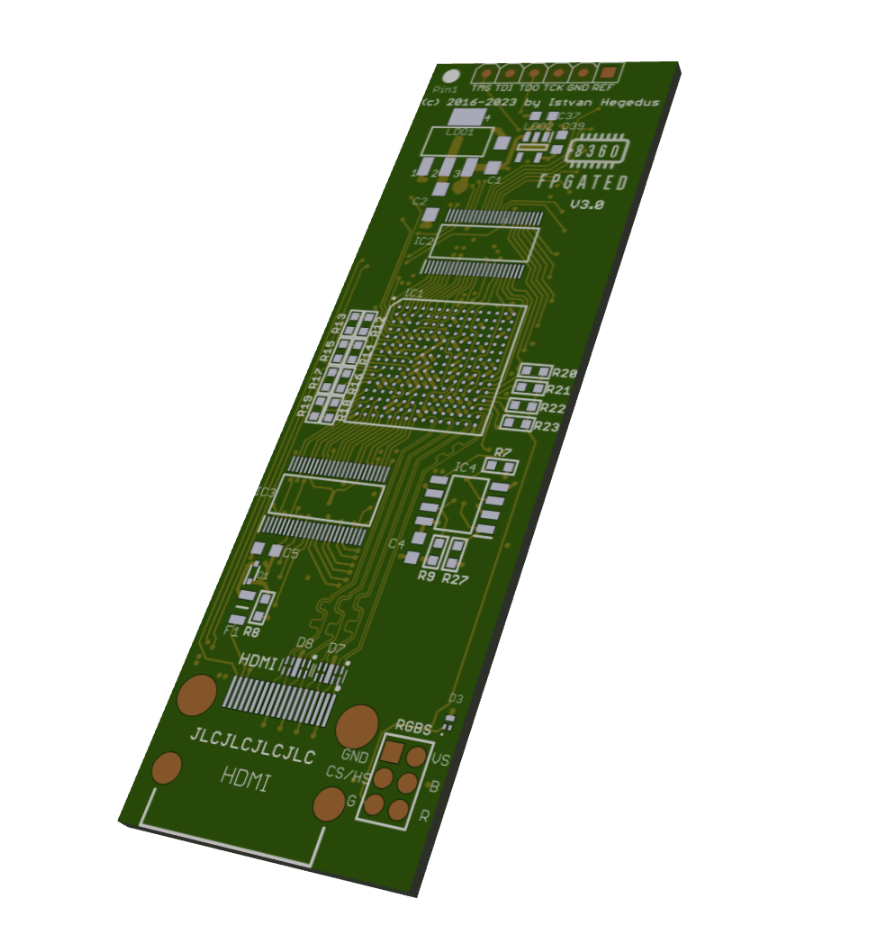

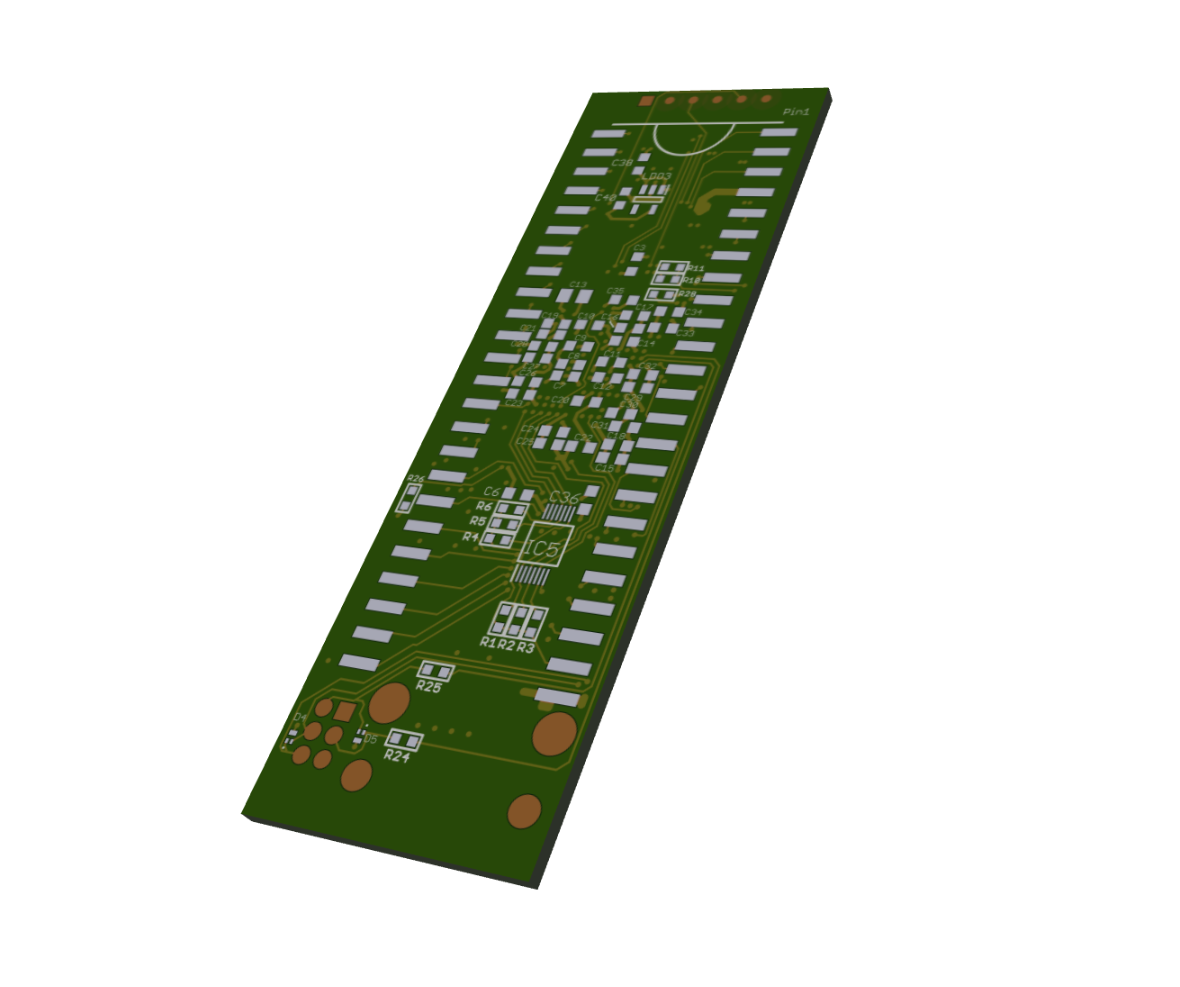

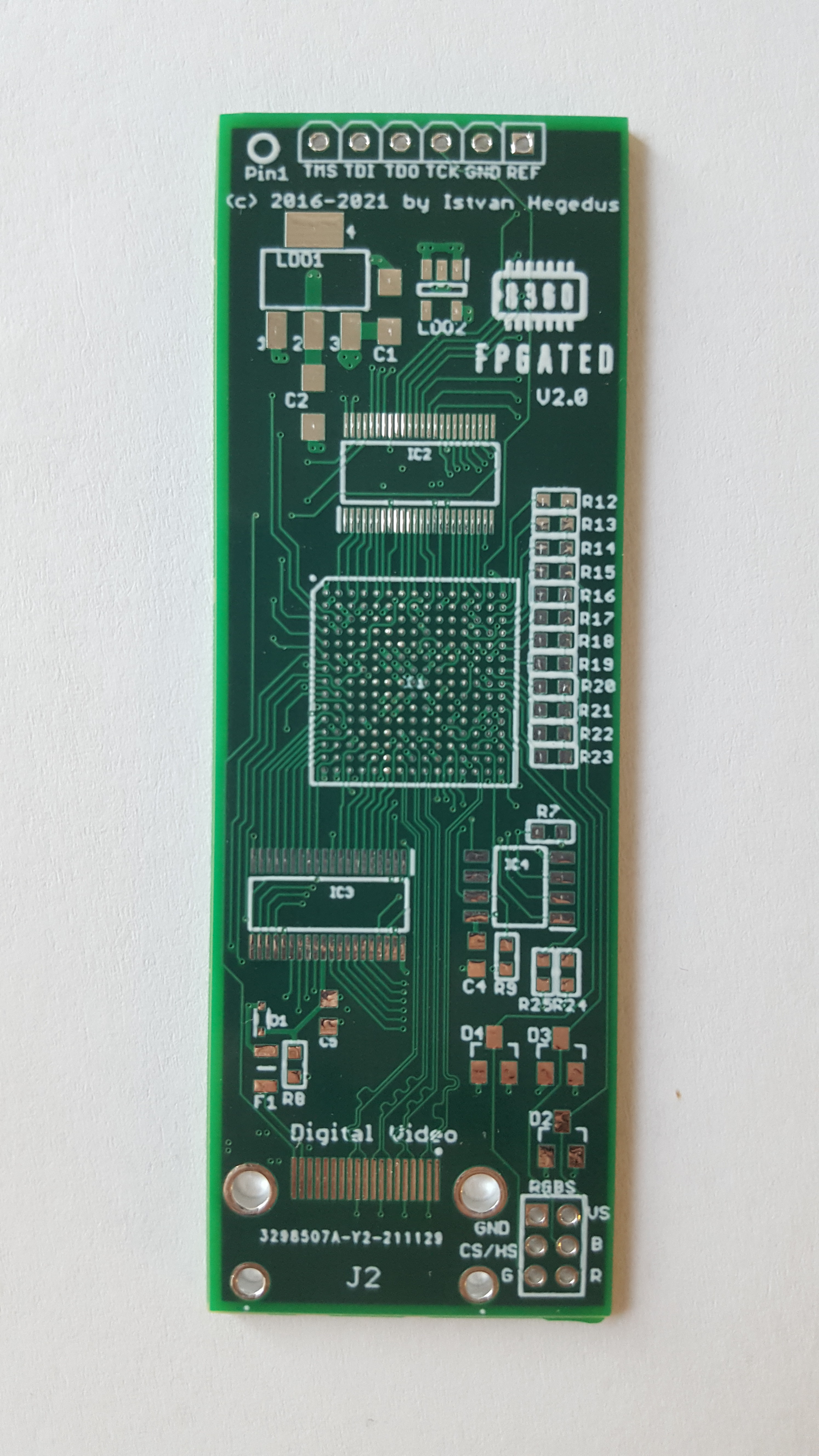

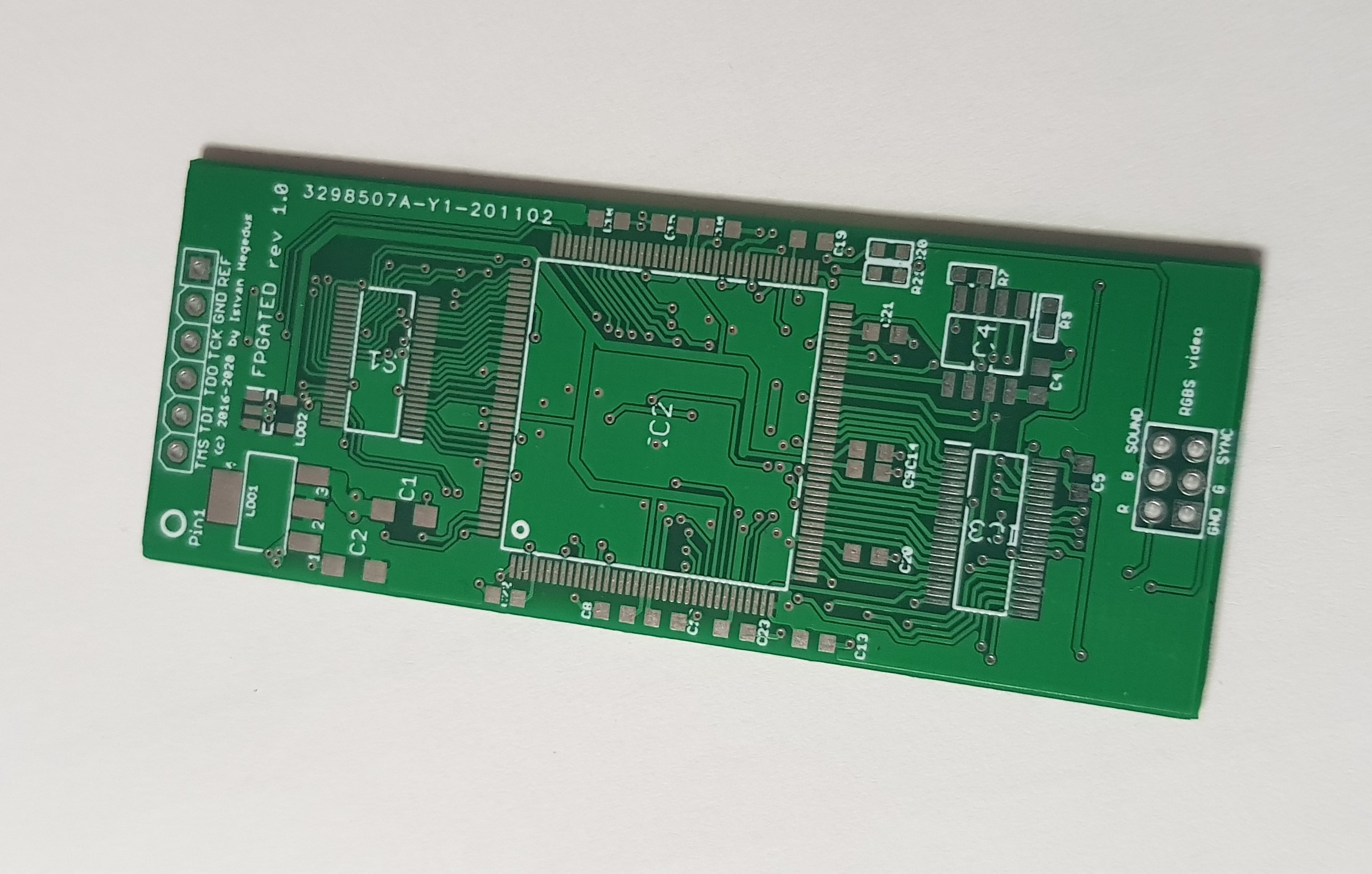

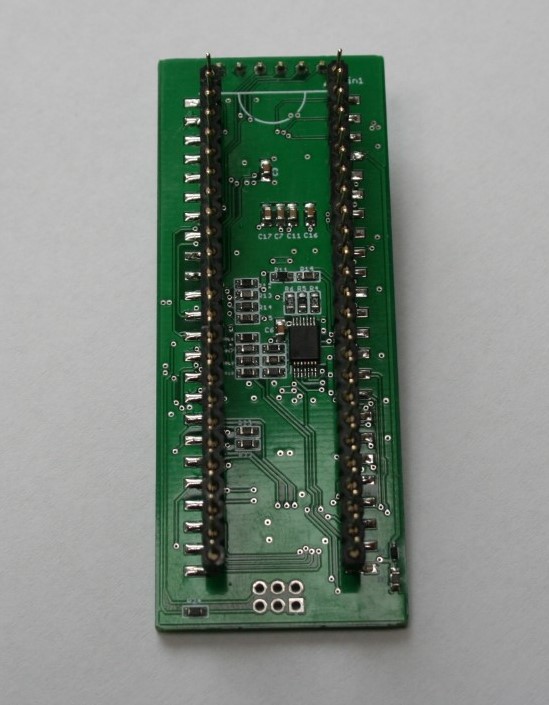

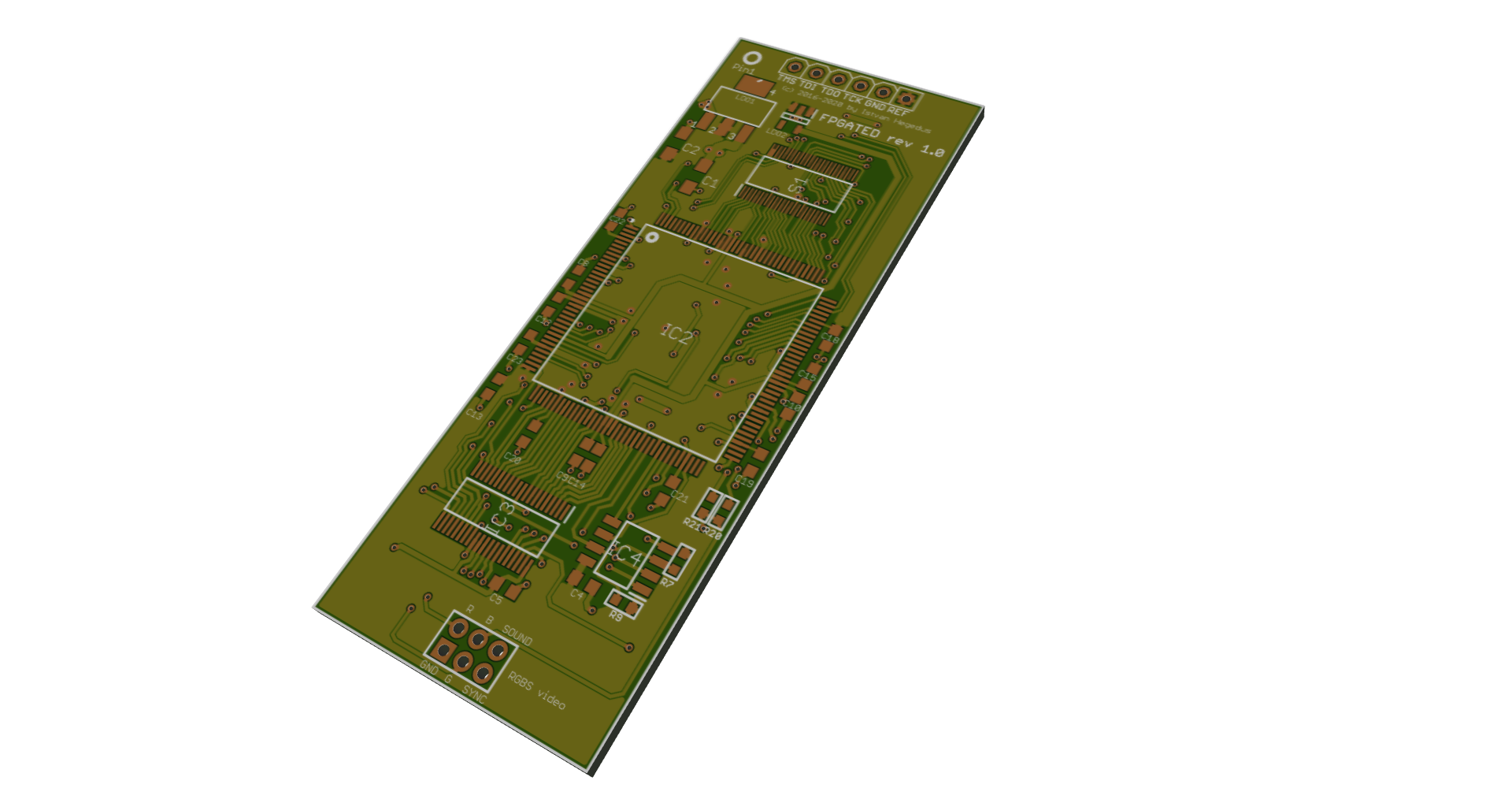

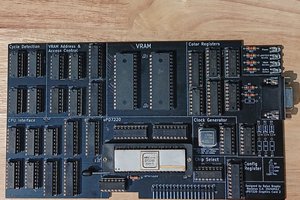

Papilio TEDwing

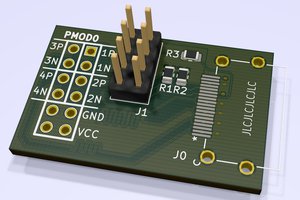

First step of the project was to create the hardware developer environment, which means building a suitable wing board for the Papilio One FPGA board. Gadget Factory has already created an Arcade Megawing however it lacks the memory part which is crucial from the TED system's point of view. It was however a good starting point for the TEDwing design. These were the main design criteria for the Papilio TEDwing:

- 12 bit VGA/RGBS output

- 2x 4464 DRAMs

- IEC serial bus connector

- PS2 keyboard connector

- Stereo audio out with low pass filter

- RS232 serial output

- Reset button

- Jumper to configure VGA or RGBS mode

The board schematic was inspired by the following other designs

- VGA, audio and PS2 part from Papilio Arcade Megawing

- IEC serial bus from SD2IEC design

- DRAM from Quickswitch QS3 voltage level translation application note AN-11A

- RS232 from MAX232 application notes

I have used Eagle 6.2 to create board schematic and layout. Size of the board fits to the limitation of Eagle free edition. All traces of the PCB was manually routed by me then sent for manufacturing. SMD soldering of components were done by me without hot air gun.

The above mentioned features fully utilize free Papilio I/O ports so there is no space left for joystick connections or user port. This is a small drawback however the original goal was...

Read more » István Hegedűs

István Hegedűs

Anders Nielsen

Anders Nielsen

Wenting Zhang

Wenting Zhang

Dylan Brophy

Dylan Brophy

For those who are waiting for the HW. I am working on the production of the 1st batch and will let you know when they are ready and purchaseable. Plan is to have them still this year. Note that 1st batch is limited amount (20 pieces).