Interpret Up and Running

Some social duties have intervened on my TTA8 work. Today was the first opportunity to spend time on the project.

The Interpreter is now working but it is much bigger (slower) than expected.

Here is the simple version:

INTERP IP SAVE IP POINTER IP INC IC REGP _1 REGQ ADD IP _246 ^POINTER JMP

Here is the Paged version:

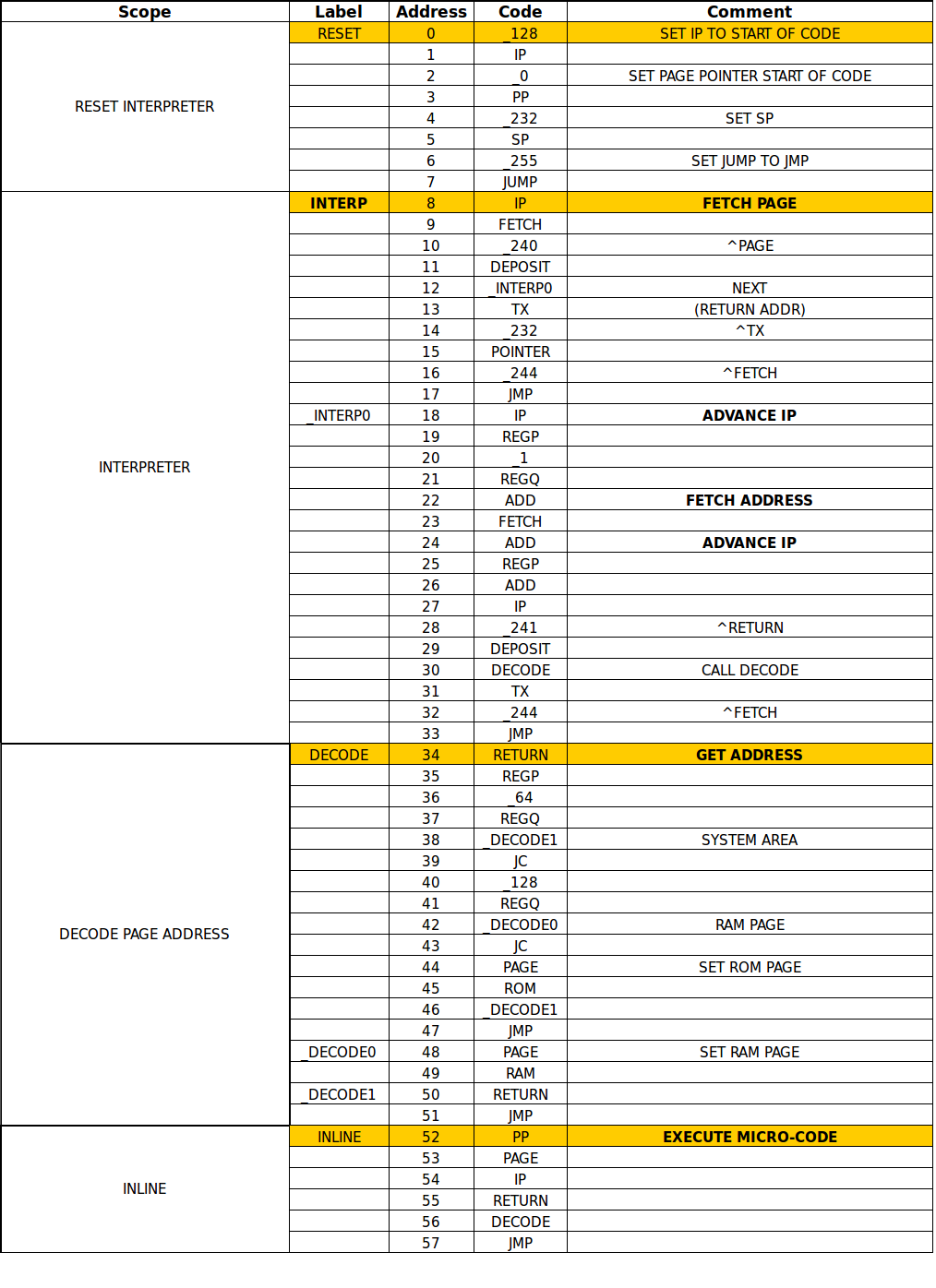

INTERP 8 IP FETCH PAGE 9 FETCH 10 _240 ^PAGE 11 DEPOSIT 12 _INT0 NEXT 13 TX (RETURN ADDR) 14 _232 ^TX 15 POINTER 16 _244 ^FETCH 17 JMP _INT0 18 IP ADVANCE IP 19 REGP 20 _1 21 REGQ 22 ADD FETCH ADDRESS 23 FETCH 24 ADD ADVANCE IP 25 REGP 26 ADD 27 IP 28 _241 ^RETURN 29 DEPOSIT 30 _INT1 NEXT 31 TX 32 _244 ^FETCH 33 JMP _INT1 34 DECODE CALL DECODE 35 JMP

Note the Paged Interpreter also calls Decode.

The Counter Program

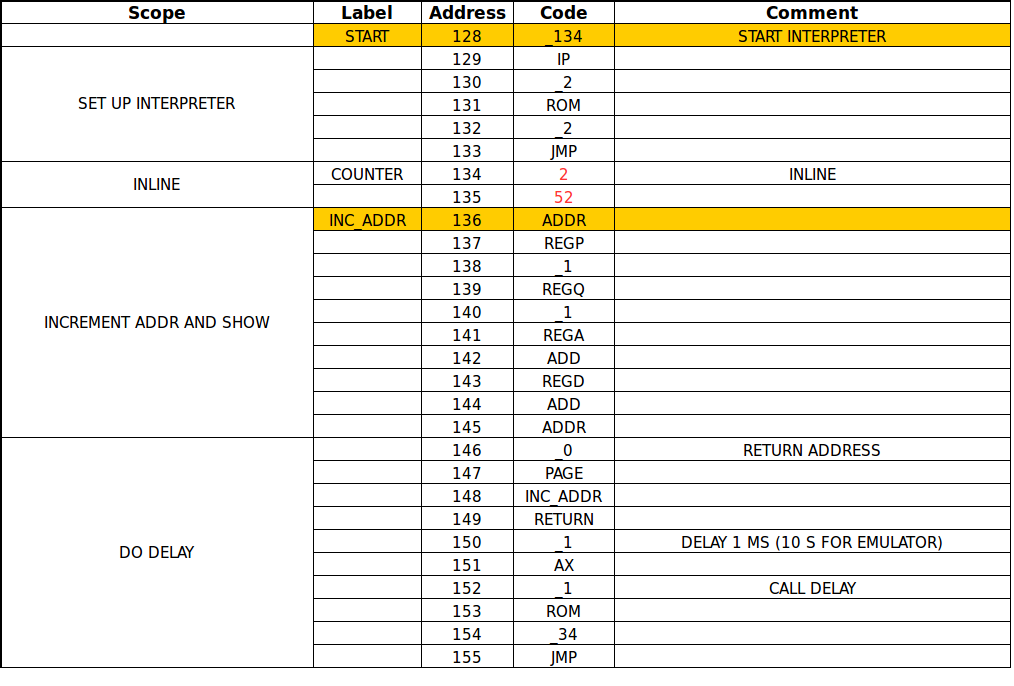

The counter progrm first sets up the Interpreter and only uses Inline (to revert bck to Machine Code):

Here is the Interpreter (including Inline and Decode):

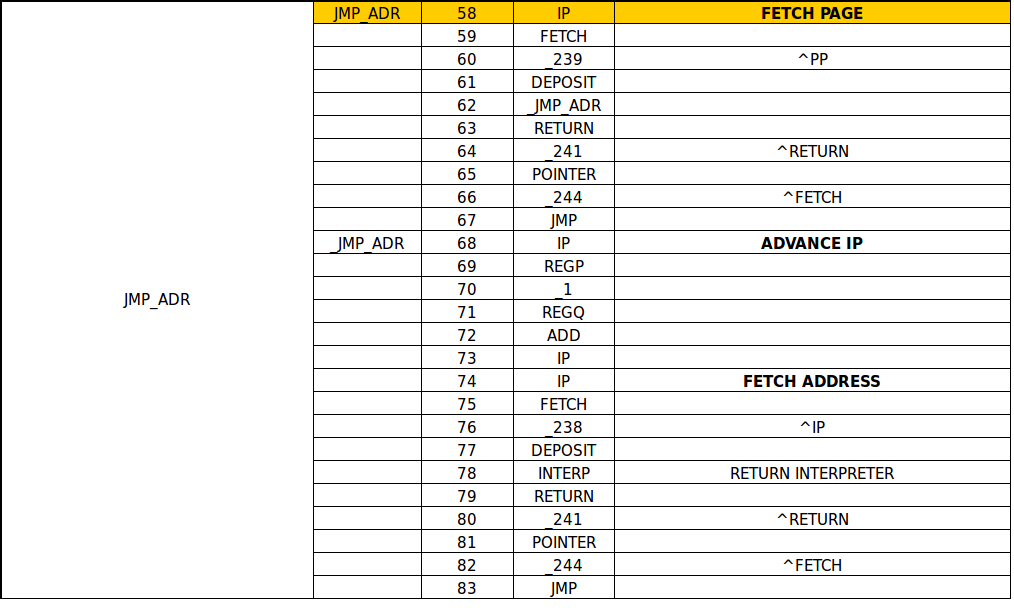

The next Interpreter instruction to write is "JMP_ADR". This will allow jumps to other pages (i.e. it sets the current Interpreter page (PP) and address (IP)). Well actually it has been written just not tested:

AlanX

agp.cooper

agp.cooper

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.