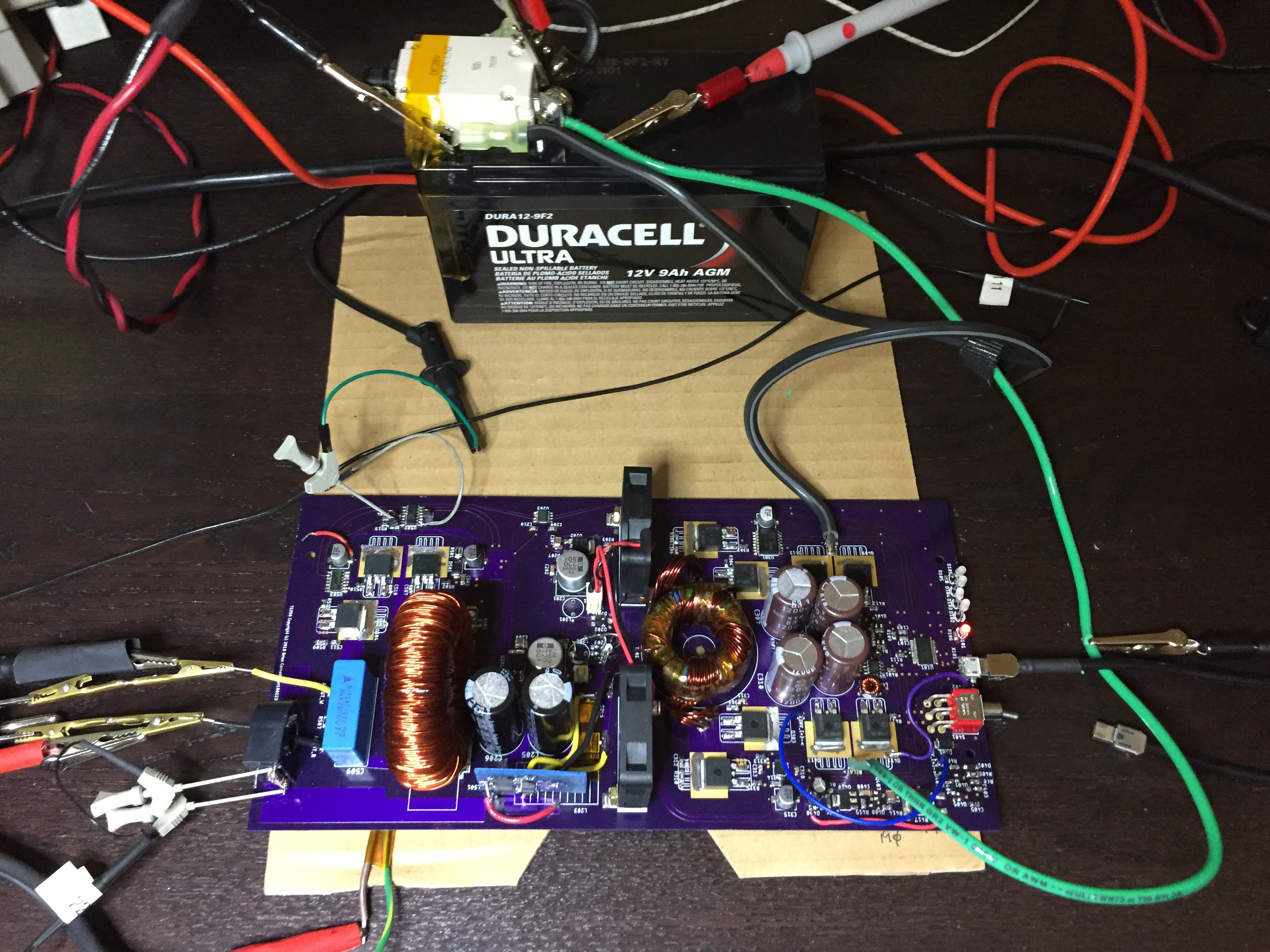

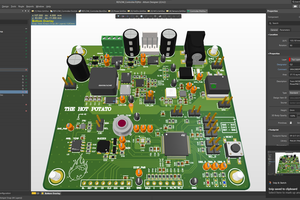

I first mentioned the TS350 in the TS50 project and that it represented the culmination of prior R&D. I had expected that it would probably go thru a few iterations to work out all the bugs but that on the whole it would be a working design. I had to rethink my definition of ‘working’. I’ve been at it now for two months and have a path forward for a redesign so,I figured this was a good time to start the project write-up. For background & context read about the TS50 first.

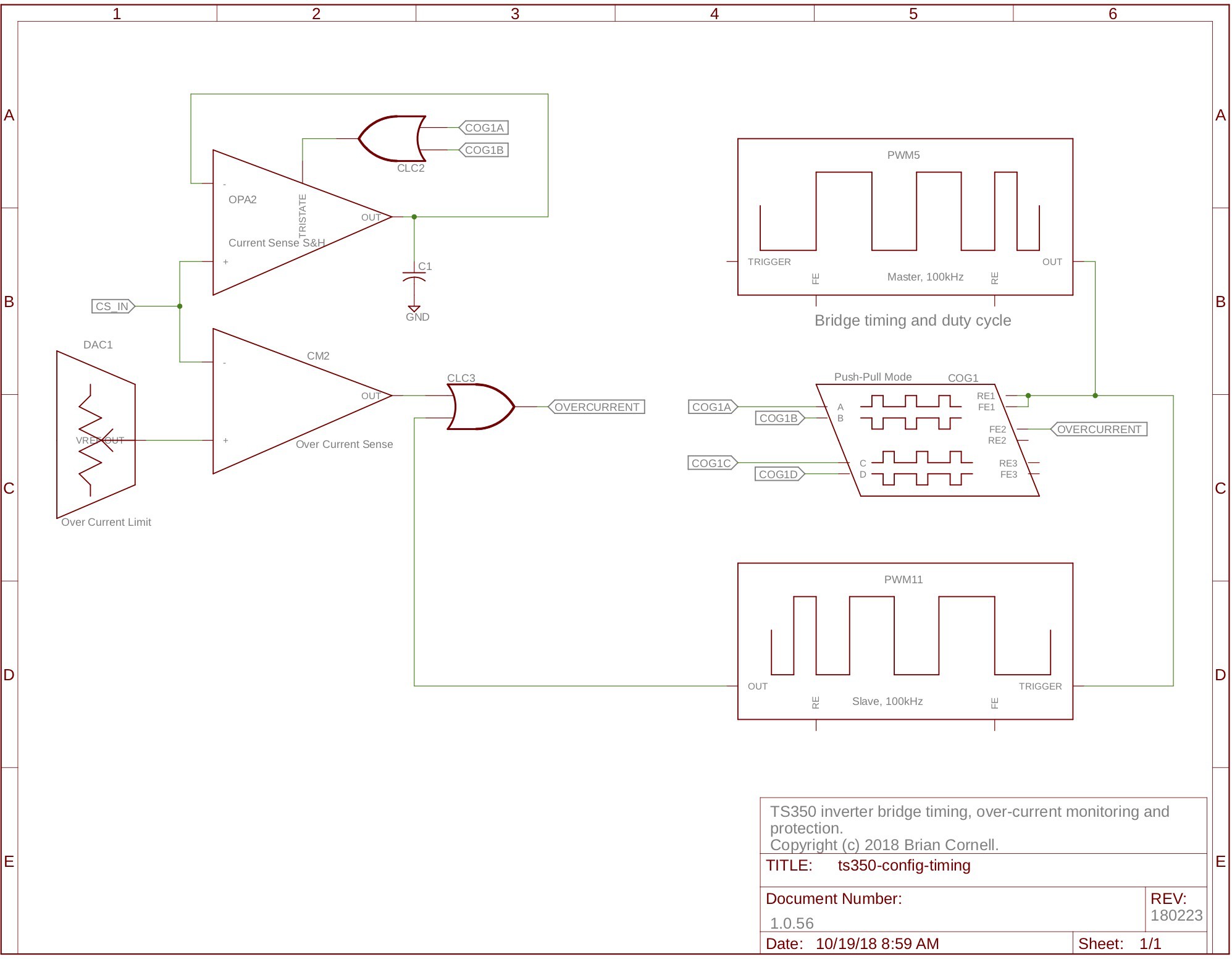

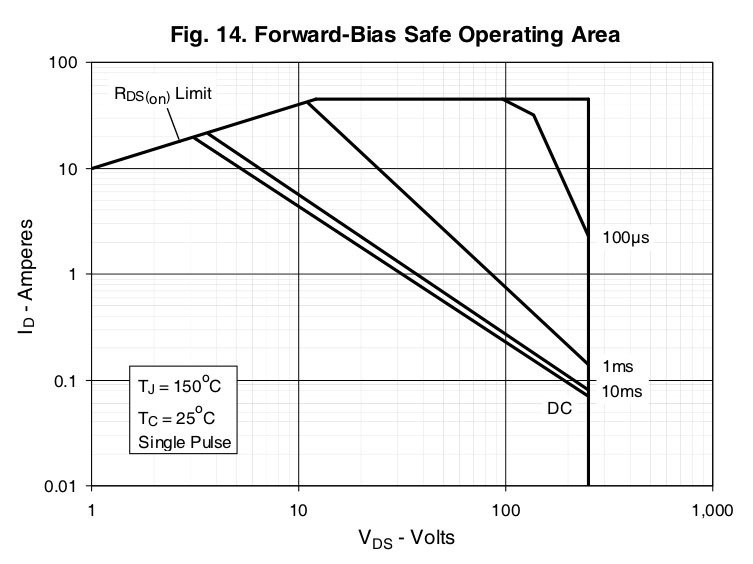

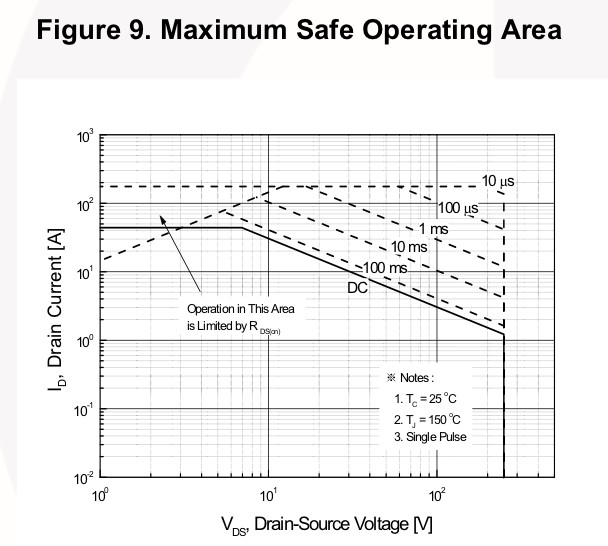

I designed the TS350 as an inverter capable of sourcing 350W continuous with the ability to deliver 500W (limited by operating temperature) for short durations. It was to do this over a wide input voltage range of 11 - 30 VDC so it could work with 12-28V systems. Not a problem, the inverter section would employ a traditional control loop to maintain a regulated 170VDC to the sine section. To do this with a full bridge and maintain flux balance in the transformer core requires a center-tap, full wave rectifier configuration. The inductor in the output LC filter maintains current flow thru the transformer secondary during the bridge off time which prevents the core from resetting. I had validated all of this in the TS50 platform.

Or so I thought. I had built center-tap transformers in the TS50 but their secondaries only delivered 60V. The TS50’s transformer delivers 170V but it is not center tapped. This turned out to be my big miss.

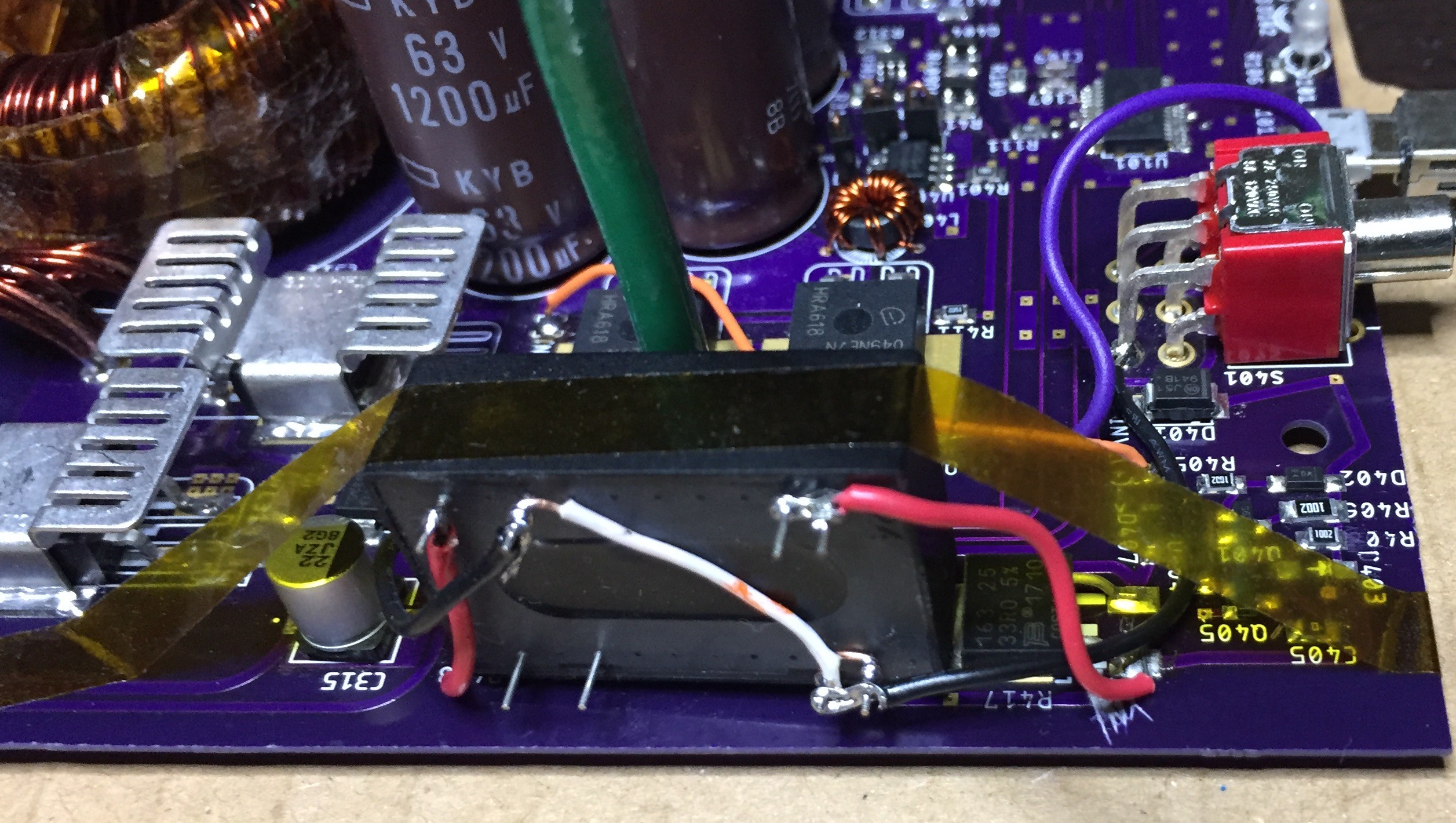

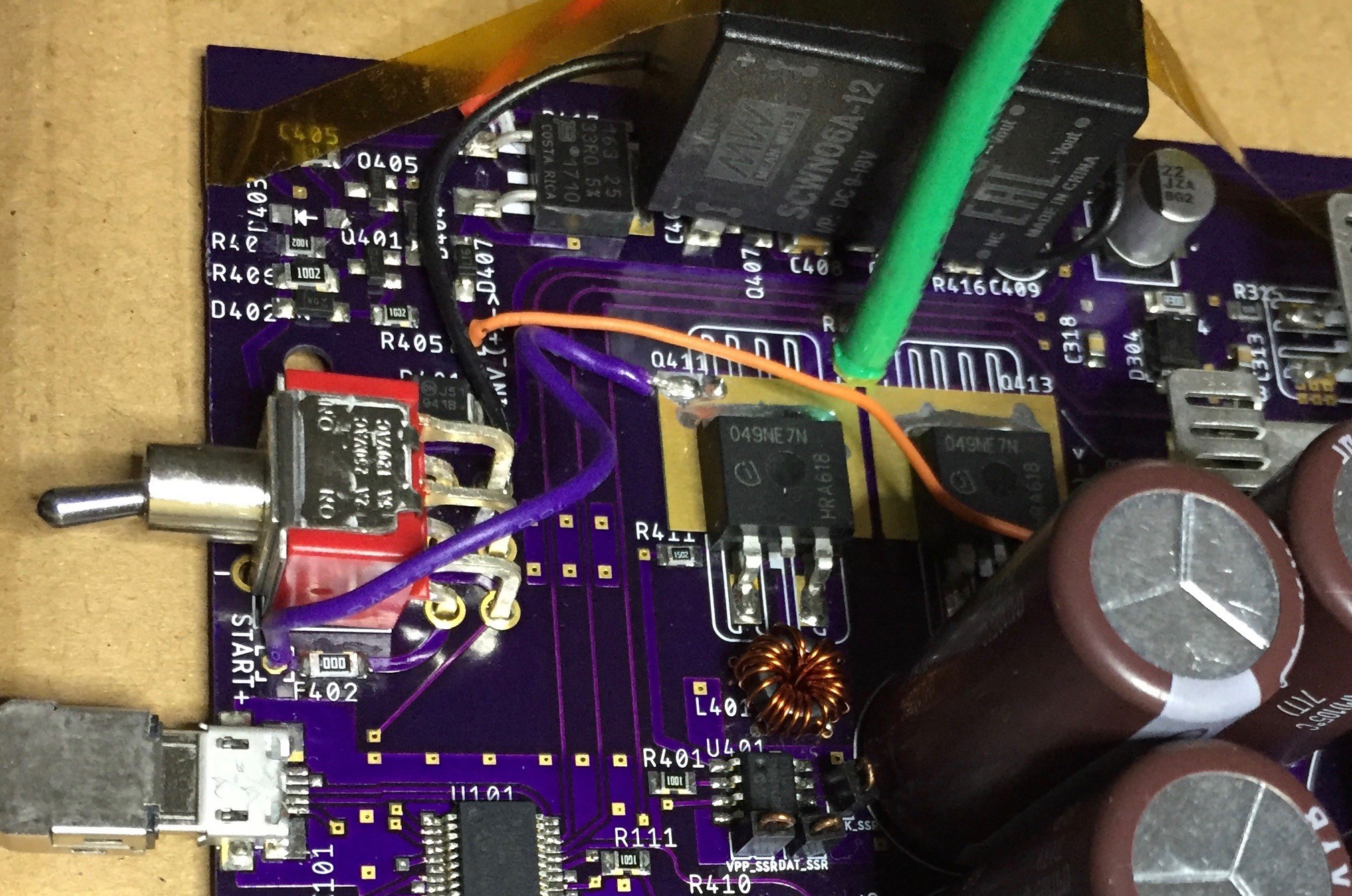

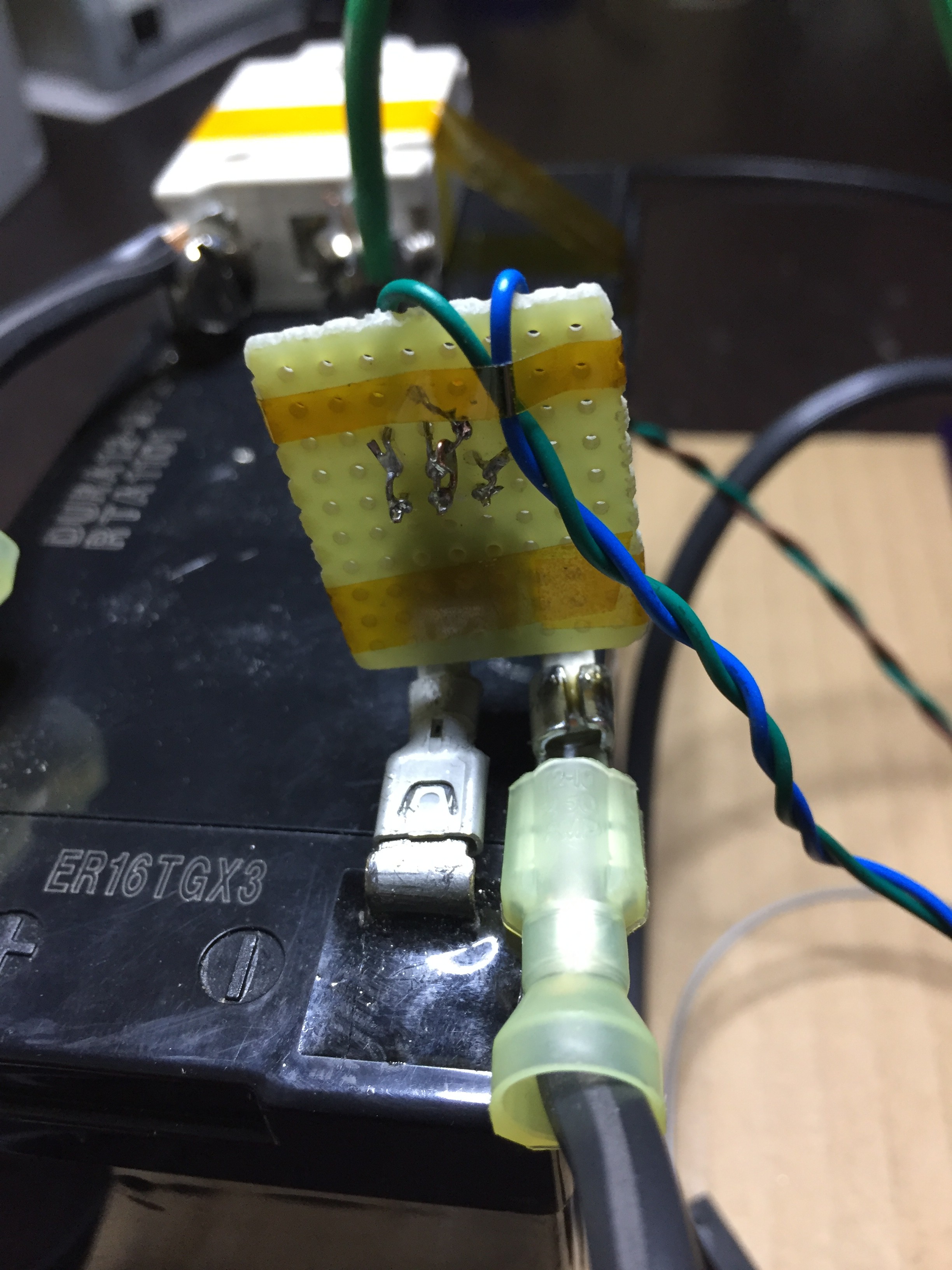

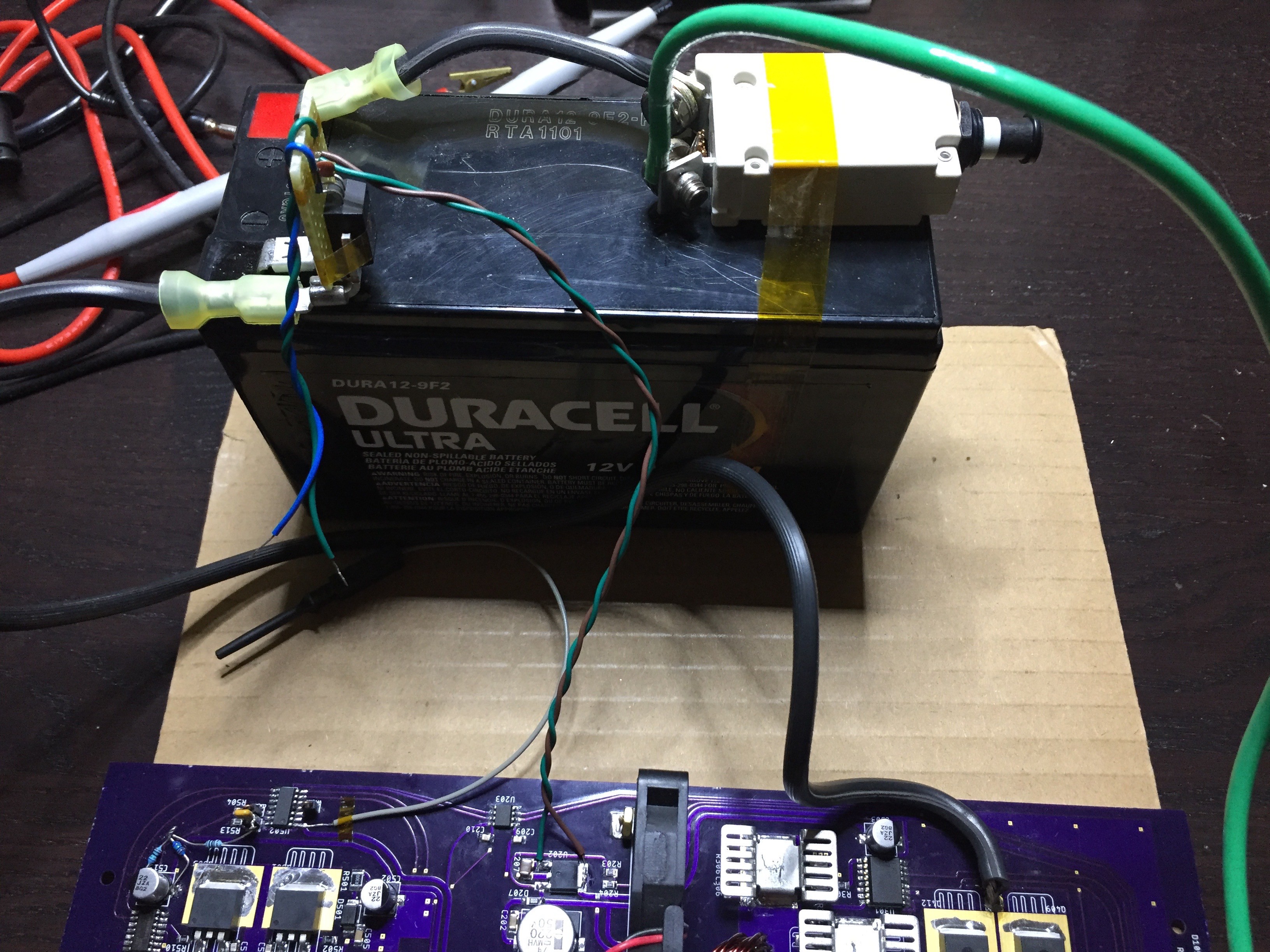

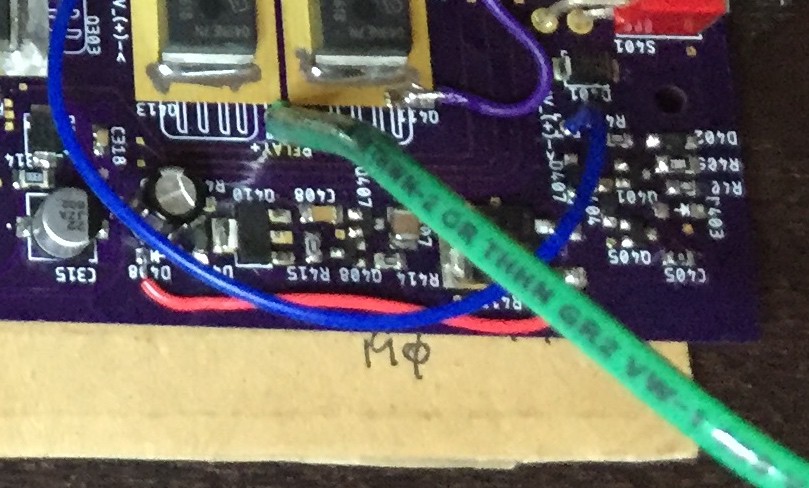

So I get my shinny PCB from the fab and start assembling section by section, testing as I go to: controller - check, start circuit - mostly check, bridge - check. I install the toroid wound transformer to test before moving on to the secondary supplies & sine section - don’t want it destroying things. I fire it up and take a look at the outputs: it shows a very large resonant ring but is otherwise functioning as expected. I’ve seen this before and many SMPS transformers will do this with their secondaries open so I’m not overly concerned. I complete the secondary power supplies, hook-up the DC load, and that’s when the trouble begins.

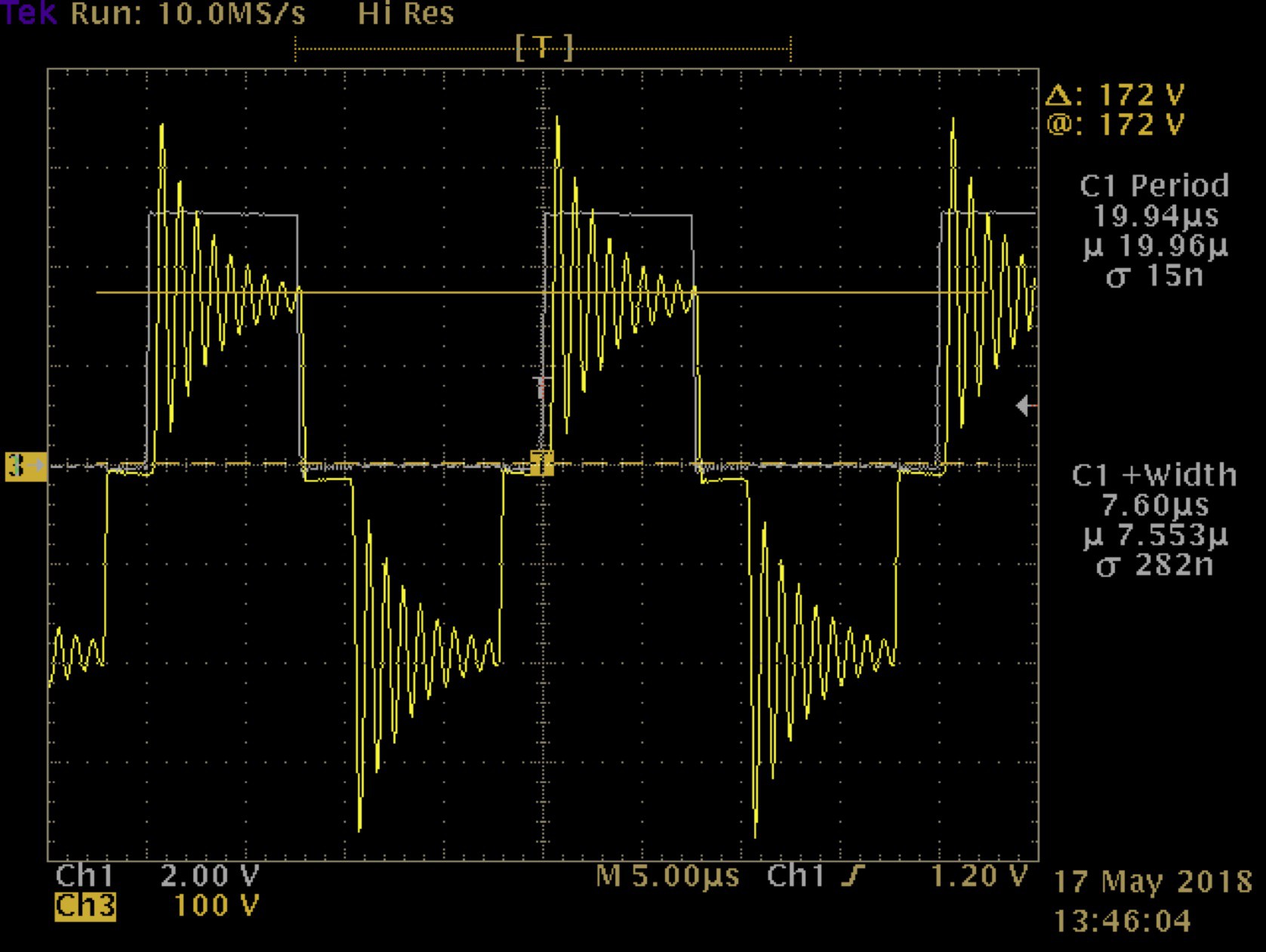

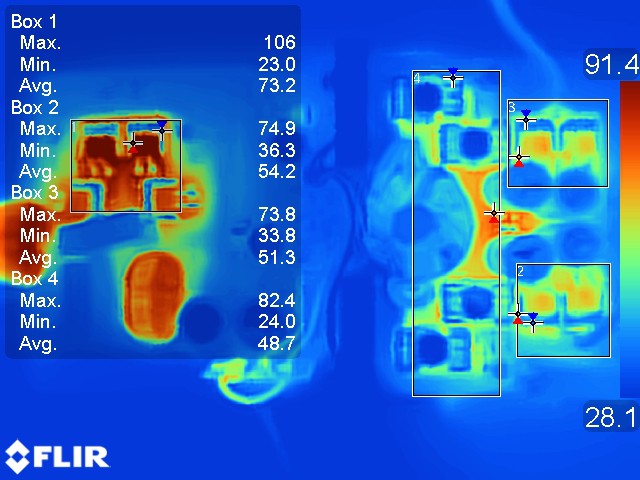

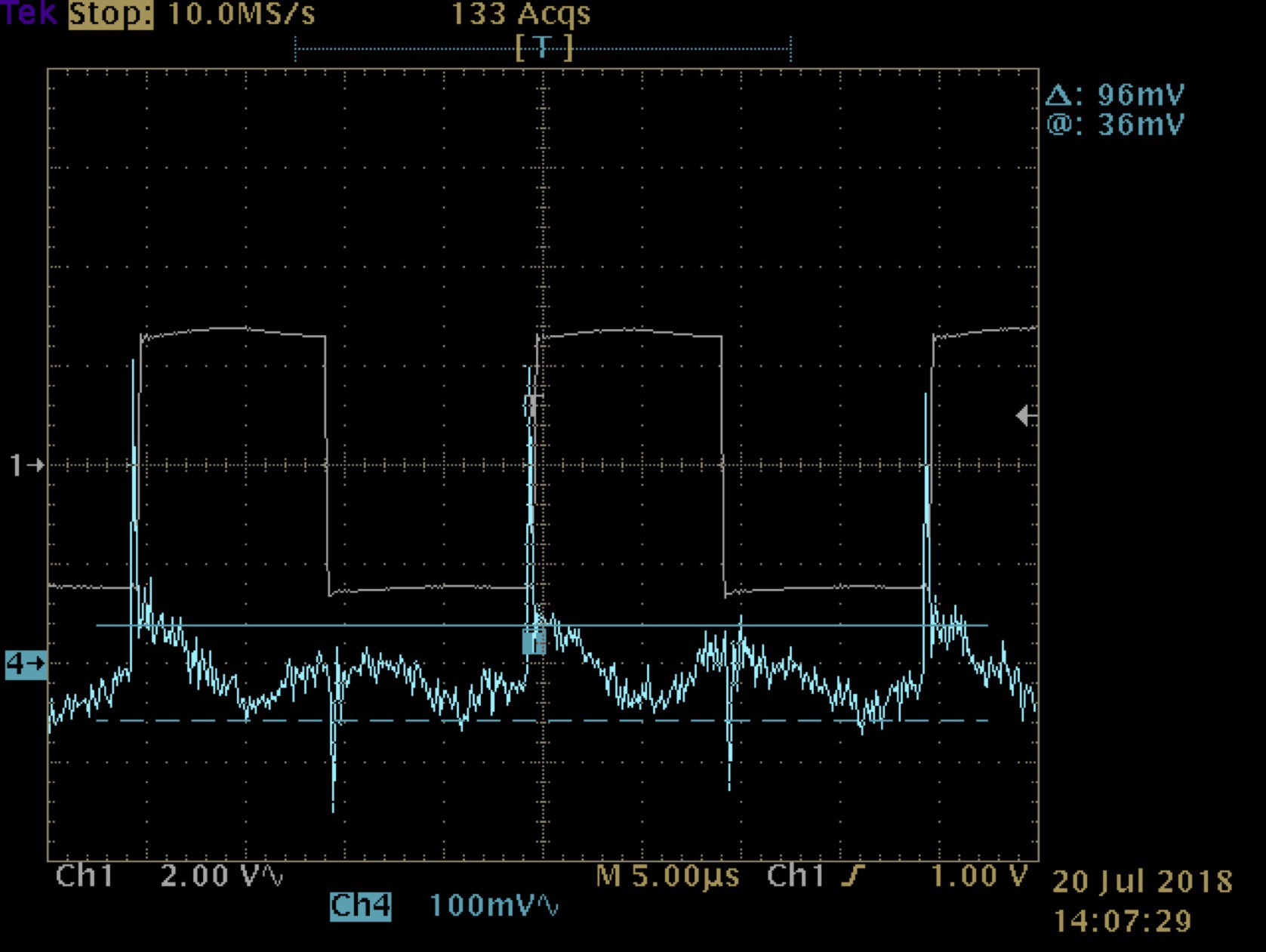

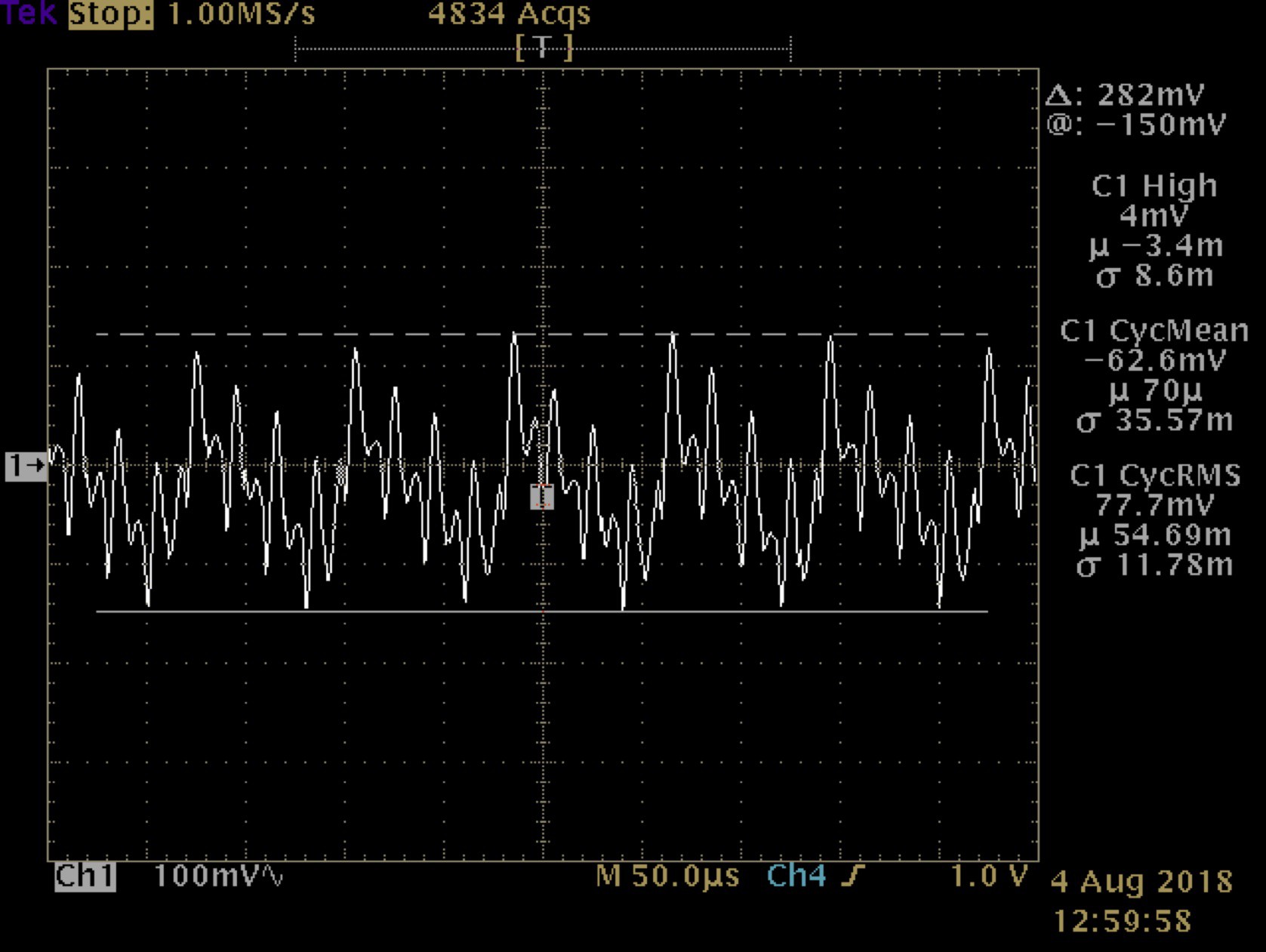

Above is the waveform at the anode of one of the rectifiers with a 1A load applied. Note the scale for CH3 - 100V. The cursor marks the 'no ring' expected voltage. The amplitude of the first ring cycle is nearly 200V! Even with 35nS reverse recovery times and generous thermal pads the rectifiers run hot (>50C) due to the ring. High loads make it worse. Higher input voltages make it worse. Of course this ring is reflected to all the windings. It renders my primary current sense circuit useless. It’s amazing the thing runs at all. After mucking with it for a few hours it’s obvious that a transformer rebuild is required or the design is DOA.

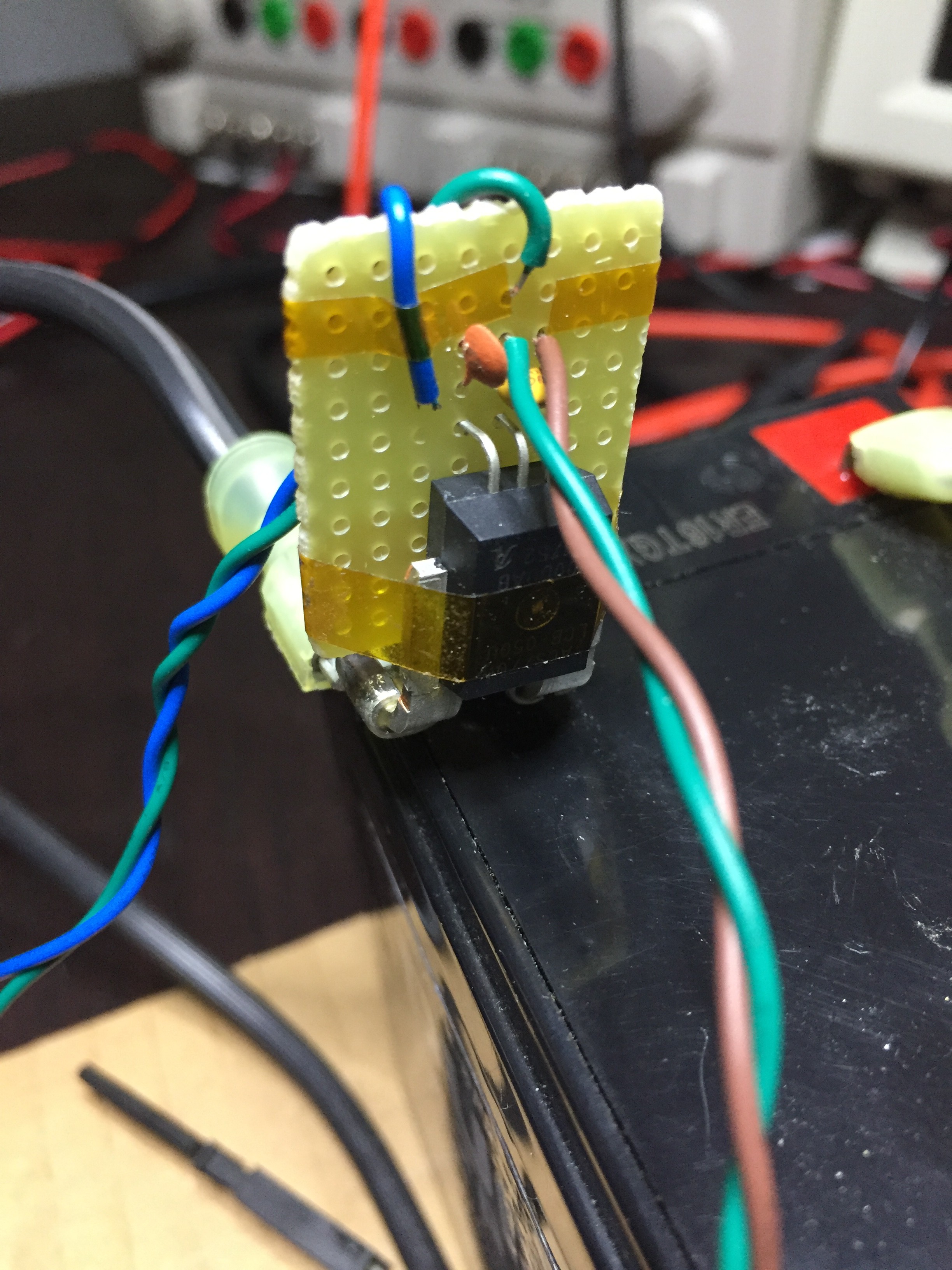

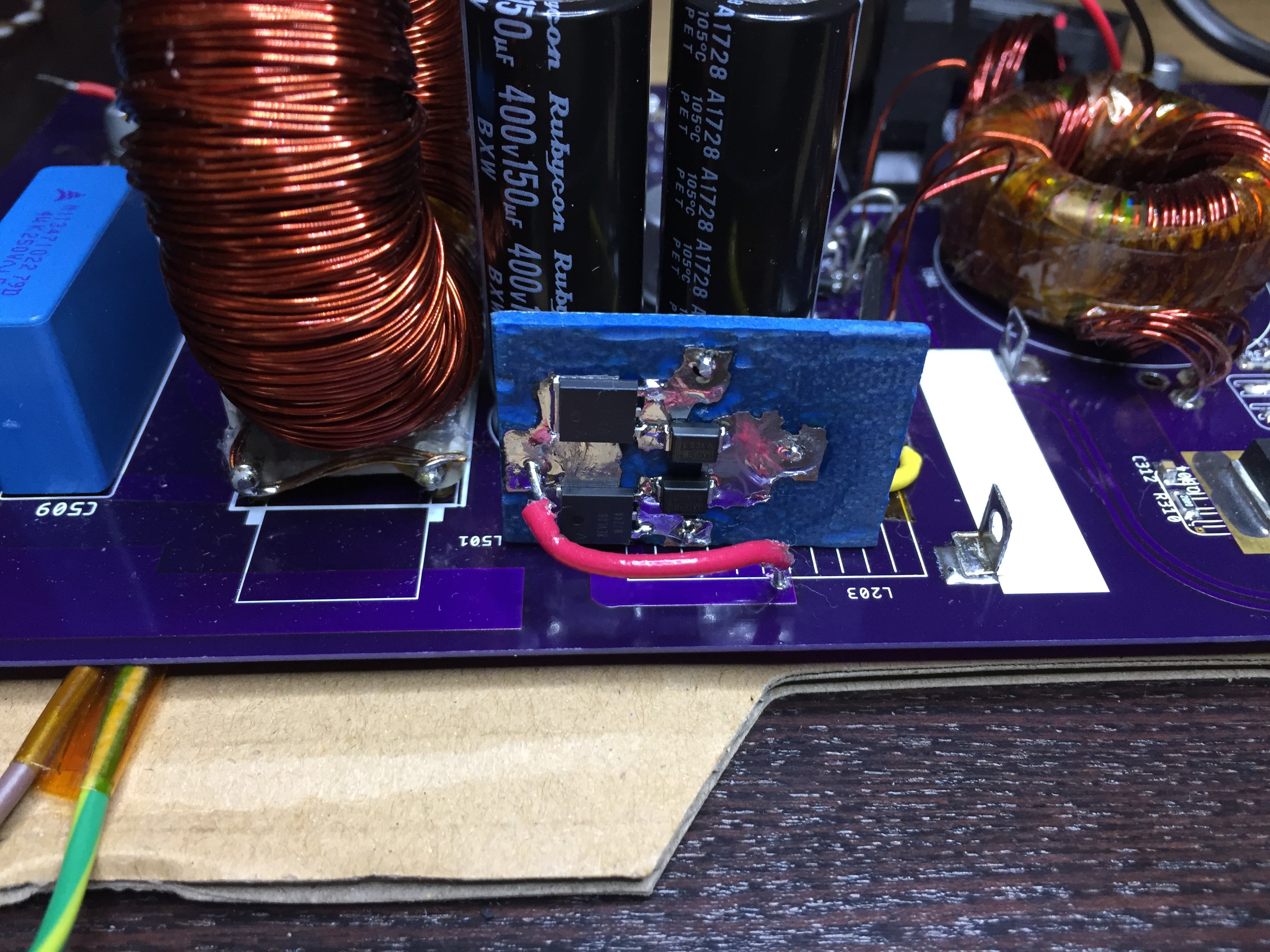

So started a two-month journey to come up with a working transformer. Along the way I earned another degree from the school of hard knocks: when designing a power supply - any kind - always start with the transformer. I had done this but with an inadequate working knowledge of high voltage windings.

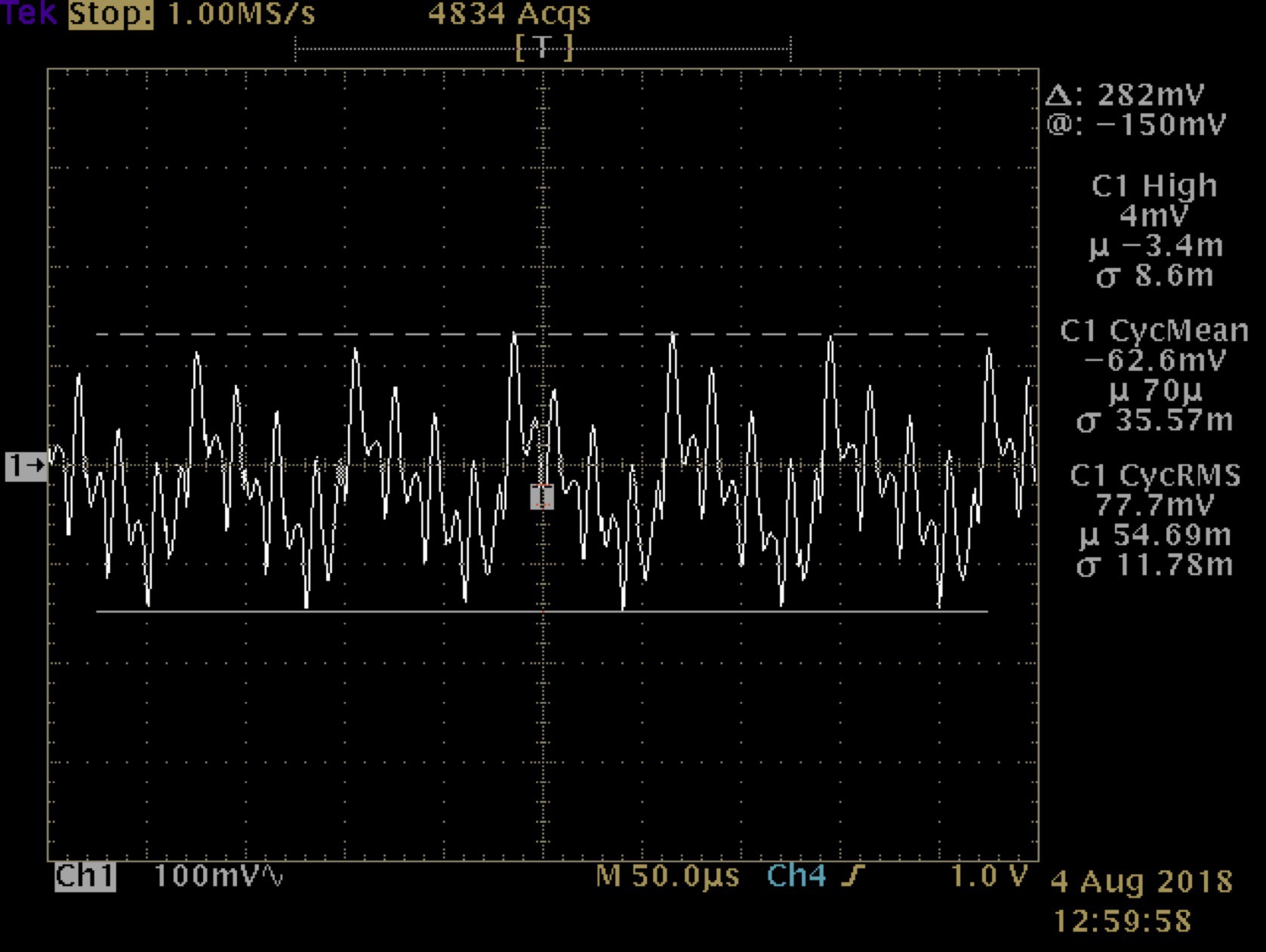

I built-up another copy of the full bridge board used in the TS50 (easy to swap transformers) and proceeded to test a dozen different builds using RM & toroid cores with a variety of winding configurations. Interleaved, bifilar, interleaved & bifilar, foldback, single layer, a combination of all of them. Faraday screens too: for both primary & secondary. But it didn’t matter - the results were consistently bad. The ‘best’ design had a measured lumped parasitic capacitance of 10nF and the worst greater than 130nF but in-circuit their performance was almost indistinguishable: a resonant ring with a peak amplitude greater than 100V above the design voltage with a decay lasting the entire duty cycle (5-90%).

The frequency of the ring...

Read more »

Collin Matthews

Collin Matthews

Jesse Farrell

Jesse Farrell

sky-guided

sky-guided

Peter Walsh

Peter Walsh