-

TERNARO playground

08/10/2018 at 08:23 • 0 commentsUsing Circuits.CC engine I created an interactive web site TERNARO.COM where you can play with different switches of TERNARO configurable logic block (by mouse) and see how they are translated into bitstream (at the bottom) and how equivalent circuit may look (on the right) - this should help other people to understand how it's supposed to work...

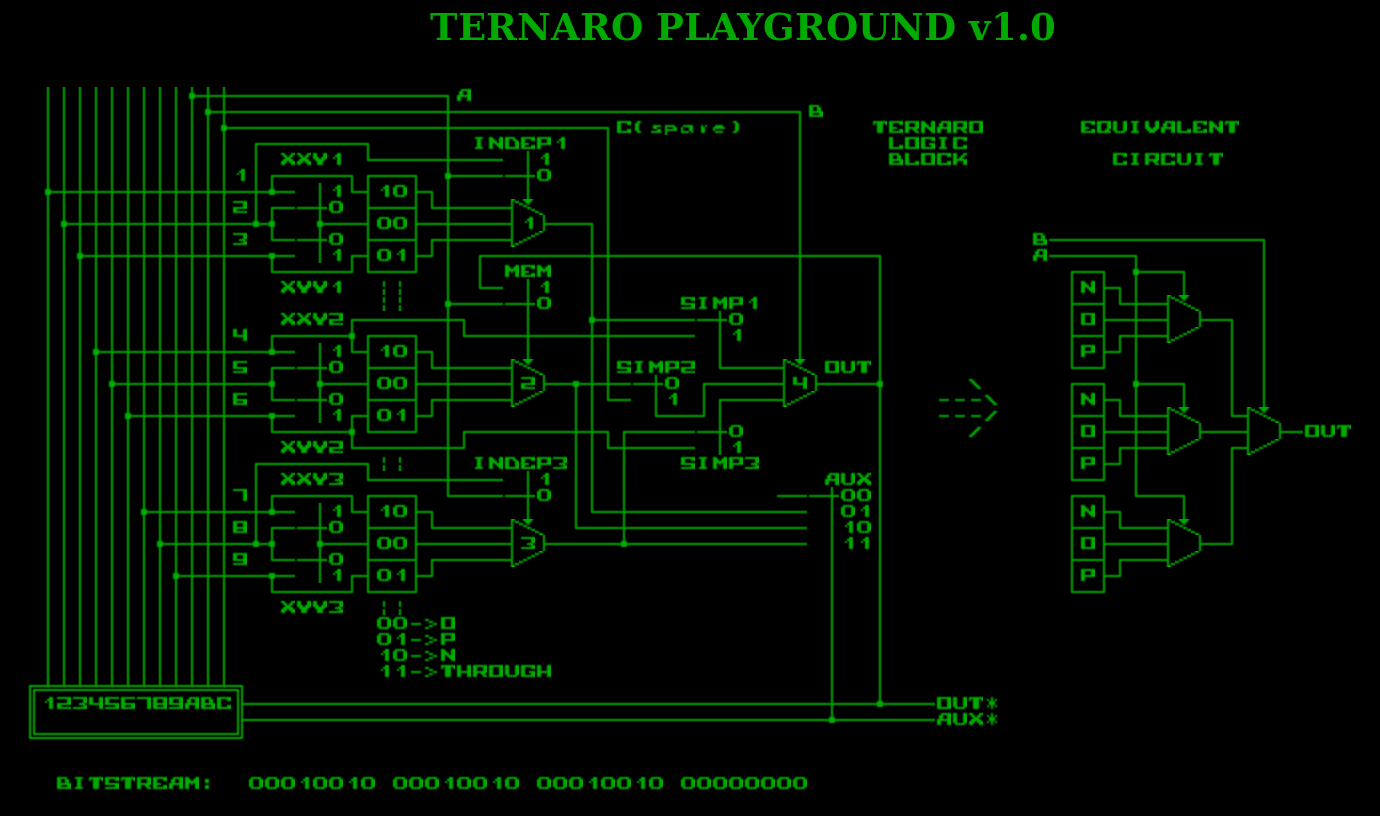

For example, this is 2-input LUT (can be used as 9-trit ROM):

![]()

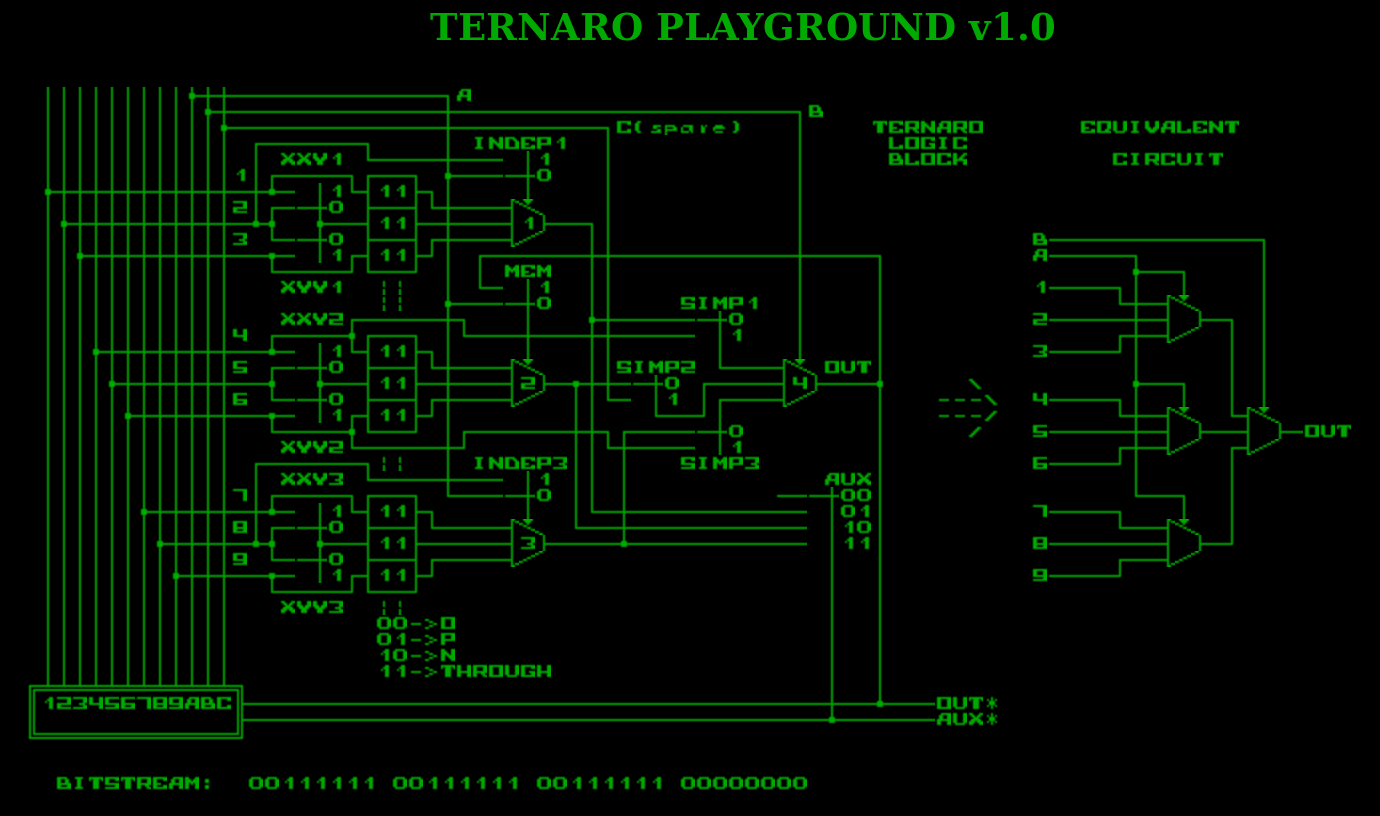

This is 9-to-1 multiplexer:

![]()

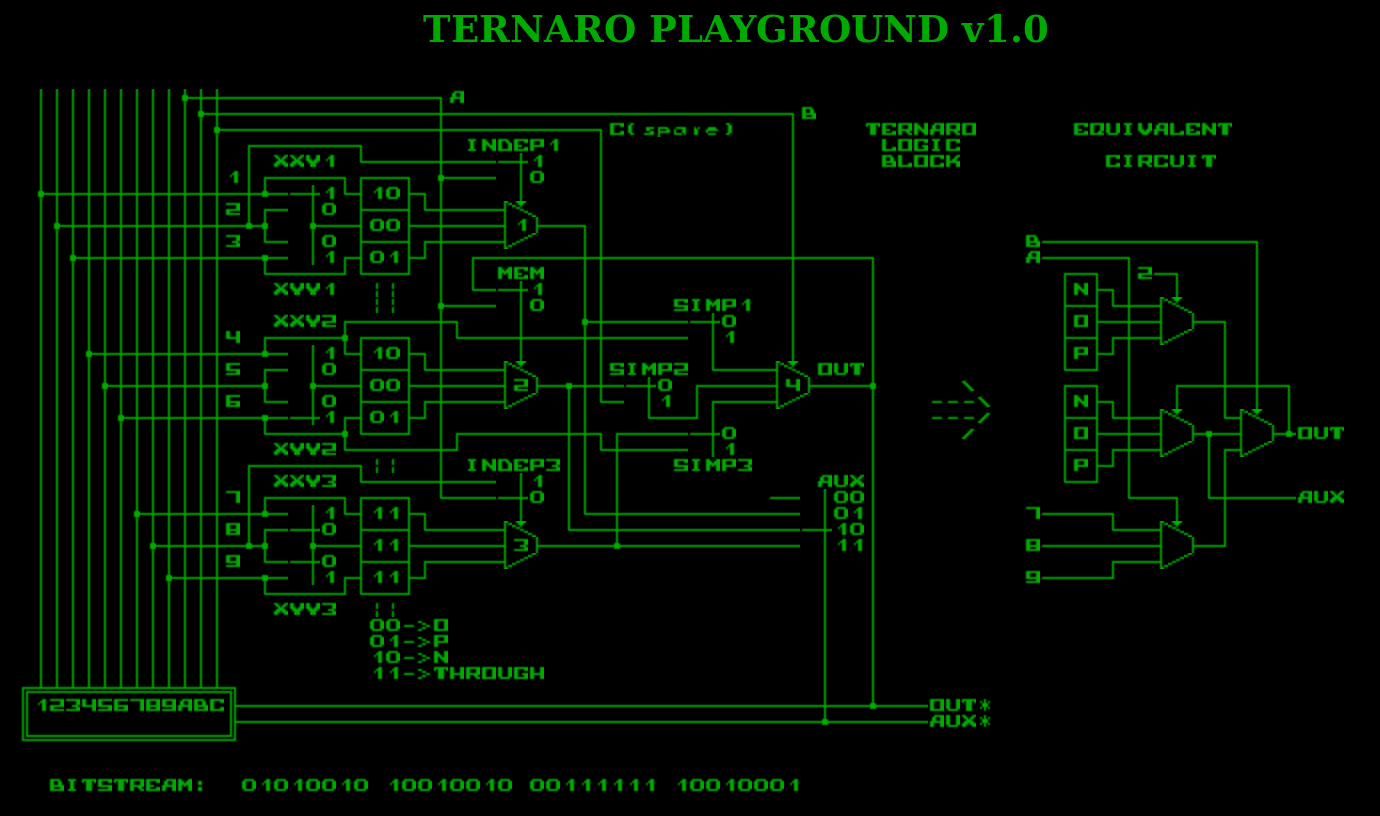

Memory (transparent latch) with 2 independent inputs (2nd MUX must be in buffer mode NOP):

![]()

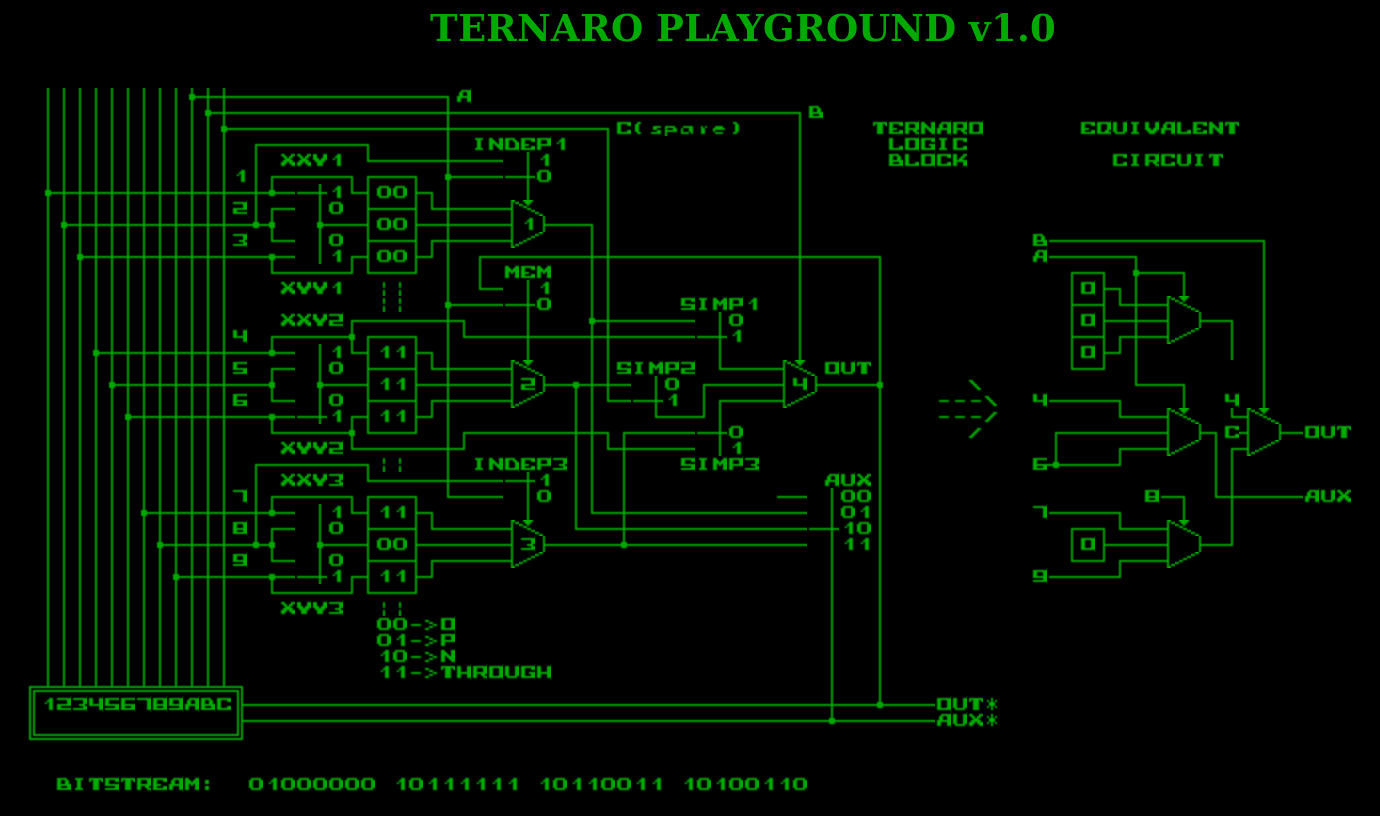

And it could be any mix of the settings:

![]()

Enjoy ;)

P.S. Source code to look at: https://gitlab.com/shaos/circuits_cc/blob/master/src/TERNARO.R

and https://gitlab.com/shaos/circuits_cc/blob/master/www/ternaro.html

-

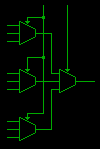

Binarized TERNARO

07/29/2018 at 10:15 • 0 commentsYes, ternary FPGA could be used as binary FPGA :)

In case of TERNARO for this purpose every 3-input ternary multiplexer should be converted to 2-input binary multiplexer by setting XYY or XXY configuration bit - it turns every MUX to E12 or E21 respectively:

![]()

From binary point of view E12 is a multiplexer with lower threshold (about 2.1V for 5V power supply) and E21 is a multiplexer with higher threshold (about 3.5V for 5V power supply). So now we can build circuits with hysteresis (see this log for more info about actual thresholds):

![]()

Also in case of "binary mode" multiplexer 2 will be used only to form MEM cell (and will be ignored if logic block is used as LUT), so vertical signals 4,5,6 will be always free to be used for interconnect.

Another interesting trick - in "ternary mode" every constant O (set by 00 pair) is actually direct connect to input Vref, so in "binary mode" we may re-name input Vref to I0, because effectively it becomes additional general purpose input for the circuit (input number zero). And constants N and P in "binary mode" becomes "0" and "1" respectively (as they stay to be direct connects to ground and positive power supply):

00 -> Vref input of the chip (I0) 01 -> Constant "1" 10 -> Constant "0" 11 -> Through connection to vertical lineLater we can add support of "binarized TERNARO" into Yosys for example and then people will be able to program TERNARO using standard Verilog :)

-

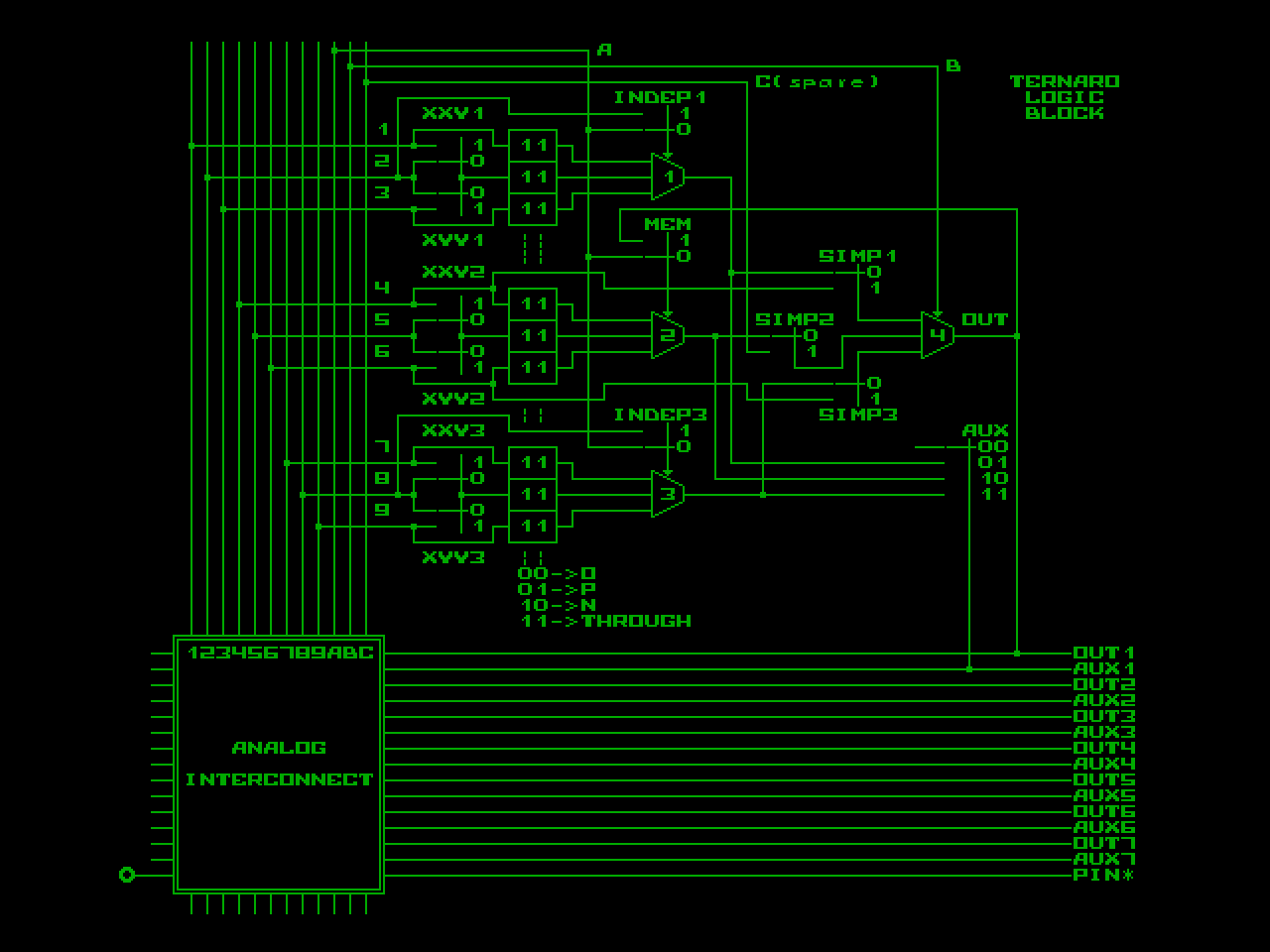

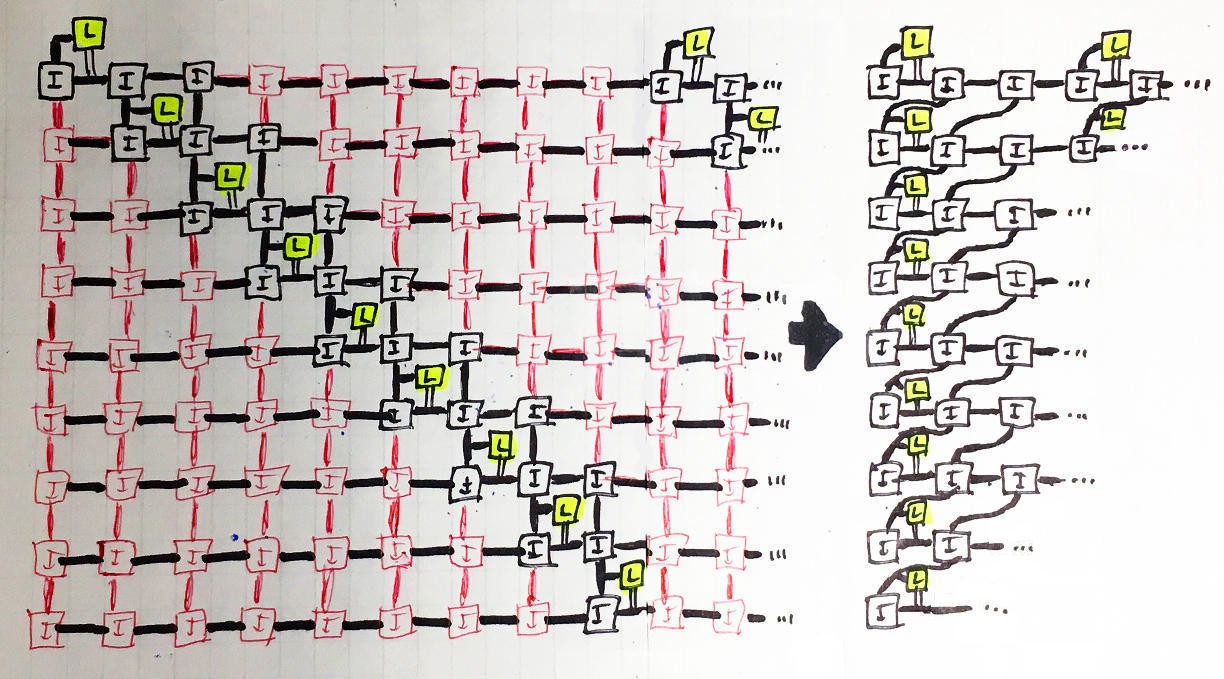

TERNARO topology

07/27/2018 at 05:13 • 0 commentsThis is how I imagined TERNARO from inside:

![]()

Bitstream should define every column one by one (from left to right) with every channel in the column (from top to bottom) like L-I-I-I-I-I-I-I-I-I (4+6*9=58 bytes per every channel/column intersection).

Every interconnection block [I] behaves as 12 switches with 16 positions each (position #0 means no connection):

![]()

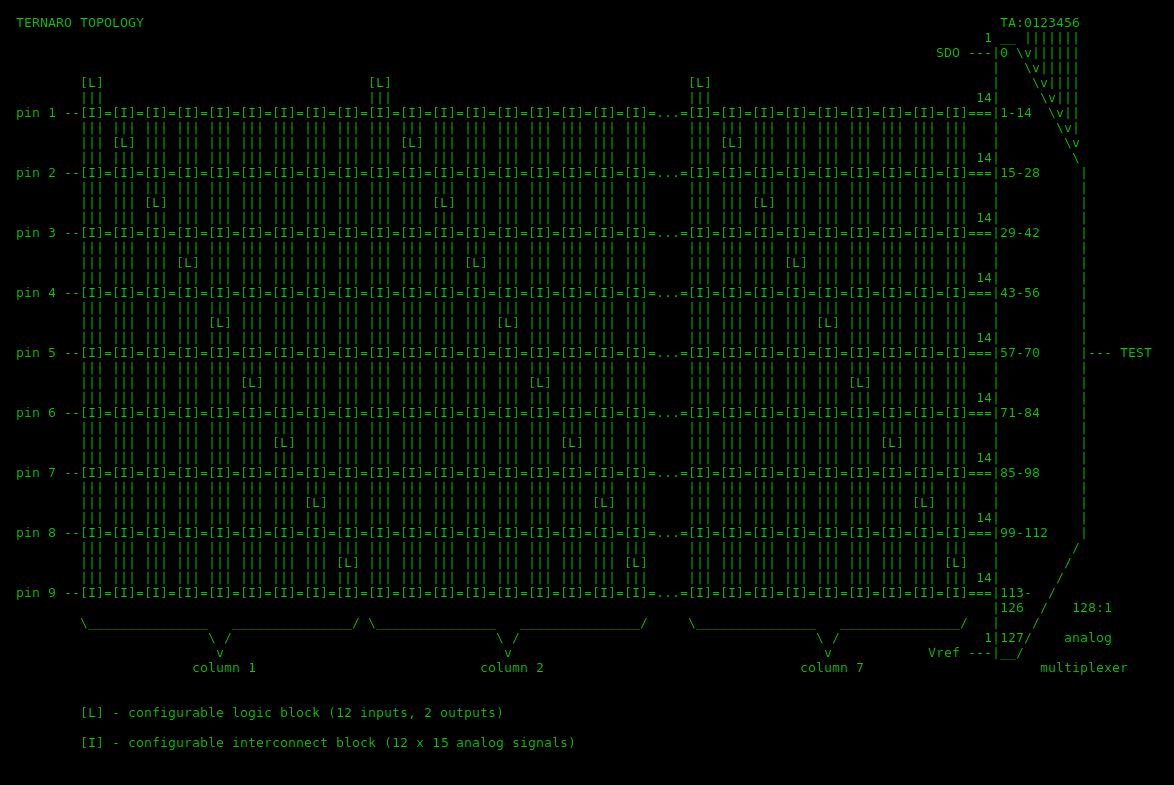

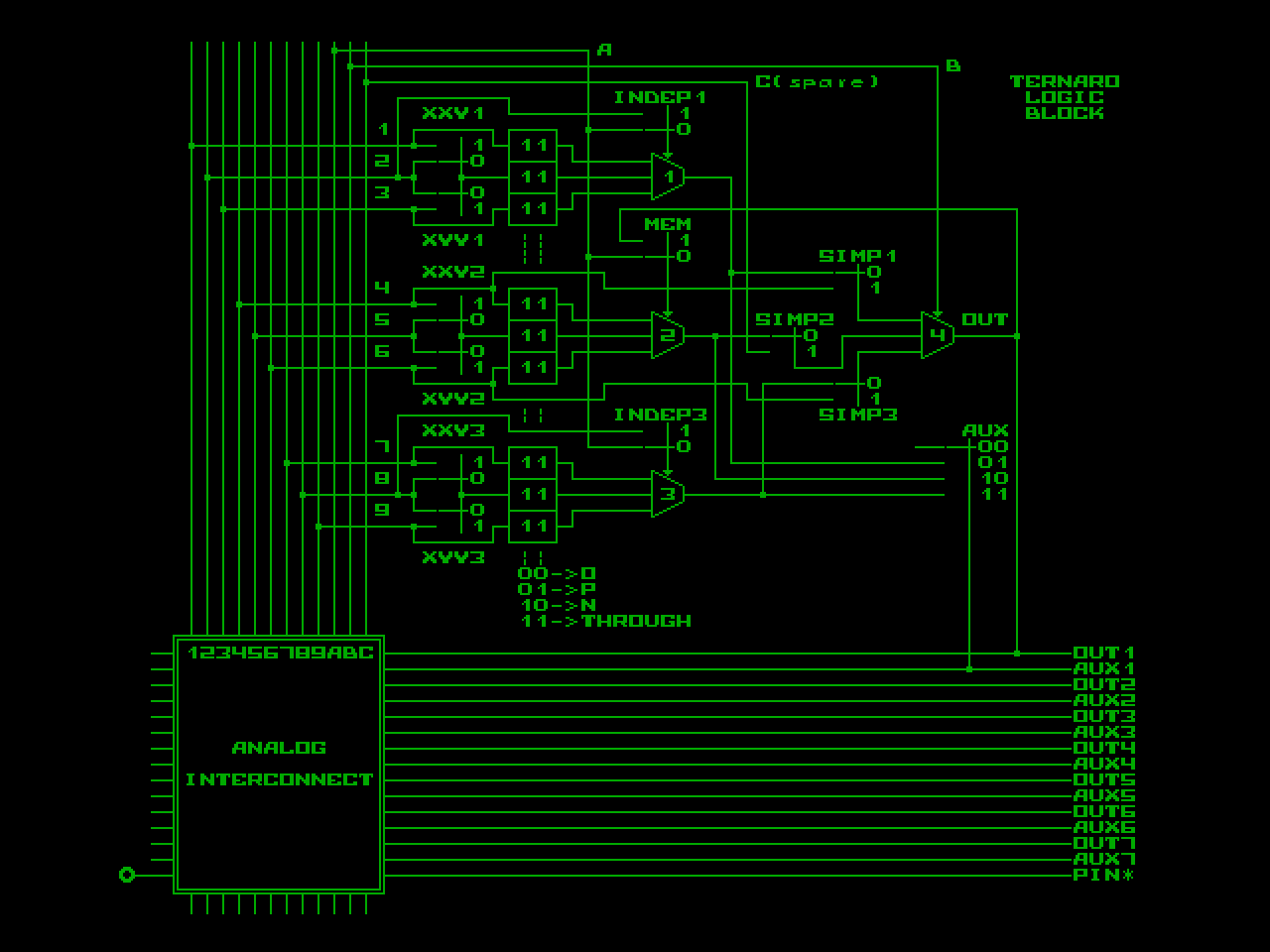

And every logic block [L] looks like this (with nearest interconnect showed as well):

![]()

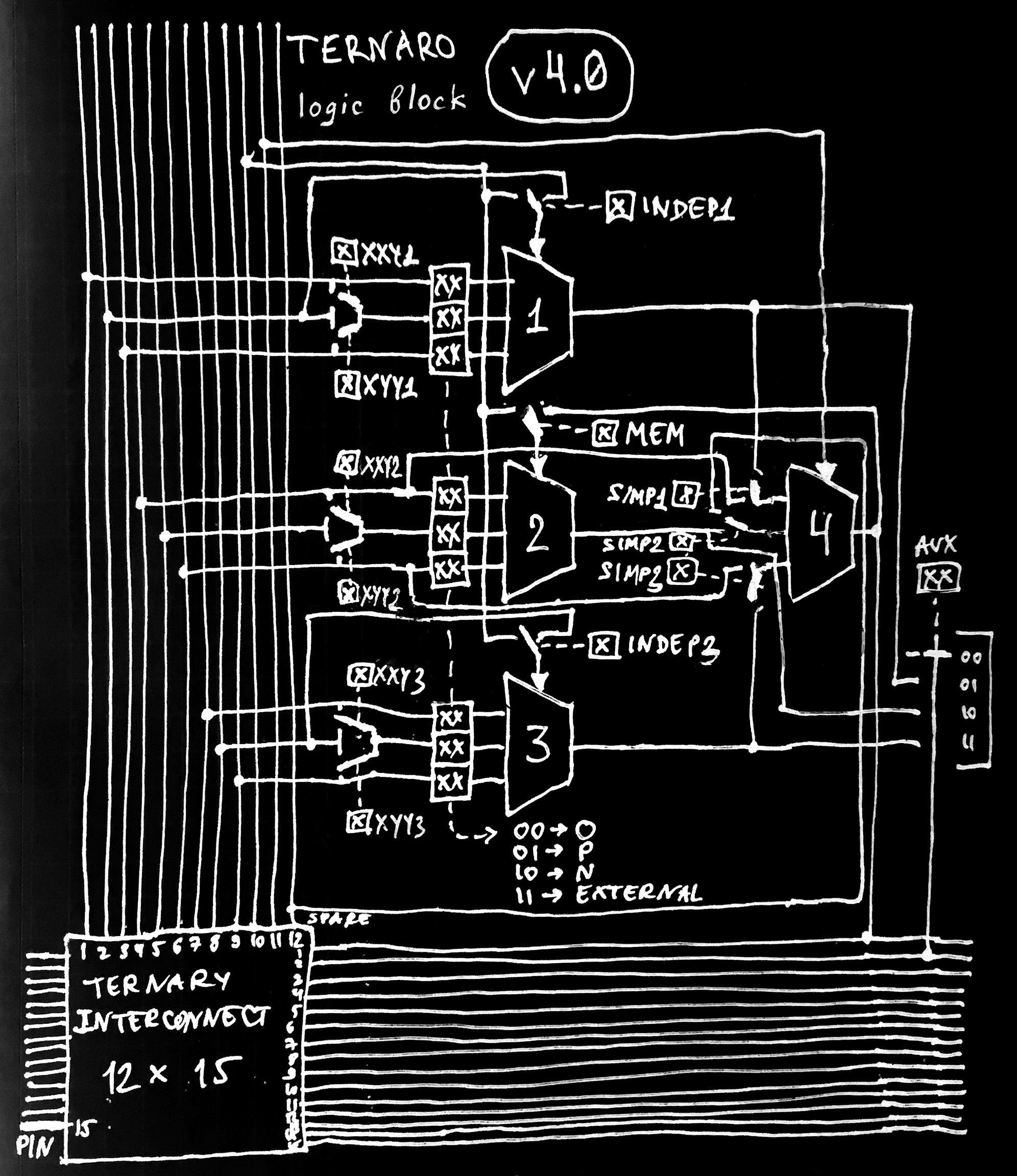

Approach when adding another pin (and another horizontal channel) requires additional interconnect block in every channel for every column is not very scalable. So later I can do some reduction like showed below:

![]()

In this case it will scale linearly with adding more pins. How many diagonals with interconnects can be removed to still be flexible for most real life applications? Honestly I don't know. Probably I need to write synthesis/place&route software first and see how it goes with different numbers. This is how one of the most extreme cases of reduction can look:

![]()

-

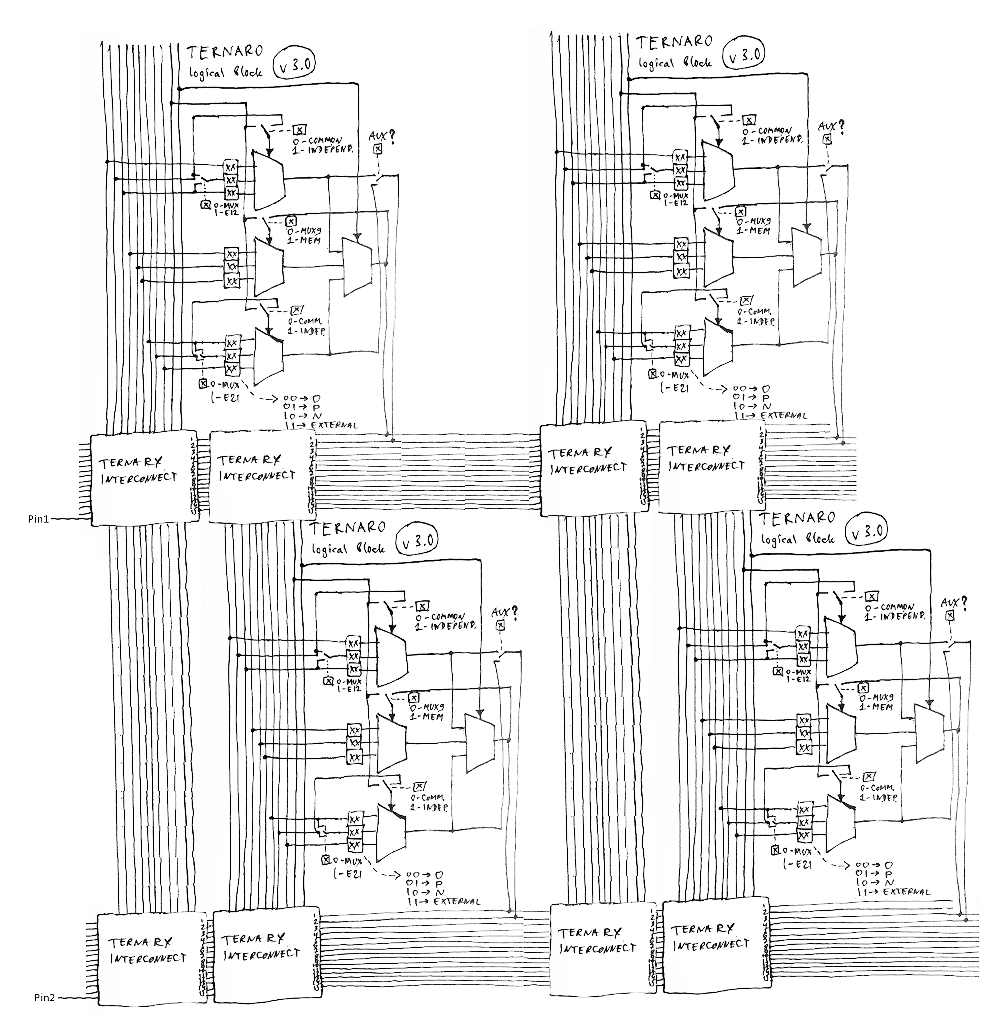

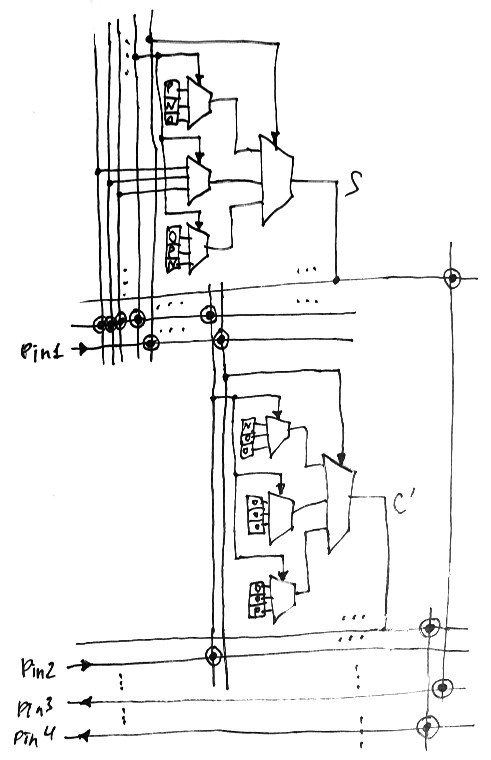

Bigger picture

07/22/2018 at 09:59 • 0 commentsAs I wrote before it should be a grid of 7 x 9 logic blocks (63 total) where every horizontal "channel" is having 15 lines and one of which is a pin (so it is 9 pins total), but less number of channels is also possible - for example below is 2 x 2 (unpractical because of only 2 IO pins are there, but good enough for demonstration purposes):

![]()

So in case of full scale 9 channels (one horizontal channel per every IO pin) every TERNARO logic block will need NINE interconnect blocks to cross every channel, so total length of bitstream will be (4+9*6)*63 = 3654 bytes (from up to down from left to right) and this bitstream needs to be pushed into the chip by external microcontroller (binary one of course).

About testability - test address inputs TA0...TA6 (address is binary) will choose which HORIZONTAL ternary line needs to be connected to test output TEST - it is 15*9=135 of them, but as we can see every 15th one is an IO pin, so we obviously have direct access to pins already and we can skip all of them so it's 135-9=126 total plus 1 output for SDO - serial data out for Slave SPI - if TA=0:

0000000 (0) - SDO output of Slave SPI 0000001 (1) - signal 1 of 1st channel 0000010 (2) - signal 2 of 1st channel 0000011 (3) - signal 3 of 1st channel 0000100 (4) - signal 4 of 1st channel 0000101 (5) - signal 5 of 1st channel 0000110 (6) - signal 6 of 1st channel 0000111 (7) - signal 7 of 1st channel 0001000 (8) - signal 8 of 1st channel 0001001 (9) - signal 9 of 1st channel 0001010 (10) - signal 10 of 1st channel 0001011 (11) - signal 11 of 1st channel 0001100 (12) - signal 12 of 1st channel 0001101 (13) - signal 13 of 1st channel 0001110 (14) - signal 14 of 1st channel 0001111 (15) - signal 1 of 2nd channel 0010000 (16) - signal 2 of 2nd channel ..... 1111110 (126) - signal 14 of 9th channel 1111111 (127) - Vref (for testing purposes)And we have 1 extra signal (when TA=127) that could be used for example to test internal Vref level...

-

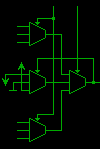

Logic behind TERNARO

07/22/2018 at 00:14 • 0 commentsI'm working on TERNARO design since January 2015. Main idea was to design ternary FPGA that may implement any ternary circuit that is built out of bunch of TRIMUXes (like TRIADOR from #Homebrew ternary computer for example). Base element of such FPGA that was chosen in 2015 is 9-to-1 ternary multiplexer:

![]()

It also may be used as 9-cell ternary ROM with 2-trit address and 1-trit output.

With little re-wiring we can get memory element out of it:

![]()

Left-center ternary multiplexer is connected as a buffer (unary function NOP) and it's the main reason why it becomes a memory cell with feedback loop like that.

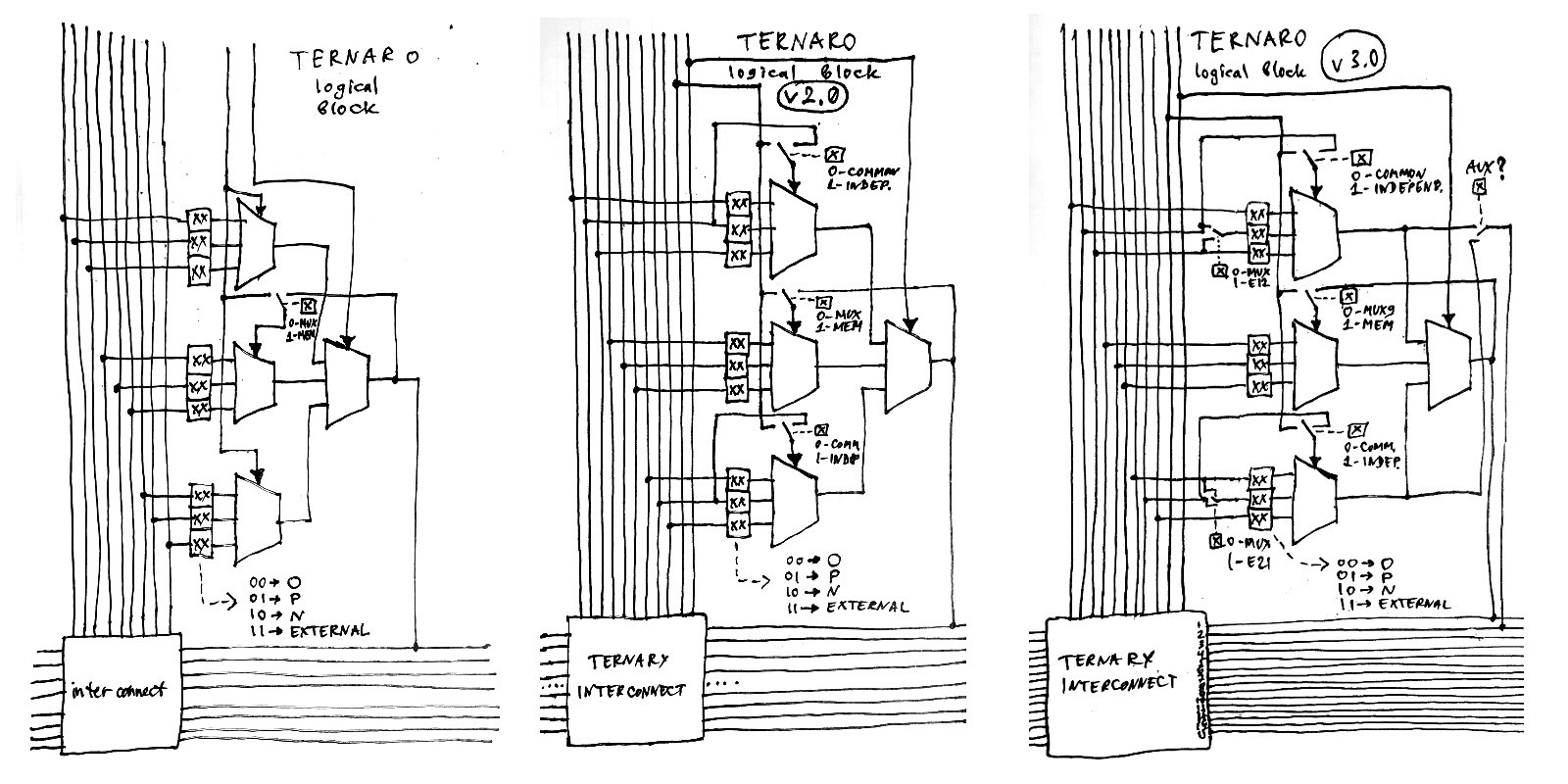

This is all versions of TERNARO configurable logic block design that I came up with in the last few days and you can see how it evolved in my mind :)

![]()

Today version 4 is the last and final design:

![]()

Now 9-to-1 multiplexer may be split to separate 3-to-1 multiplexers. But even with initial programmable capabilities we can easily implement things as ternary half-adder for example:

![]()

Also if we have 9 IO pins it means we have 9 horizontal channels with 15 signals in each...

SHAOS

SHAOS