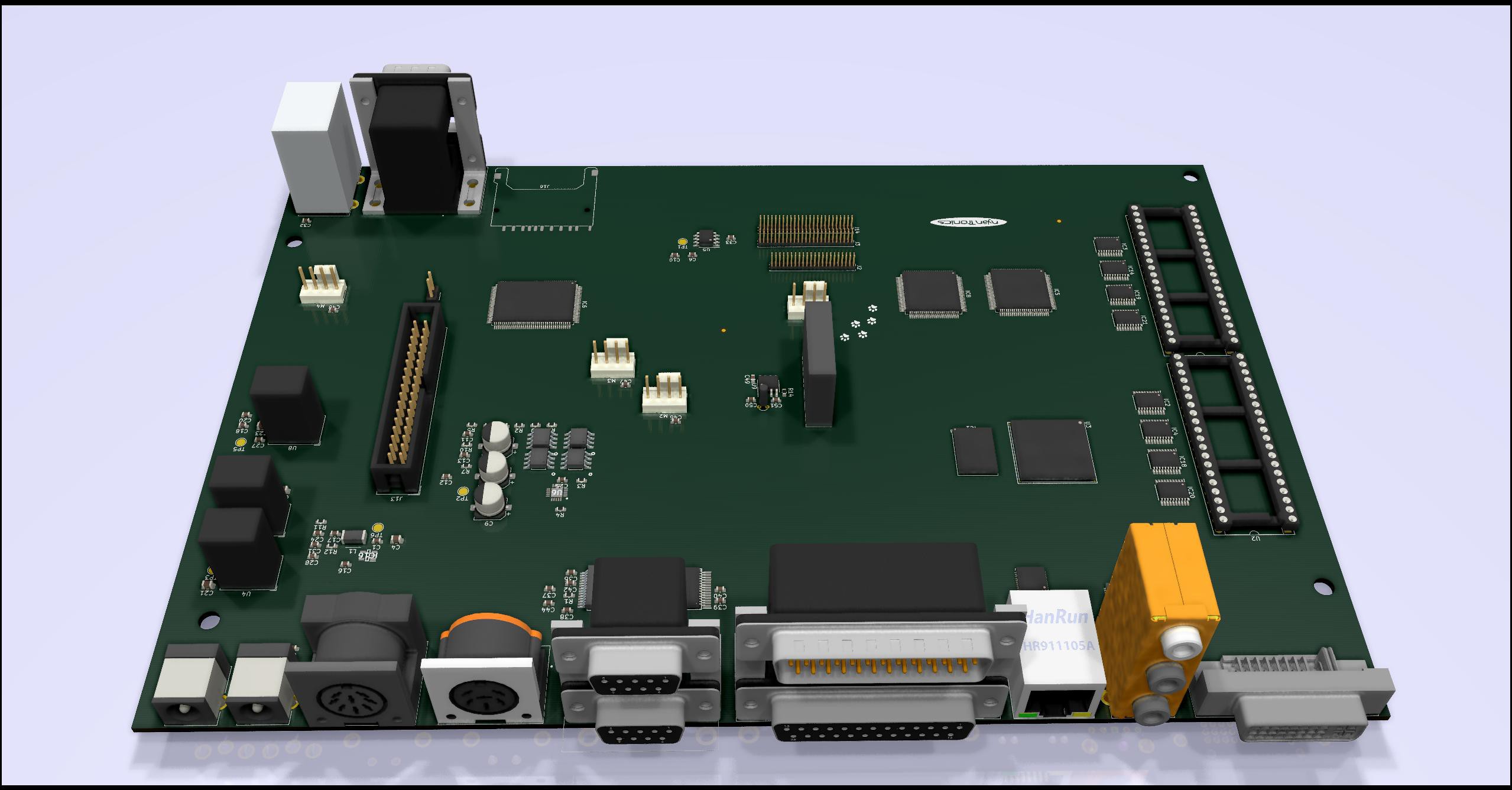

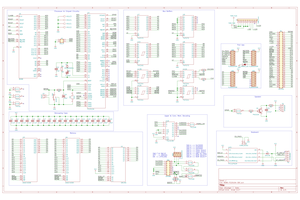

The project's PCB is being designed in KiCad, with a custom enclosure in progress that will fit the custom PCB form factor. At this point in the project's development the specifications are:

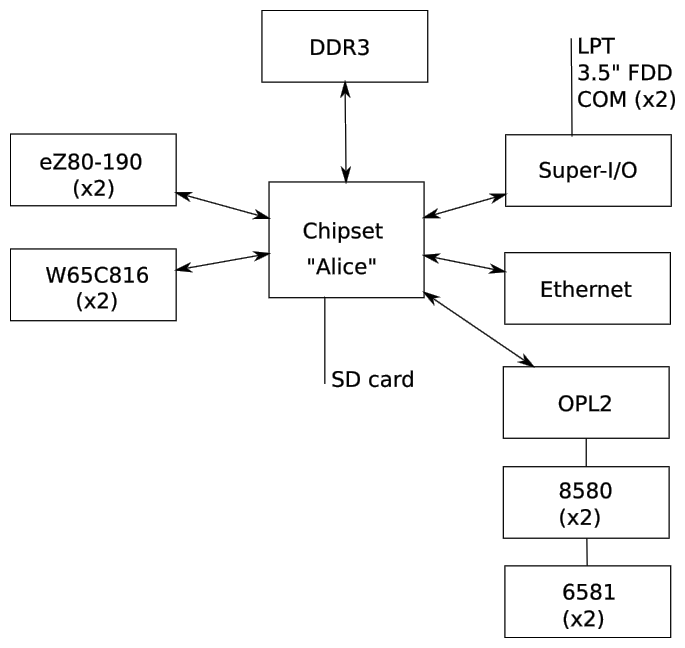

- W65C816 MPU (x2)

- eZ80-190 MPU (x2)

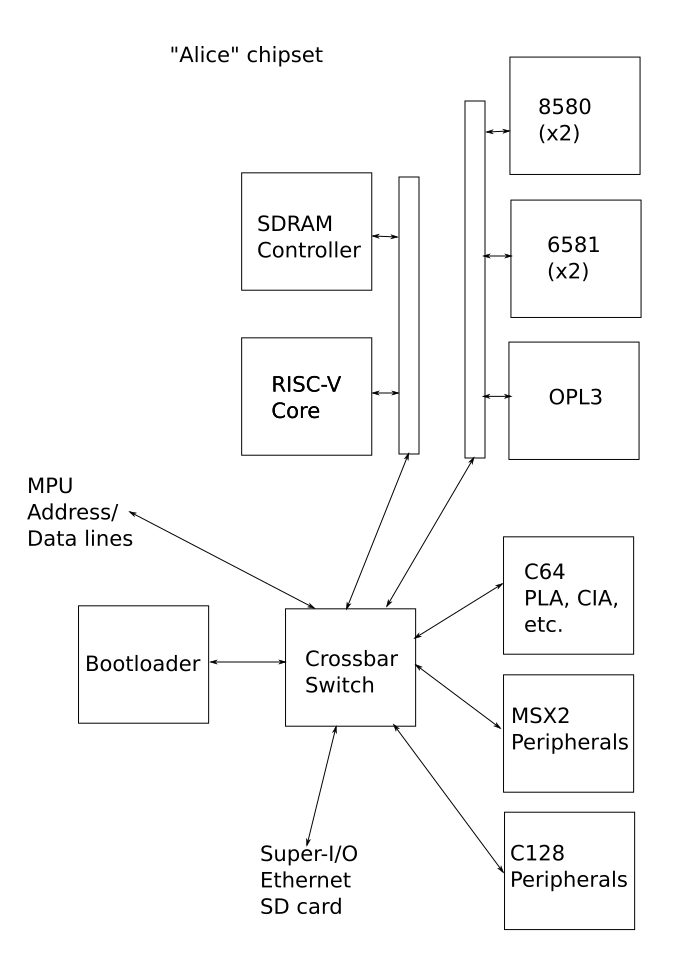

- MIPS soft core (in FPGA)

- 256+ MB of DDR3 SDRAM

- "Alice" chipset.

- Yamaha OPL3 synthesizer

- Commodore 8580 SID (x2)

- Commodore 6581 SID (x2)

- 100 Mbit Ethernet

- SD card reader

- Parallel port (SPP, EPP & ECP)

- RS-232C port (x2)

- DVI output (VGA compatible)

- Stereo audio out, microphone input

- Single 3.5" floppy drive

Current status:

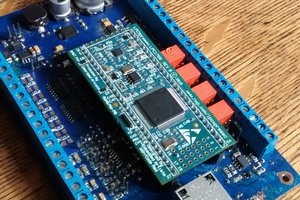

- Developing the "Alice" chipset using a Lattice ECP5-based development board.

- Case design mock-up has been completed.

- Sampling a number of (Microchip) Super-I/O ICs (SCH5027, SCH5627) that are 3.3V & LPC compliant.

- Board layout and schematic are progressing into the final stages before review.

Maya Posch

Maya Posch

Andy Geppert

Andy Geppert

Christopher

Christopher

Hi

I think it's a very good project,? What state is it currently in? Are there any dates for completion, sale, etc.?

regards