Here's the project in bullet points.

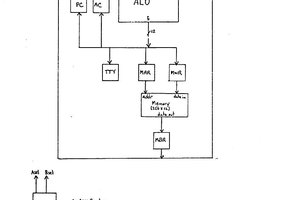

- A processor heavily inspired by the PDP-8.

- 16-bit word length without byte-addressable memory.

- Very basic instruction set, though much less basic than the PDP-8's — since we don't use core memory, the instruction set's defining decisions would be very different anyway.

- Accumulator architecture with a Page Zero emulating registers, like the 6502 or PDP-8.

- PDP8-style ‘microcoded’ instructions, which allow many small instructions in one, keeping the instruction set small but very flexible.

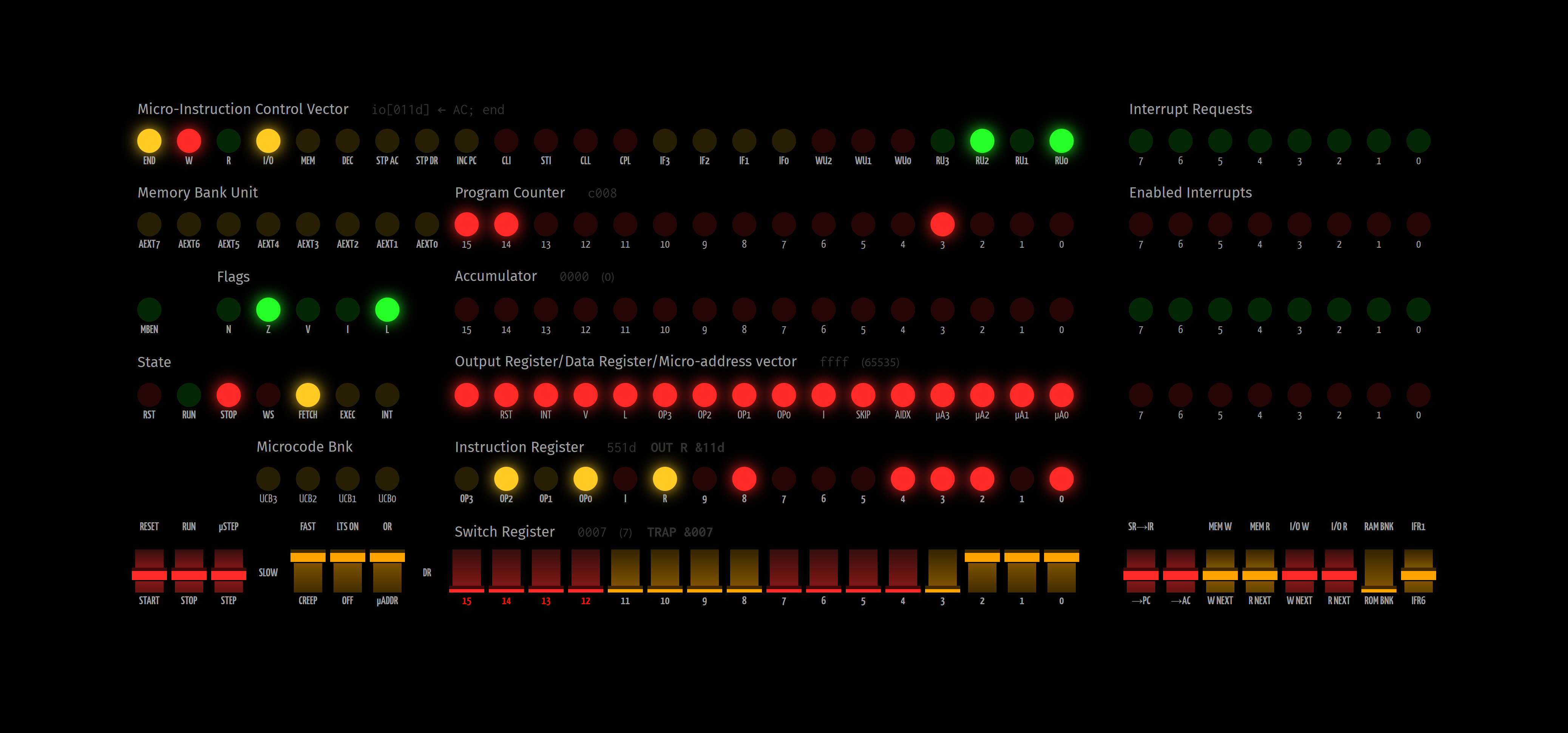

- Microcoded design. (in the modern definition of the term)

- 16-bit address space. A 2013 upgrade gave it a 21-bit paged address space. The 2019 architecture changes bring us to 24 bits of memory with 65C816-like bank registers.

- Interrupt support with a single interrupt. An expansion board increases this to 8.

- Front-panel support.

- Nearly all implemented with 74xxx ICs like those found in the Sixties and Seventies.

- A very simple operating system with basic abstraction and little else.

- A dialect of Forth is used as a combination OS shell and programming language.

- A retro logo.

- Hundreds of pages of documentation that nobody's ever going to read.

Alexios C

Alexios C

Fábio Gil

Fábio Gil

Pavel

Pavel

Wow! I want one!!