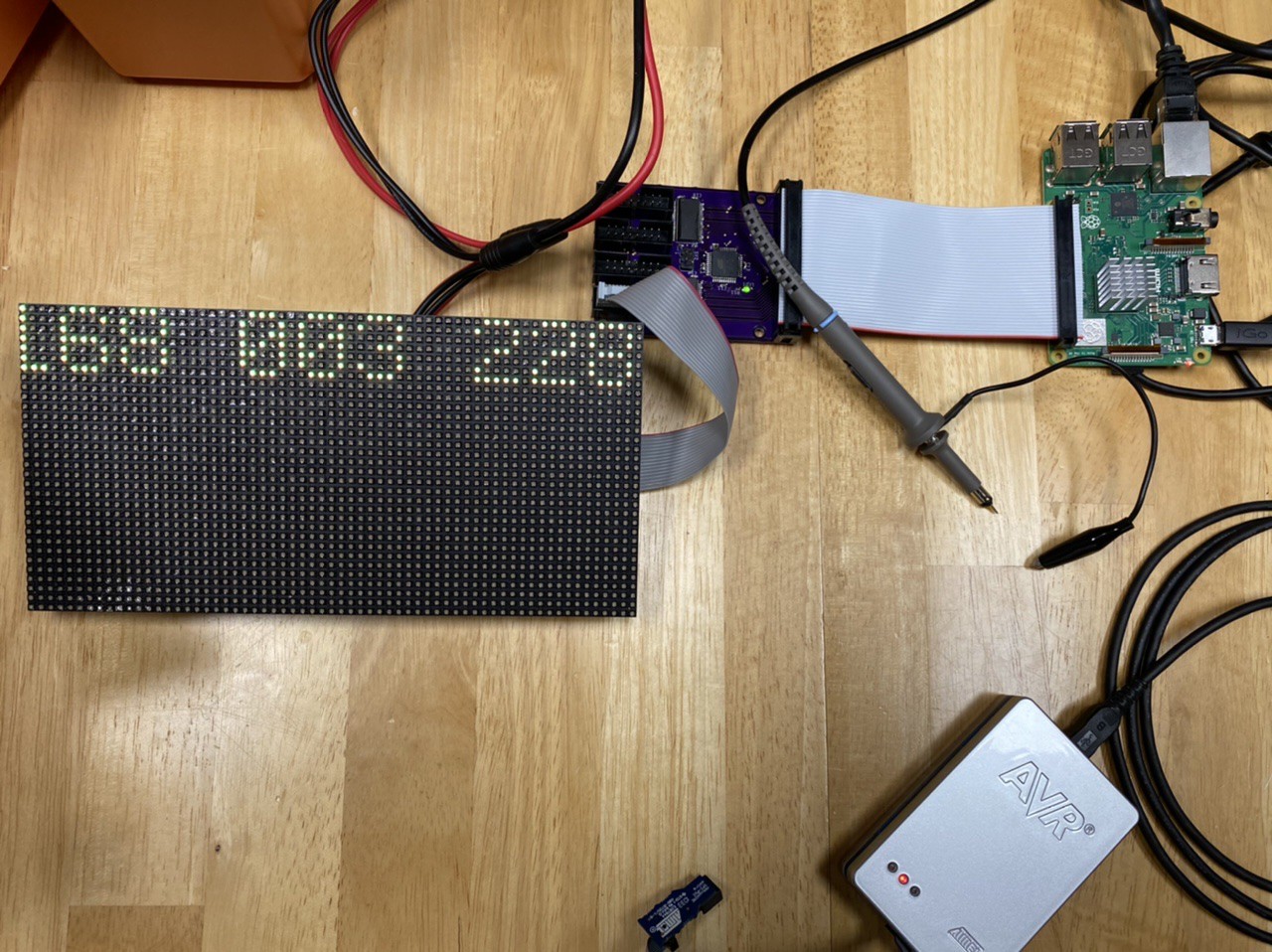

Uses Raspberry Pi DPI operating with 32MHz pixel clock. (32MHz is the clock limit of the XMega)

- Provides consistent panel timing regardless of CPU load.

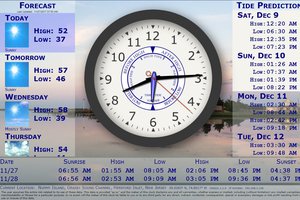

- Capable of drive large arrays with high refresh rate.

- Software driver derives array dimensions from Linux framebuffer device, pwm bits, and panel type.

- Panel CLK is produced by simple AND gate using pixel clock and DEN signal.

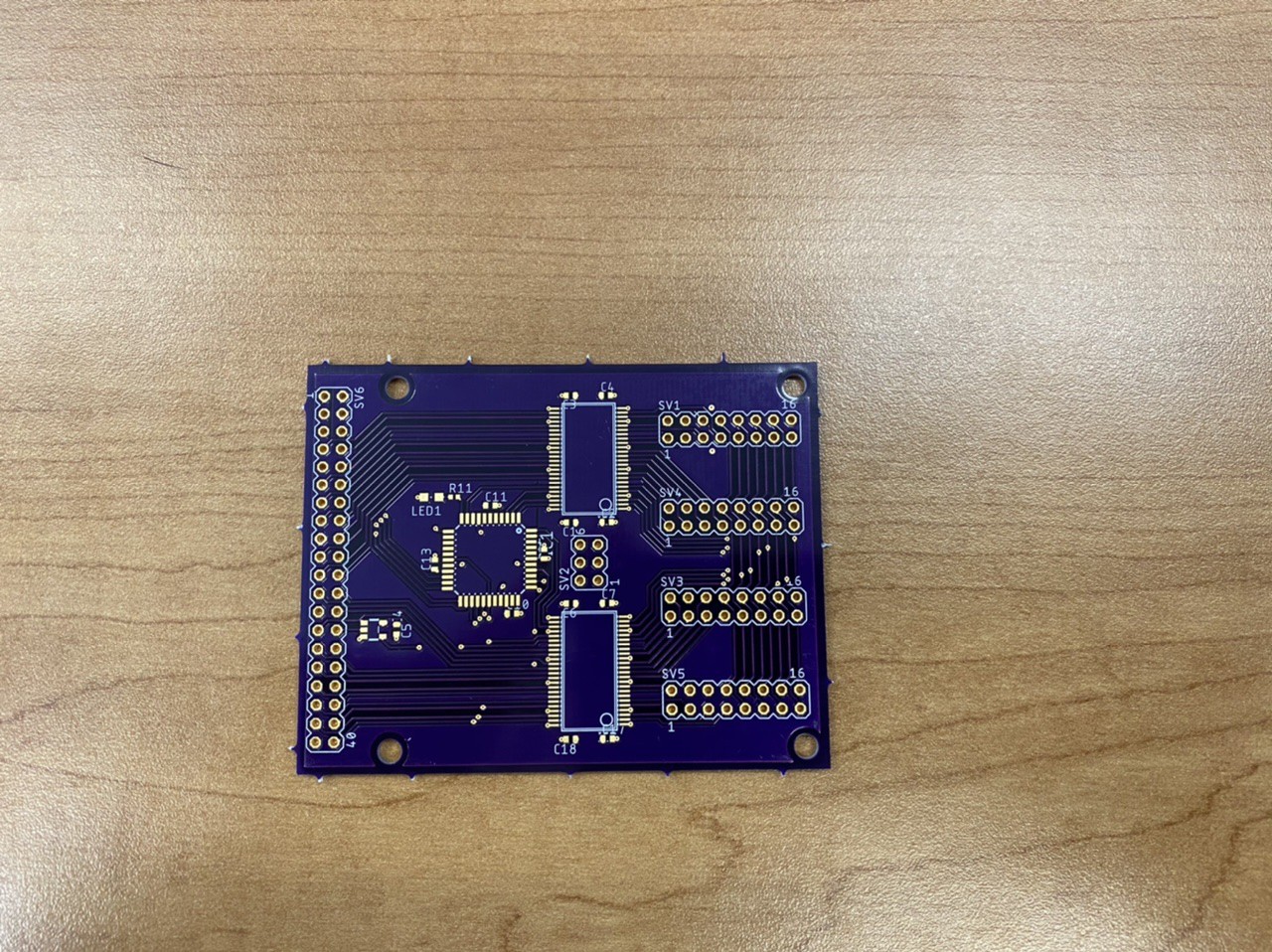

An Atmel XMega uses the pixel clock as it's external clock for synchronization.

- Use HSYNC edge to capture scan line data from first few bytes of each scan line.

- Generates PWM signal

- Outputs row select bits

- Generates LAT signal

Current Panel Configuration:

- 48 Qiangli Q3F32 v4.1 panels (64 x 64, not hub75 compliant)

- Canvas size: 768x256

- Refresh Rate: 82Hz

- Max OE active time: 49% at full brightness

Benchoff

Benchoff

Thomas Snow

Thomas Snow

ElecLab

ElecLab

Hi

Please help me to add slowdown gpio setting for my panels