-

Log#72 : The last post

04/12/2020 at 00:56 • 0 commentsBy whygee on Thursday 16 January 2020, 17:50 - Updates and news

This is the last post of this blog on this platform.

My hosting company discontinues its free blogging service so I have to move the archives to another place, probably http://yasep.org and/or https://hackaday.io/whygee

The development was abruptly halted some years ago due to a computer crash but the work on the the core is meant to resume someday, when the #YGREC8 is mature enough (this tune sounds familiar, I know).

Meanwhile, active development is continuing on http://ygrec8.com

See you on the other side !

20200412:

So this is the last log, it took about a week to move all the posts here and ponder on this retrospective...

The YASEP is a great project with a lot of flaws and awesome parts, that I hope will be revived when all the tools are finally ready. Apparently the most critical part is #YGWM Whygee's JavaScript Window Managerand this is what motivated me to come here and seek help.

A cycle ended and new ones are coming...

-

Log#71 : Progress with the SHL unit

04/12/2020 at 00:49 • 0 commentsBy whygee on Saturday 28 November 2015, 23:57 - Architecture

Work continues on the discrete YASEP, with frequent log posts on hackaday.io.

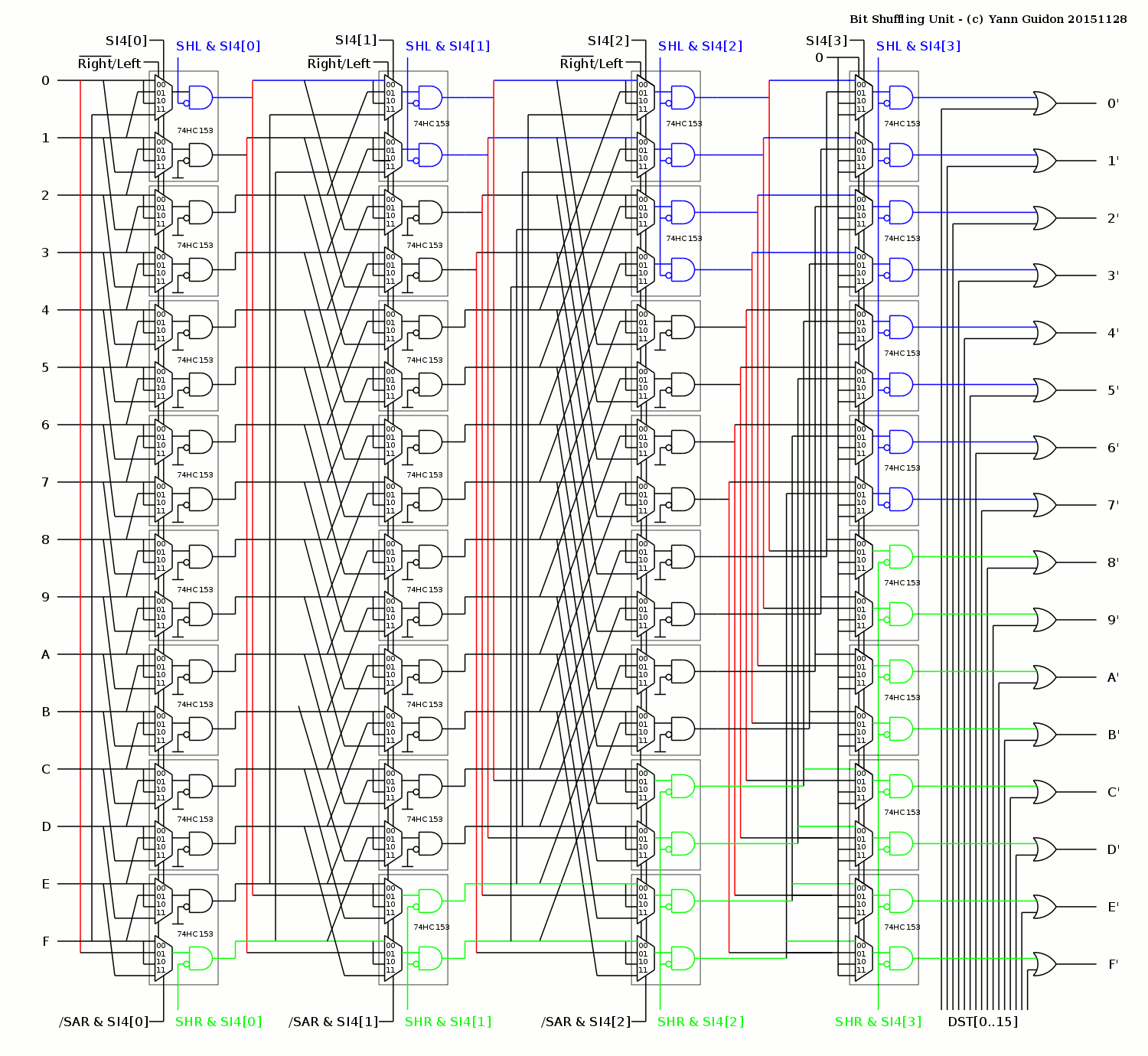

In one post, the SHL group's instructions have been reordered :

- 0 : SHR

- 1 : SHRO

- 2 : ROR

- 3 : SAR

- 4 : SHL

- 5 : SHLO

- 6 : ROL

- 7 : BSWAP

Then the structure of the SHL unit has been refined and a detailed diagram is drawn:

![]()

There is still some room for extra features and the I/E unit (Insert/Extract) might benefit from the unused inputs of the last MUX4 layer :-)

20200412:

By 2015 my development process shifted to the HaD.io platform and more tinkering occured here. A bit later, critical YASEP development files were lost in a HDD crash and I didn't have the force to rescue and resume the project.

This series of logs keep essential traces of design decisions that will help to reboot the project.

-

Log#70 : The Discrete YASEP

04/12/2020 at 00:42 • 0 commentsBy whygee on Thursday 5 November 2015, 04:05 - Updates and news

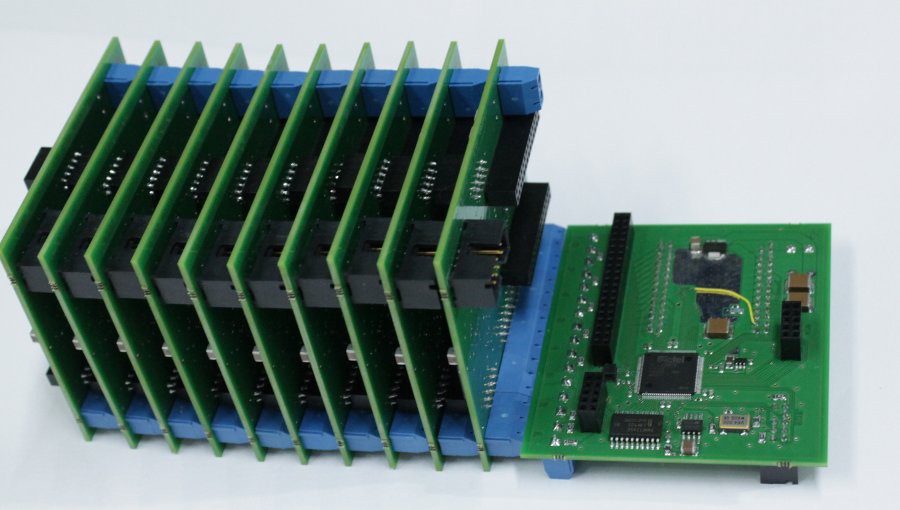

A parallel project has recently emerged : a YASEP implementation with SSI/MSI parts (74HC parts). The day-to-day progress is described on hackaday.io and the first prototype will also be the first working implementation of the new instruction set format.

20200412:

As usual, #Discrete YASEP forked in many sub-projects and couldn't make it to the functional state... but it explores many alternate architectures and started a fundamental process to re-design and re-think how I design.

With time, and as my list of projects shows, I'm still not good at keeping focus on a single project.

-

Log#69 : yasep2015

04/12/2020 at 00:37 • 0 commentsBy whygee on Tuesday 3 February 2015, 18:22 - Updates and news

A new year has begun, another milestone is created.

2014 saw the creation of the new, definitive instruction set format, as well as the start of new websites (http://ygwm.org and http://httap.org) and the early design of the miniYASEP. It is also possible to Flash the contents of a SPI memory on the WizYasep (Ethernet+FPGA) boards !

On the hardware side, several WizYasep boards are now deployed in Belgium. They are undergoing a harsh fire&ice treatment... More pictures can be seen on the public YGDES facebook page.

2015 will see that work continue on many fronts. The code base is currently pretty fragmented and unstable, the development version is barely usable and the previous version is not useful. To prevent this, all the files must become more independent, more modular, so work on one part does not break any other. For example, the main web site should be split into layers of increasing specificity ("base", "add-ons", "specific" modules...). Other CPU architectures should be easily supported in the near future !

At the same time, the website should move to a different server, which is an increasingly complex task. Modularity should help, for example by storing the base files on the ygwm server (some files are already in a different directory).

That's a lot of un-sexy work but the result should be worth the efforts !

20200412:#Mons2015 LED Screen ElectroSuperwas the project with all the #WizYasepboards. The YASEP core didn't make it to the FPGA but it worked. It incurred so much stress that YASEP2015 didn't make it as expected...

Yes my development practices clearly don't scale :-(

-

Log#68 : Latest tutorial

04/12/2020 at 00:29 • 0 commentsBy whygee on Monday 6 October 2014, 22:50 - Updates and news

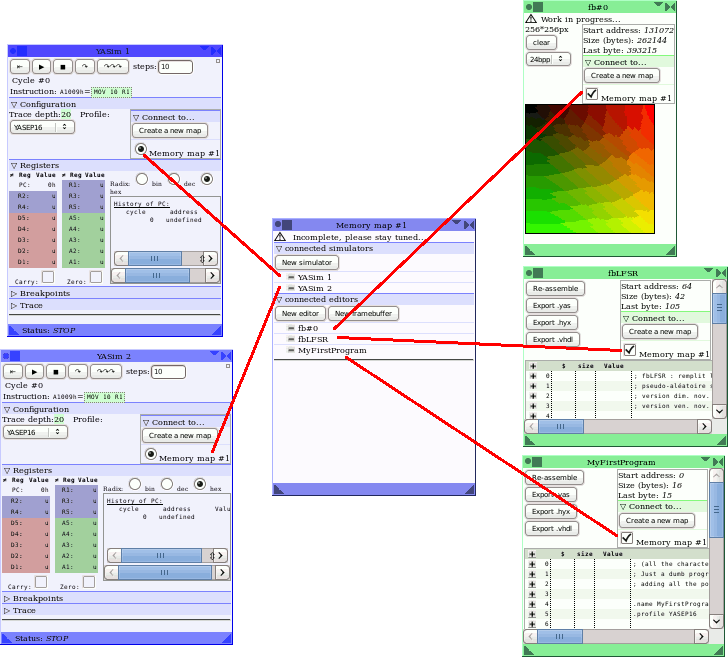

At last ! It was planned for two years at least but now it's done. The tutorial that explains the basics of using the YASEP simulator is written :-) I hope it will help the newcomers !![]()

You can read it at http://ygdes.com/~whygee/yasep2014/#!tuto/tuto_sim

-

Log#67 : The latest tool : direct programming of SPI Flash from the source code editor

04/12/2020 at 00:25 • 0 commentsBy whygee on Thursday 2 October 2014, 06:03 - Updates and news

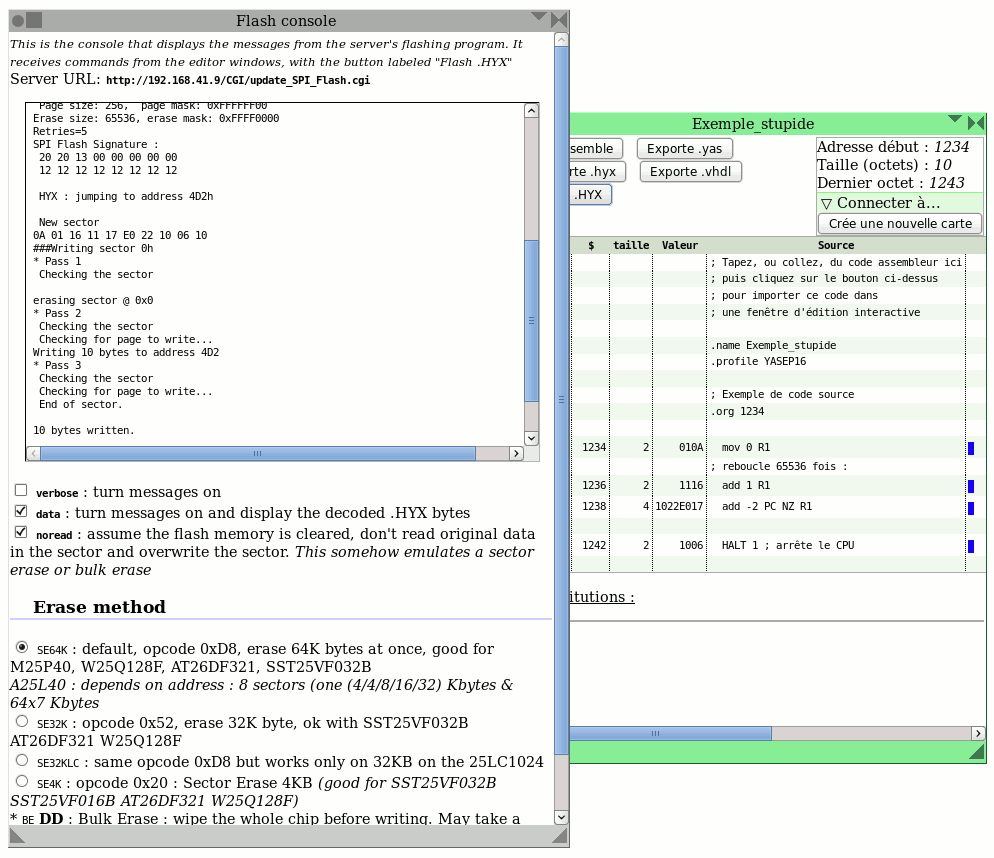

After a whole summer of work, I can now reach a new level of comfort. I can type my code and test it on the target within seconds by clicking on a single button in my browser.![]()

This is going to speedup development a lot ;-)

20200412:Look at #SPI Flasher:-)

#YGWM Whygee's JavaScript Window Manager needs a biiiig update and rewrite though :-/

-

Log#66 : The first PCB designed for the YASEP

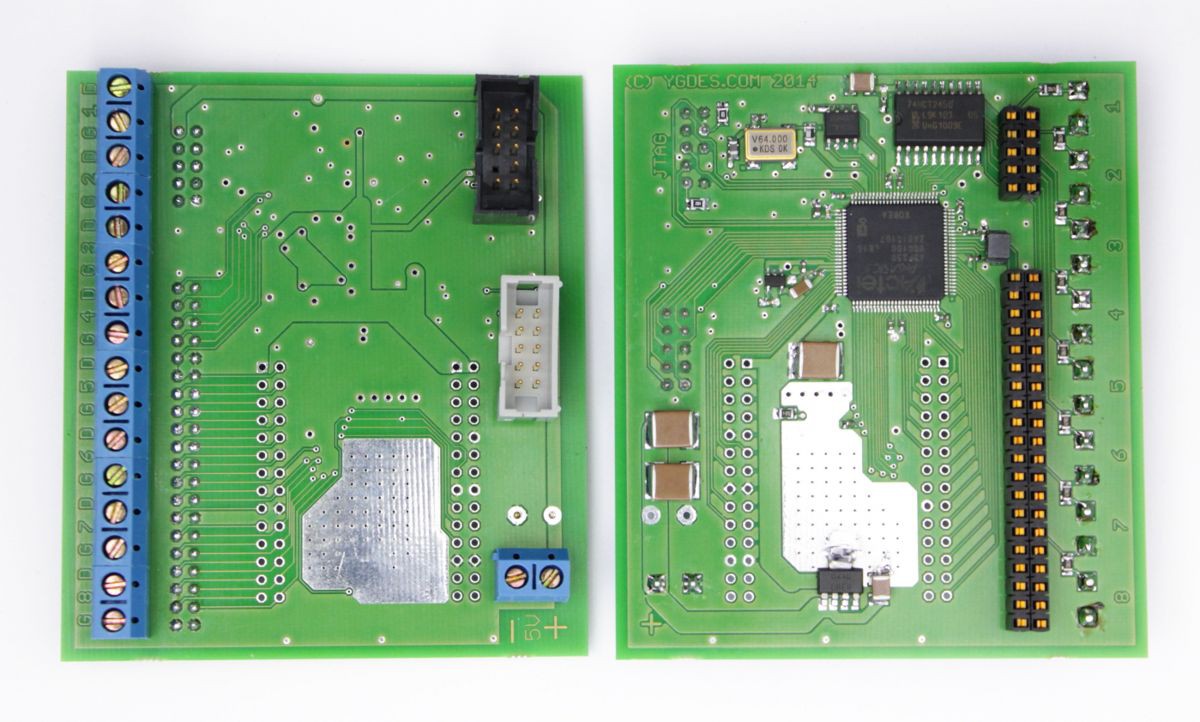

04/11/2020 at 04:52 • 0 commentsBy whygee on Sunday 27 July 2014, 12:09

My development time is dedicated to the "WizYASEP", a board containing a

FPGA (A3P250VQ100) and a Wiznet WZ5300 (high speed TCP/IP module). The first prototype board, using Dipole's services, is received and soldered :![]()

In the coming months, a batch will be produced and deployed. They will display videos on outdoor LED screens, see some previous similar projects at https://www.facebook.com/YGDES/

Thanks to its connectors, this small board is quite versatile and will find many applications, as is or with extension boards. The PCB itself can also be customised and adapted for specific projects.

Later, this board might become the next development tool in the YASEP ecosystem : equiped with a HTTP server (with HTTAP support), storage and probes, it will be a great in-circuit-emulator for other YASEP boards, such as the Actuino.

Due to time constraints, the first version will use an old microYASEP core (pre-2014) but the newer, faster and enhanced miniYASEP will follow in 2015, implementing the new instruction set format.

Oh, and Microsemi has released a QFP144 version of its Igloo2 FPGA. It looks very promising...

20200411:

The YASEP core never made it to the WizYasep board... yet....

Dipole closed shop some years later :-(

But the #WizYasepbecame a pretty good platform... I wish I had more stable tools though, because it is now stalled/shelved as well.

-

Log#65 : Baby steps

04/11/2020 at 04:45 • 0 commentsBy whygee on Monday 28 April 2014, 18:00 - Project

The YASEP's development progresses on many fronts so big results are not visible yet.I just started http://httap.org/ to document and publish the work on a TAP protocol over HTTP. A lot of multi-language development is going on, while writing articles on many connected subjects.

HTTaP is critical to rewrite the microYASEP from scratch with "Design For Test" in mind. In fact I'm investing time on debug/design tools in the hope that further development will be much faster, like on many occasions in the YASEP project !

I need to deliver a microYASEP VHDL core in a few months so it's pretty critical. The YASEP2014 architecture is still fresh in my head and there are so many details to correct. But some good things emerge anyway, such as my recent rewrite of the register set code (it now allows a "side channel" for address updates) or the removal of the ugly SWAP_IR flag (probably one of the most confusing aspects of the architecture that became finally pointless with the latest instruction format changes).

Translation (to spanish and german) is still on the table though no meaningful progress has occured lately.

As usual, pretty unstable snapshots are uploaded to http://ygdes.com/~whygee/yasep2014

whenever possible, so you can look at the evolution. -

Log#64 : Why ? Pourquoi ?

04/11/2020 at 04:42 • 0 commentsBy whygee on Wednesday 26 March 2014, 02:11 - Project

(Français plus bas)

I get asked this question often : Why design another CPU softcore ?I (Whygee) design electronic circuits to address the needs of my clients. The commercial solutions are often lacking in flexibility. It's often hard to find the right part number to match a project with its fixed feature set, including I/Os, speed, processing power, memory, peripherals... The chips may be cheap but the whole toolset can become expensive, and requires a Windows computer. On top of that, parts stock obsoletes quickly and long term availability is never certain (will the company go bankrupt or be bought next year ?).

On the other hand, the existing open source softcores do not solve all these problems. Some of them are little student projects with no continuous development, the toolset is often minimal, the requirements or usefulness might be arbitrarily specific, the documentation may be unsufficient...

The YASEP's purpose is not only to create a processor family but also develop the tools that I need and that may be re-used for other projects, in particular to design other CPU architectures. Many softcores need to reinvent the wheel and can't afford to make a sleek integrated IDE. The YASEP is also a reusable modular toolset.

Today, I can wrap the YASEP around customer projects' needs, instead of warping my technical solution around some manufacturers' constraints. In fact, I can solve most of my microcontroller needs and I stock only a handful of FPGA part numbers. If the YASEP solves my problems, it might also solve yours and that's why I have open sourced all the necessary resources.

You will find some background on this project in these presentations: EHSM2012 (english) and JMLL2012 (french).

On me demande souvent : Pourquoi créer encore un autre microprocesseur ?Mon métier est de réaliser des circuits électroniques pour répondre aux besoins de mes clients. La plupart du temps, les produits commerciaux ne sont pas assez flexible. Il est difficile de trouver la bonne référence de circuit intégré avec les bonnes caractéristiques, qui dispose du bon nombre d'entrées-sorties, qui soit juste assez rapide, avec juste assez de mémoire et les bons périphériques... Les puces sont souvent abordables mais l'ensemble des outils de développements peut coûter très cher, surtout si on doit acheter un ordinateur dédié sous Windows. En plus, les stocks de composants deviennent vite obsolètes et la pérennité à long terme n'est jamais assurée (est-ce que le compagnie va faire faillite ou être rachetée l'année prochaine ?).

D'un autre côté, les softcores open source ne résolvent pas tous ces problèmes. Certains de ces projets sont abandonnés, les outils de développement sont incomplets ou beaucoup trop restrictifs, la documentation est insuffisante...

L'objectif du YASEP n'est pas juste de créer une famille de processeurs mais aussi de développer des outils dont j'ai besoin et qui peuvent être réutilisés par d'autres projets, en particulier pour concevoir d'autres architectures de processeurs. Beaucoup de projets de softcores doivent réinventer la roue et ne peuvent pas investir le temps pour créer une interface utilisateur aboutie. Le YASEP est donc aussi un ensemble d'outils modulaires et réutilisables.

Aujourdhui, je peux adapter totalement un YASEP pour répondre aux besoins de mes clients, au lieu de plier mes projets aux contraintes des fabricants. En fait, le YASEP convient pour la plupart des projets où un microcontrôleur est requis et je peux garder en stock un nombre plus réduit de références de circuits intégrés. Et si le YASEP résout mes problèmes, il pourrait aussi vous aider et c'est pour cela que je diffuse tous les outils avec une licence libre.

Pour plus d'informations sur la génèse de ce projet, regardez ces deux présentations : EHSM2012 (anglais) and JMLL2012 (français).

-

Log#63 : Flag polarity

04/11/2020 at 04:07 • 0 commentsBy whygee on Thursday 13 February 2014, 05:12 - Architecture

RISC does not like status flags, but it was determined to be a necessary evil for the YASEP. Yet something more important than scheduling has confused the flags : their values. They have often created more problems than they solve because I always remember the wrong ideas about them, or I forget that I changed a detail.The Carry flag

In the beginning, it's very simple : the carry flag is set to 1 if the result of an addition generates a carry (overflows). It's valid both for signed and unsigned, thanks to the magic of 2s complement.

Then comes the subtraction : a little electronic quirk made me chose to not complement the borrow flag when there is a borrow. So the flag is set when there is no borrow. It's not usual but it saves maybe half a nanosecond and it's hidden by the symbolic treatment of the assembler with the "BORROW" condition.

Comparisons and MIN/MAX are even more confusing and I never know what to expect or how to come with the right thought process... The fact that the operands can often be swapped does not help !

(to be continued)

The Equal flag

This one just changed polarity, again. So now it's simple : it is set to 1 when the operands are equal.

The value's calculation is a bit subtle : it reuses the ROP2's XOR layer, but since CMP also performs a SUB in parallel, the SND operand is negated, so it's actually a XORN.

Additionally, the reduction was done by a OR, and now it's done by AND (otherwise it won't work).

The documentation at http://yasep.org/#!doc/reg-mem#equal is updated with a new diagram. This time, I should not forget the subtleties anymore...

20200411:Oh my, here I go again with these "details"...

SeeLog#62 : Zero becomes Equal and Log#46 : The Zero status flag

YASEP News archives

A backup of the blog before the host erases it. A good opportunity to review the development, twists and turns of this ISA !

Yann Guidon / YGDES

Yann Guidon / YGDES