-

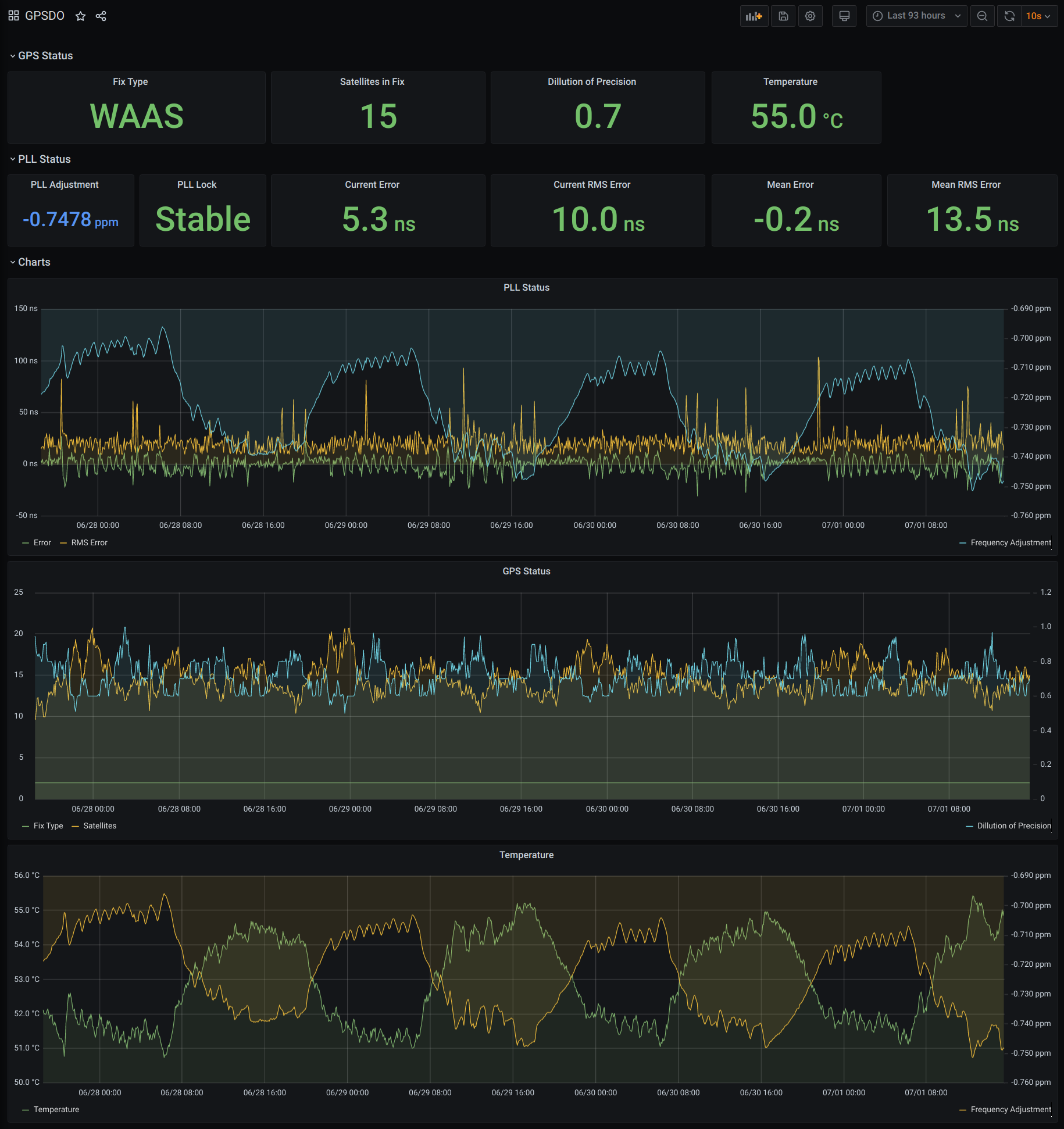

Multi-day Performance

07/01/2020 at 20:33 • 0 commentsHere's the tracking performance over 93 hours. The graphs demonstrate both the frequency drift over temperature and the much more gradual drift from aging. The enclosure appears to sufficiently blunt the cyclic temperature changes, and the PID loop remains stable despite the offset jumps when the GPS recalculates its coordinate fix. I plan to eventually move the antenna outdoors which should reduce the GPS fix errors.

-

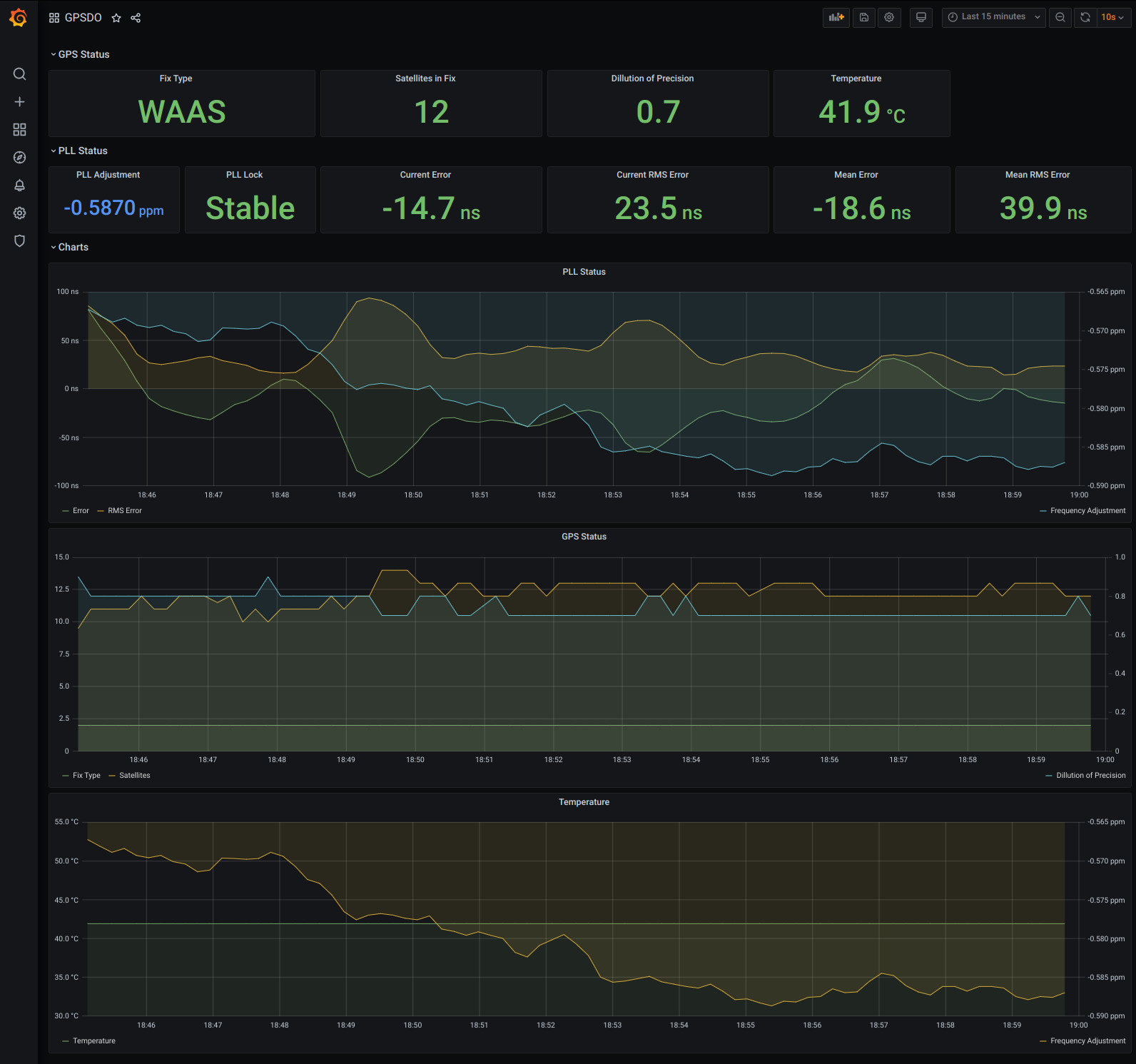

TCXOs are simply better...

06/28/2020 at 15:23 • 0 commentsAfter building an enclosure for the board and allowing it time to settle, the clock stability is remarkably improved over the previous revisions. Here's the settled performance over 12 hours:

![]()

The enclosure slows the temperature ramps sufficiently enough that I've been able to relax the proportional coefficient in the PID controller which makes the VCTCXO adjustments far smoother.

-

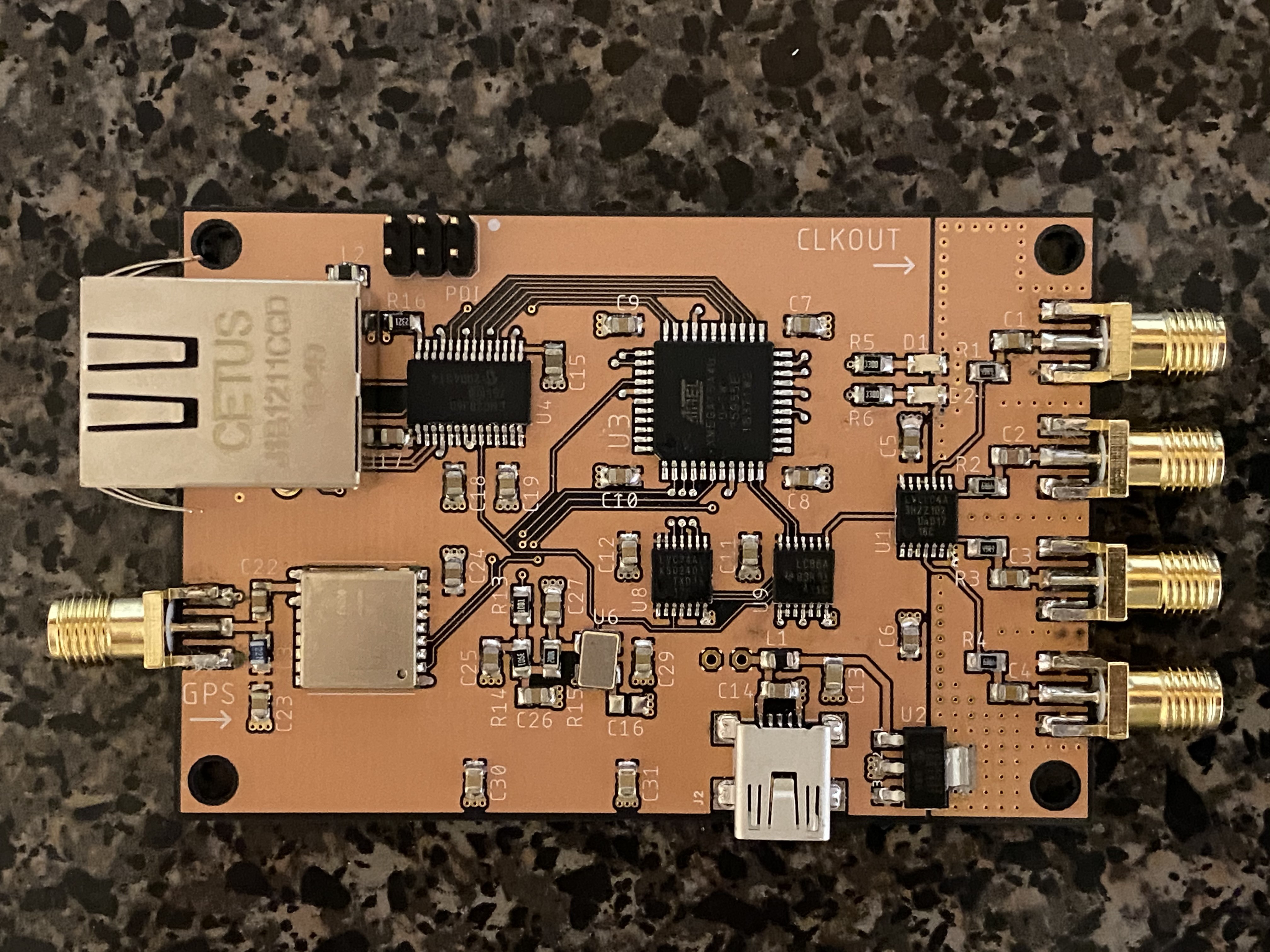

Assembled final boards.

06/27/2020 at 00:00 • 0 commentsI've assembled the final revision of the GPSDO board. I have recalibrated the XMega firmware for the new board am presently performing a 48-hour burn-in test.

![]()

-

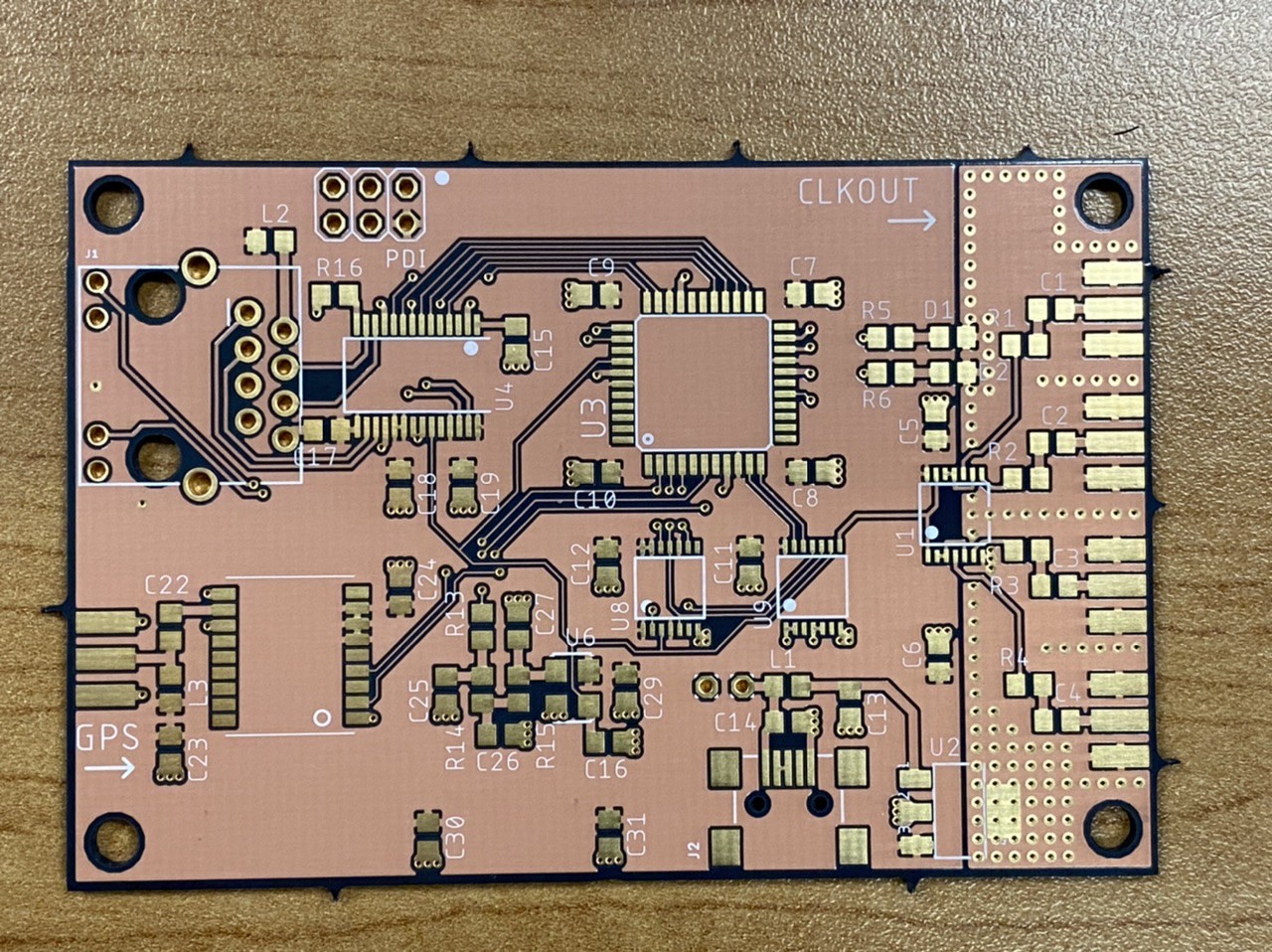

Final boards arrived.

06/22/2020 at 17:54 • 0 commentsFinal boards arrived today. I'll assemble them once the last parts arrive.

![]()

-

Control Loop Improvements

06/17/2020 at 02:46 • 0 commentsI noticed over the past several days, that there were occasionally momentary oscillations in the PLL feedback values. The cause turned out to be an overlooked pole in the loop transfer function: the relative PPS offset error itself. The PPS offset error is ultimately an integral with respect to the crystal frequency adjustment. I solved the instability by changing my control from a simple integral into a full PID controller. To improve the initial lock time I used two sets of coefficients:

- Initial Lock

- Cp = 3.333 = (10ns / 1.5ppb) / 2s

- Ci = 0.104 = (10ns / 1.5 ppb) / 64s

- Cd = 0

- Stable Lock

- Cp = 1.666 = (10ns / 1.5 ppb) / 4s

- Ci = 0.026 = (10ns / 1.5 ppb) / 256s

- Cd = 0

The derivative coefficients ended up unused because the P and I coefficients provided sufficient performance by themselves.

In addition to changing the loop controller I also overclocked the xmega to 50MHz (2x 25MHz) to increase the error resolution and ultimately reduce the loop tracking error.

I also reduced the magnitude of thermal perturbations by covering the VCXO in hot glue and cooling the bottom of the board with a low speed fan. This reduces the overall operating temperature will preventing sudden jumps in frequency from stray air currents. The final board will have a VCTCXO and be kept in an enclosure which will further reduce thermal sensitivity.

![]()

- Initial Lock

-

Final Board Revision

06/12/2020 at 15:40 • 0 commentsSince the current board layout and software have proven to work, I've replaced the SiT 3807 VCXO with the SiT 5156 VCTCXO on the final board revision. The TCVCXO is considerably more expensive which is why I performed the prototyping stage with the less expensive VCXO.

The new boards should arrive in a few weeks.

-

XMega Software Improvements

06/07/2020 at 00:39 • 0 commentsAfter observing the PLL performance over several days it became obvious that both the tracking accuracy and the loop stability could be improved. As a result I made the following changes:

- Added logging of PLL frequency correction.

- Increase effective DAC resolution to 16 bits through offset twiddling.

- Reduce PLL overshoot by applying adaptive gain based on error magnitude.

- Fix offset in error estimation by shifting clock bins 0.5 cycles to match ideal signal alignment.

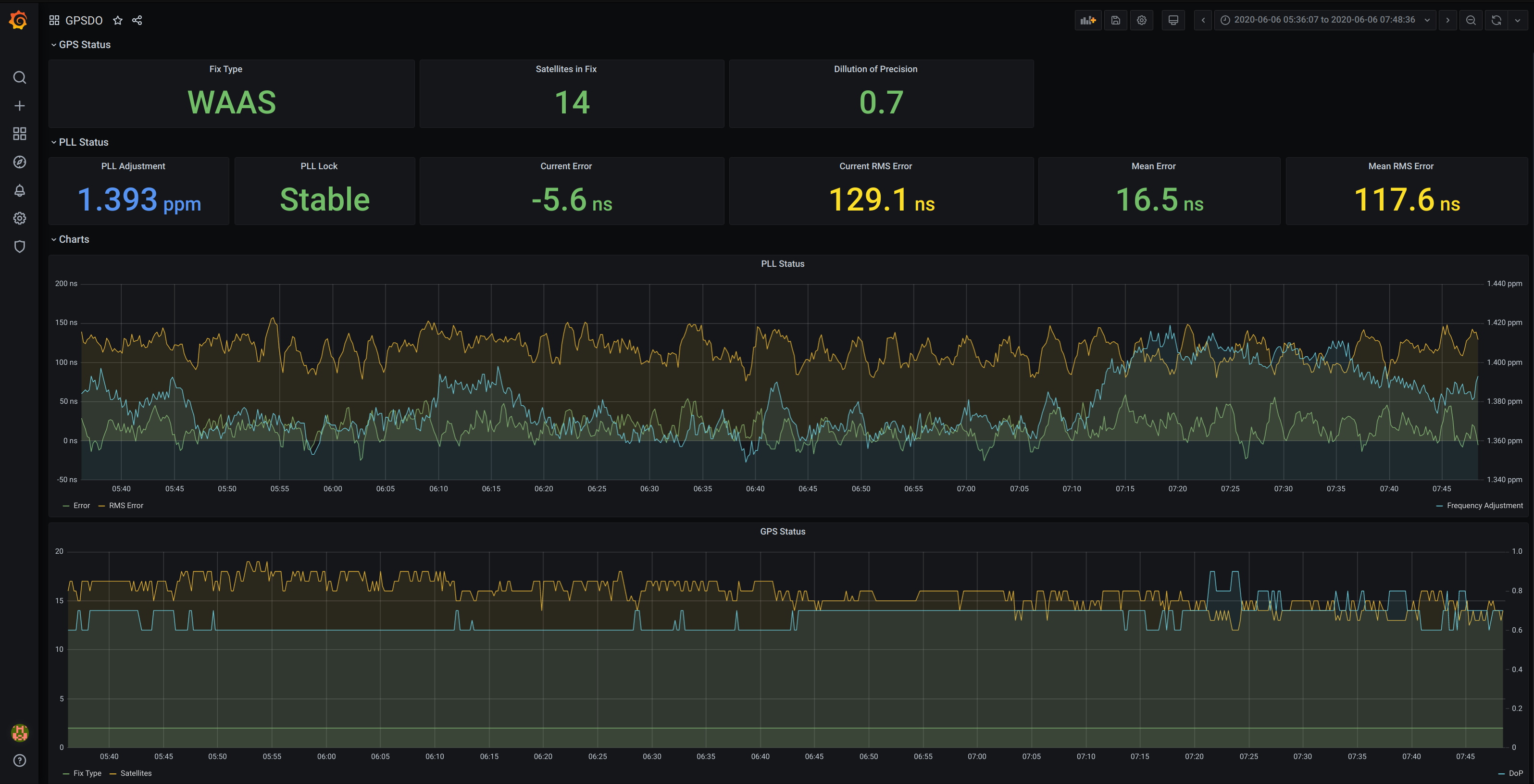

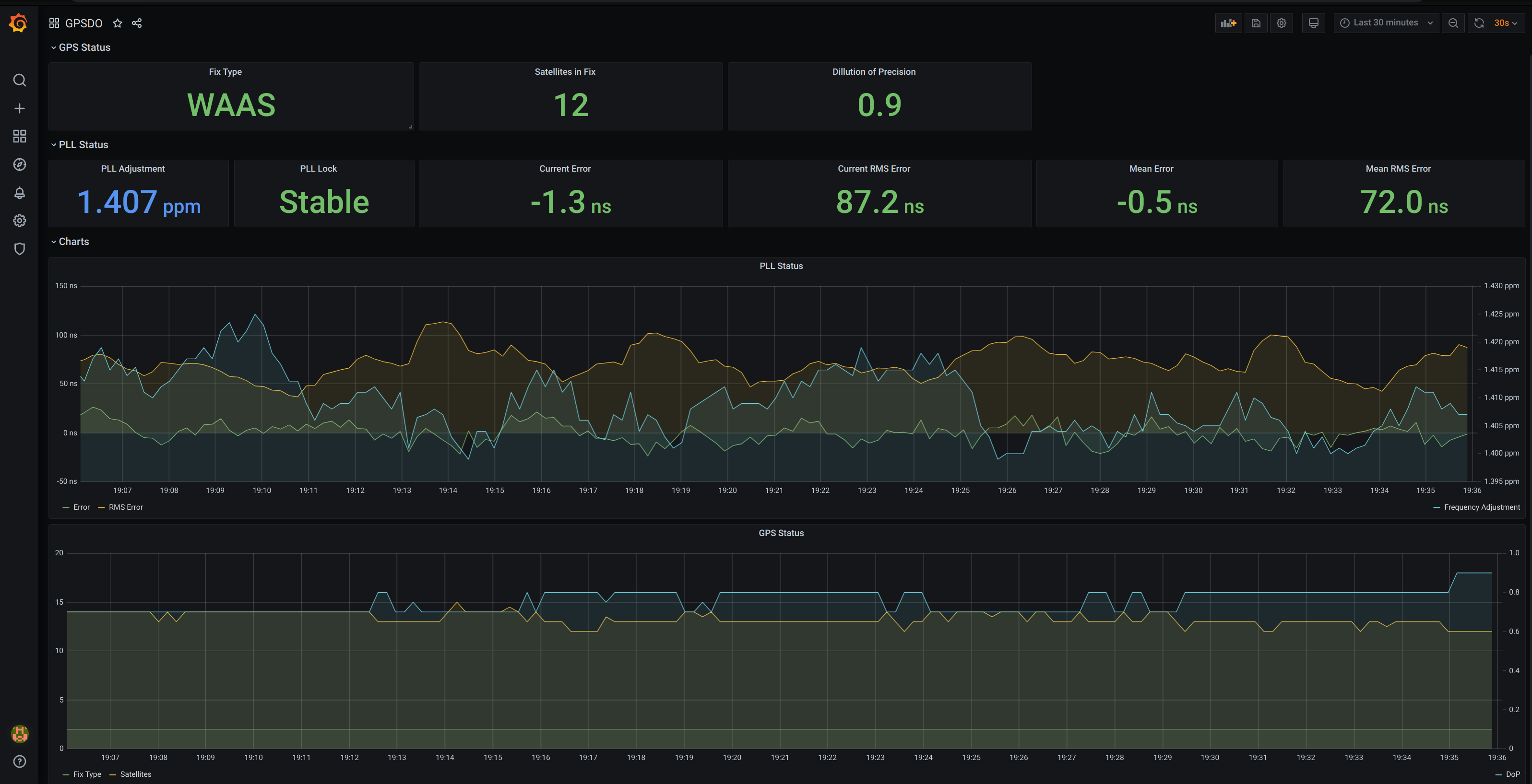

Before:After: