-

TUTOR Running on 5CEFA2F23 card

08/11/2020 at 00:08 • 0 commentsGot TUTOR 1.3 running on the 5CEFA2F23 Cyclone V FPGA card. on the RETRO-EP4CE15 base card. Needed to fix the address decoder to use 16KB of space for the ROM.

Code is up in GitHub.

-

S Record Load Character Drops - Sometimes

07/11/2020 at 19:18 • 0 commentsI am getting character drops when loading the S Records - but only sometimes. I had a similar problem with MIKBUG s-record loads. I solved it there by disabling echo on loads. There is no ECHO on TUTOR when the file is loaded from the ACIA as the second port.

I think there may be a workflow that works reliably.

-

Jeff Tranter's Demo Video

07/11/2020 at 10:51 • 0 commentsJeff has a nice video demonstrating his build of the TS2. The FPGA card software is identical.

-

TUTOR Loading S-Records Timeout

07/10/2020 at 17:59 • 0 commentsI tried to load a program using the S-Record loader built into the Tutor monitor using the LO command. The problem was that the board immediately timed out. The reason is TUTOR has a software loop which times out the load in 10 seconds and the FPGA CPU is much, much faster than the 8 MHz 68000 in the TS2.

The "real" 68000 chip took 4 clocks to access memory (if DTACK* is grounded). The VHDL core takes one clock at 25 Mhz. That's a scaling factor of 4 for the single clock time and 25/8 for the raw clock itself. Thus, the VHDL design runs 12.5 times as fast as the original design.

The timeout loop was easy to find in the LST file and it's in two places:

4490 9fe2 243C 0003 MOVE.L #LTIME,%D2 | D2 = 5 SEC DEADMAN @ 8MHZ 4490 20C8 4557 a06a 263C 0001 MOVE.L #LTIME/2,%D3 | D3 = 2 1/2 SEC @ 8MHZ (CHARATER TIMER) 4557 9064

The address of the offsets in the .MIF file is shifted right by two since the MIF file is for 16-bit data. It was easy to manually edit the MIF file and fix the two locations. Also, the base address of 0x8000 needs to be subtracted.

- (0x9fe2-0x8000) / 2 = 0x0ff1

- (0xa06a-0x8000) / 2 = 0x1035

Here's the locations I patched in the MIF file.

0FEA: 48E7 7090 6100 FCAA 2648 6100 FC92 243C 0033 20C8 614A 6704 615C 60F8; ^^ 1030: 671C 0C01 0020 6D14 1C81 263C 0011 9064 220E 928D 0C41 0050 6A02 528E; ^^Here's what it looked like after the patch was installed:

009FE0 FC 92 24 3C 00 33 20 C8 61 4A 67 04 61 5C 60 F8 ^^ 00A060 67 1C 0C 01 00 20 6D 14 1C 81 26 3C 00 11 90 64 ^^The timeout is now about 4 seconds.

-

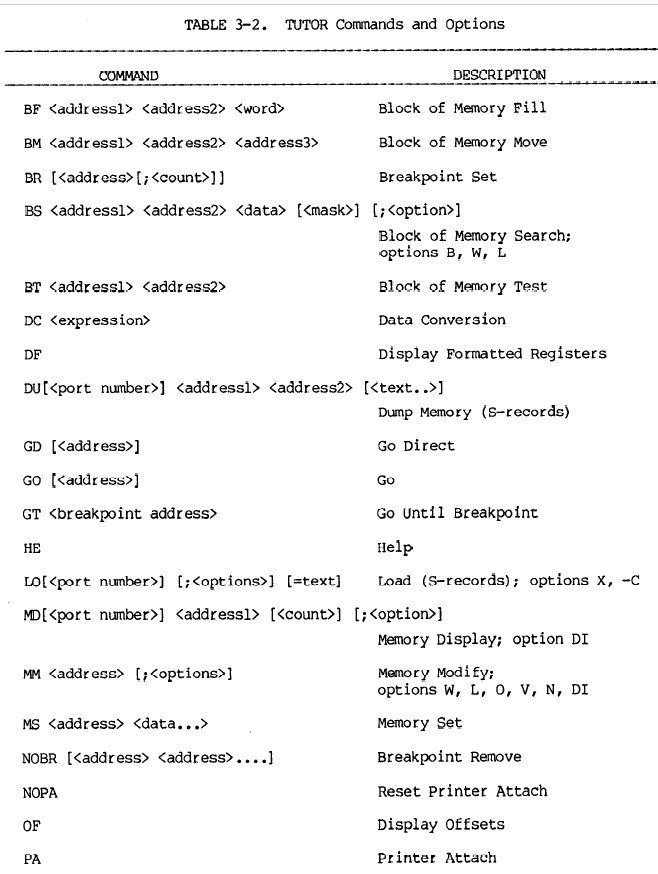

TUTOR Command Set

07/10/2020 at 15:00 • 0 commentsThe Motorola MC68000 Educational Computer Board (MEX68KECB) User Manual has the command set for TUTOR in Section 3.6. Here's a snapshot of the commands:

-

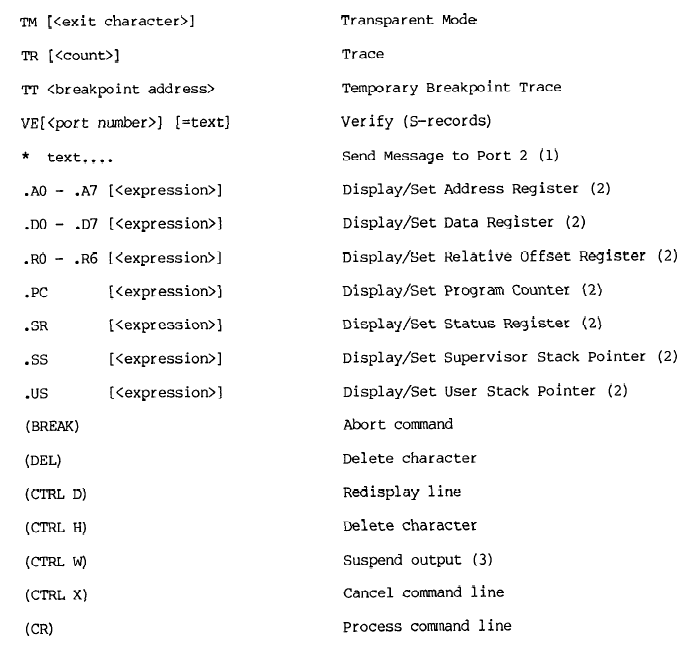

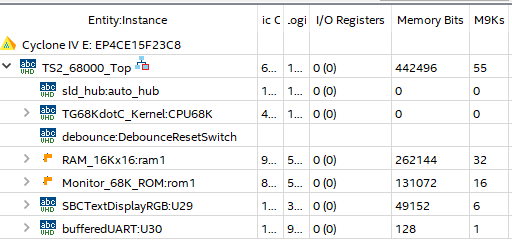

FPGA Resources - Running TUTOR Monitor

07/10/2020 at 13:42 • 0 commentsI wanted to run Jeff Trantor's build of the TUTOR monitor since it has a lot more features than the TS2BUG. The User Manual for the MEX68KECB details the commands for TUTOR.

It requires more ROM resources than the TS2BUG monitor design used. The TS2BUG monitor uses less than 4 KB of memory. The TUTOR monitor requires 16KB.

The FPGA has 56 of 1 KB blocks so there is enough RAM space to have 32KB of SRAM and 16KB of ROM and still have a full-featured VDU (color attributes per character and 256 characters).

The resource use (with the 4 KB TS2BUG) is:

That breaks down to:

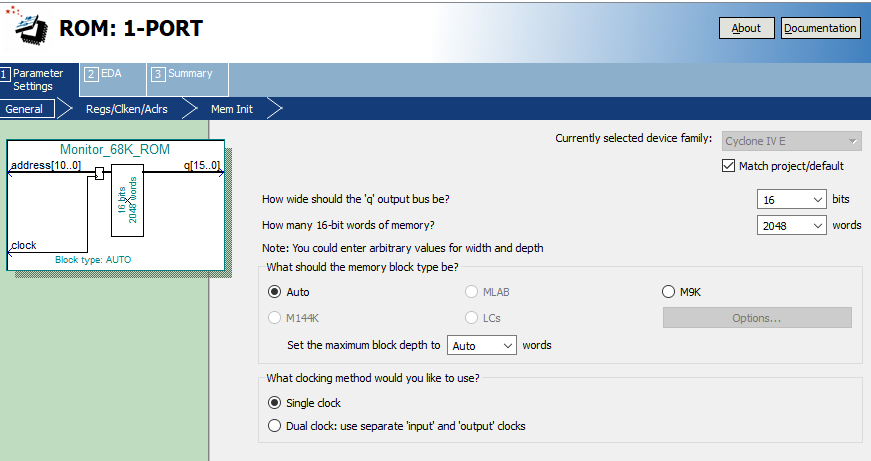

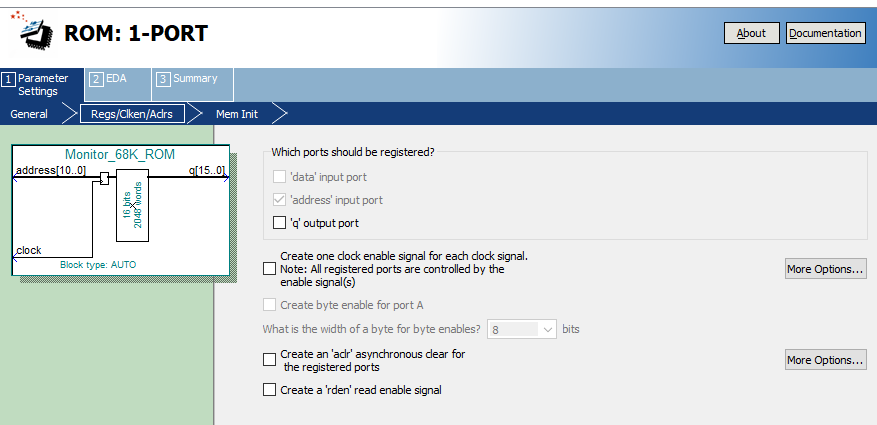

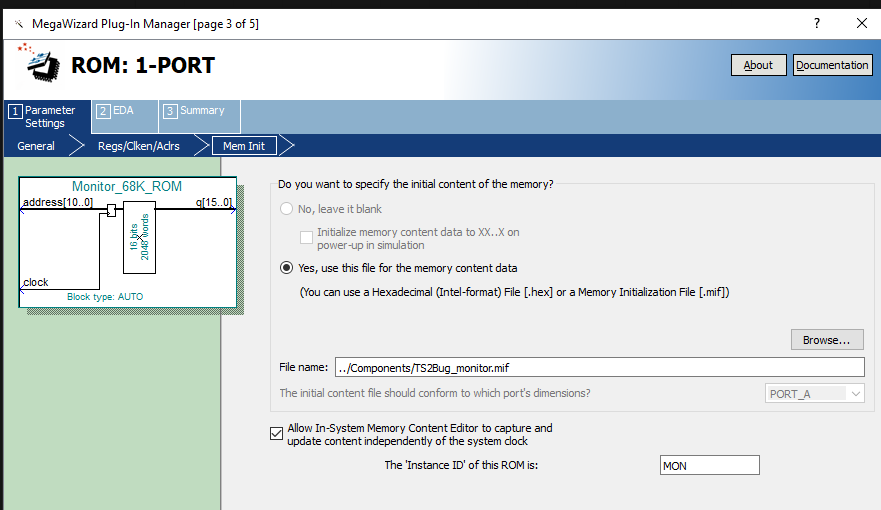

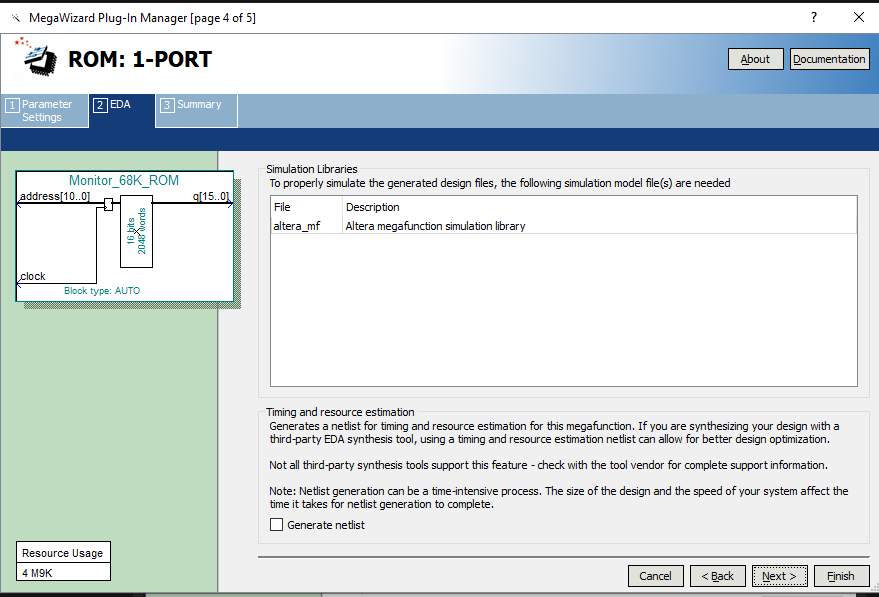

The ROM megawizard values are:

To make the change in the MegaWizard requires setting the memory size to 8K of 16-bits and changing the MIF file to the TUTOR monitor. That leaves a single 1K block of SRAM in the FPGA.

I also had several changes to the ROM address decoder to use less address bits. This will still be backwards compatible with the TS2MON.

Both the TS2TBUG and TUTOR run without re-compiling of Jeff Tranter's builds. All that is needed is converting the S record or HEX file to an Altera MIF file (process described in previous BLOG).

TUTOR 1.3 now works!!!

Loaded to GitHub here.

-

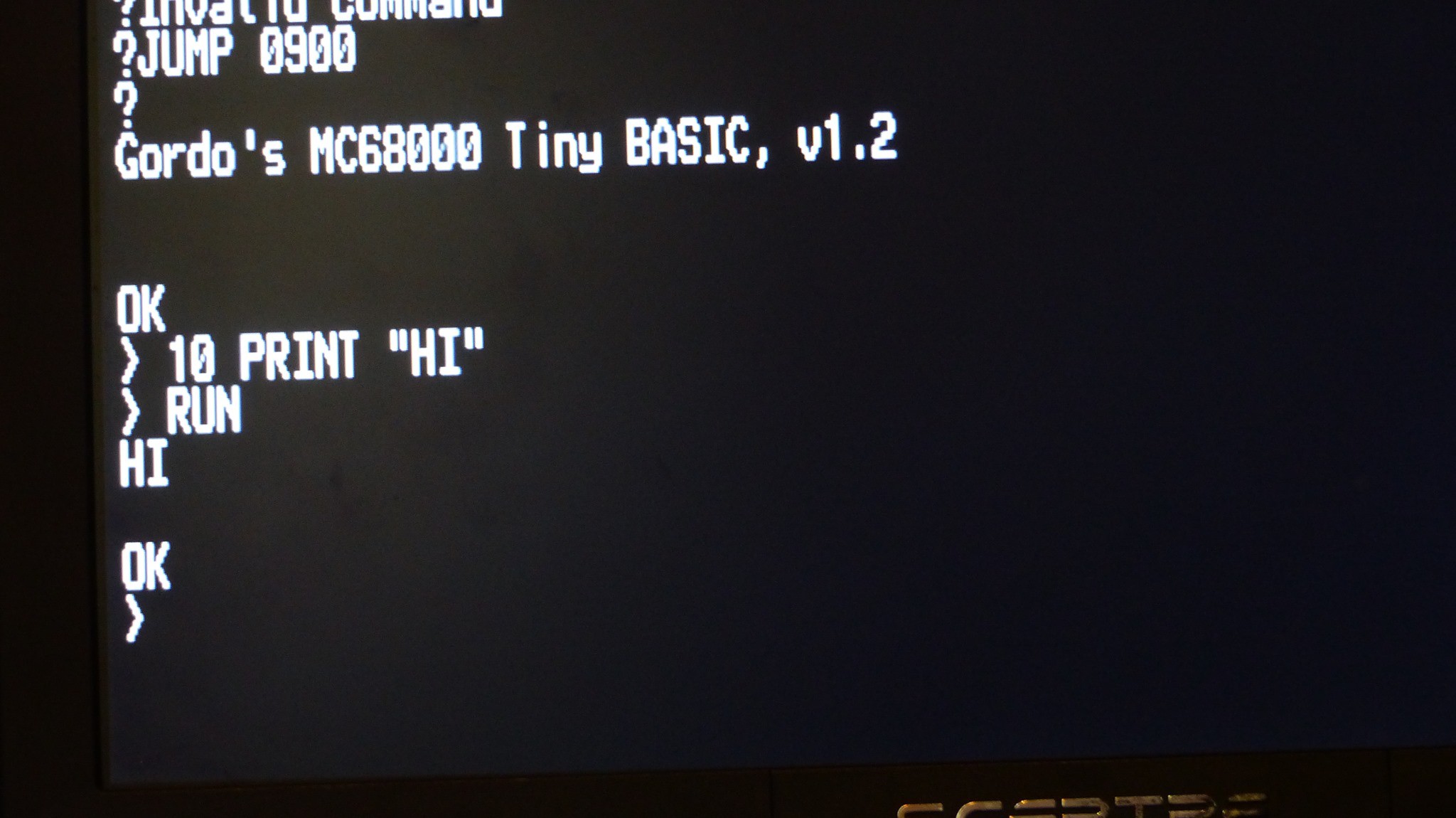

Loading/Running Tiny BASIC

07/10/2020 at 11:53 • 0 commentsThe Motorola MC68000 Educational Computer Board (MEX68KECB) has a Tiny BASIC that is already assembled. Since the card is compatible with my FPGA design it loads nicely.

![]()

- Type LOAD on VDU port

- Waits on S-records from the ACIA port

- Running PuTTY on the PC connected via USB to Serial to the FPGA card

- Copy/paste S1/S9 records from TBI68K.HEX into ACIA port

- JUMP 0900 to run

- Type LOAD on VDU port

-

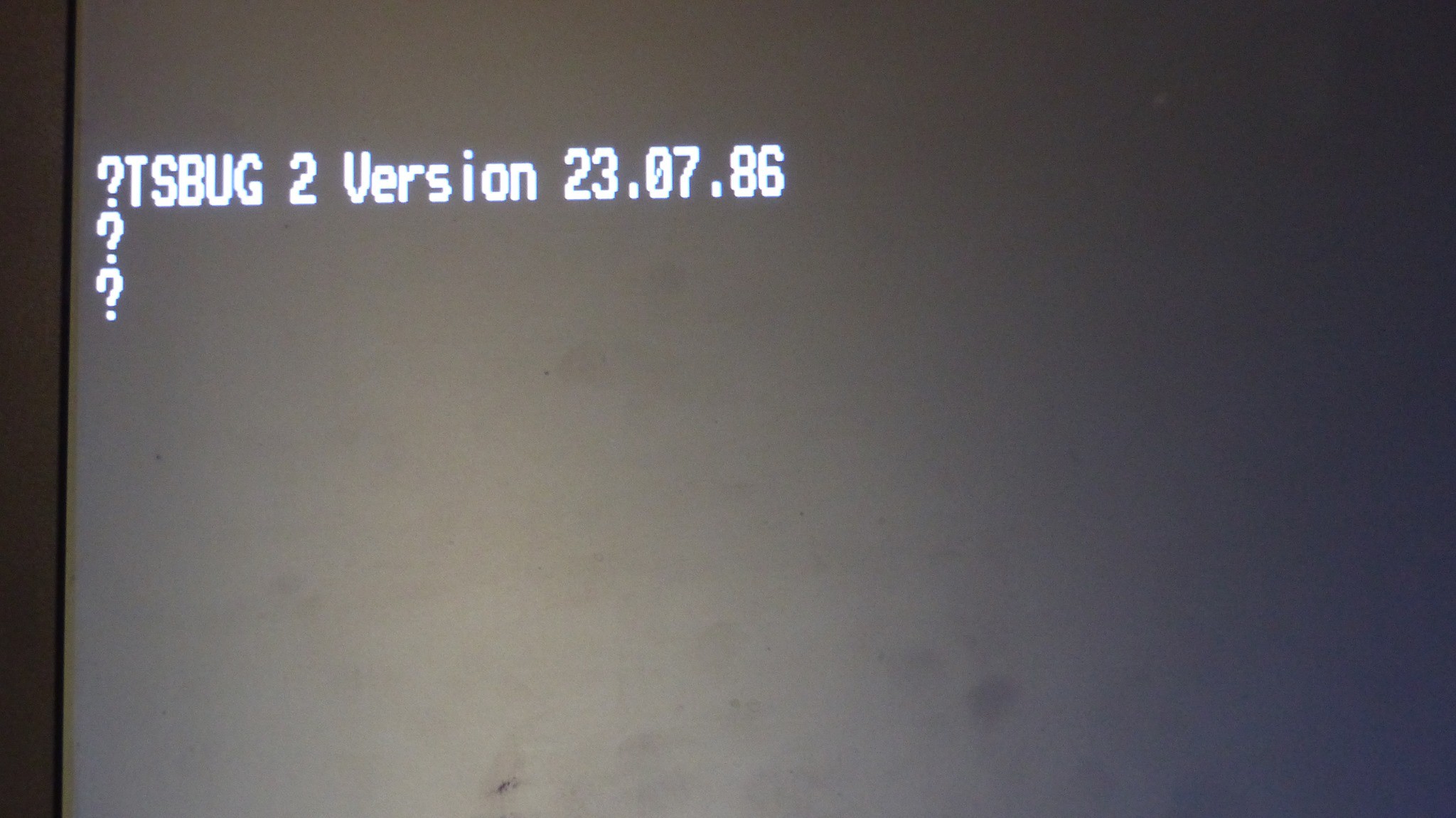

Up and Running

07/10/2020 at 11:32 • 0 commentsAfter a few days of messing around with the FPGA top entity, I got it running and was rewarded with the TS2BUG prompt on the VDU.

![]()

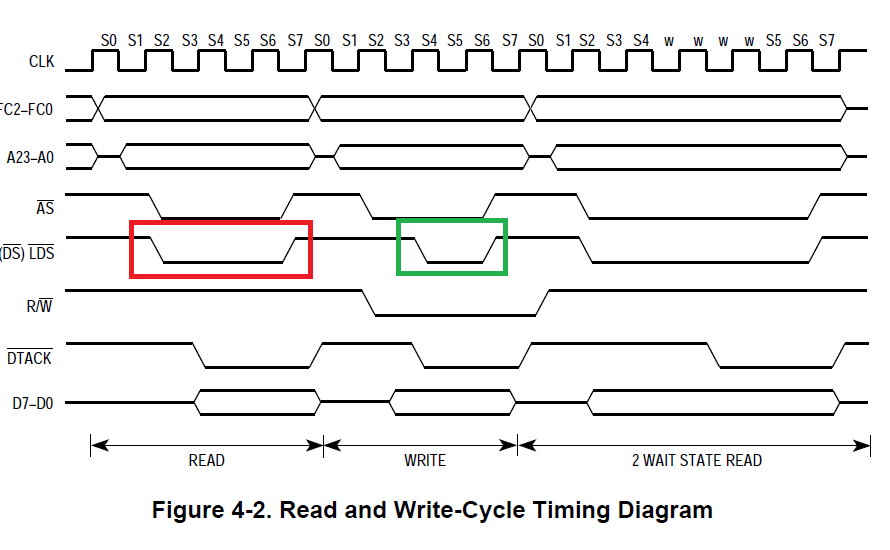

Lesson Learned

FPGA implementations of CPUs rarely match the pins of the original part. They are typically poorly documented where it comes to the changes or how to interface to the CPU. Sure, address and data match and are easy. The 68000 Hardware User Manual helps for signals that are in common but doesn't help for missing/added signals.

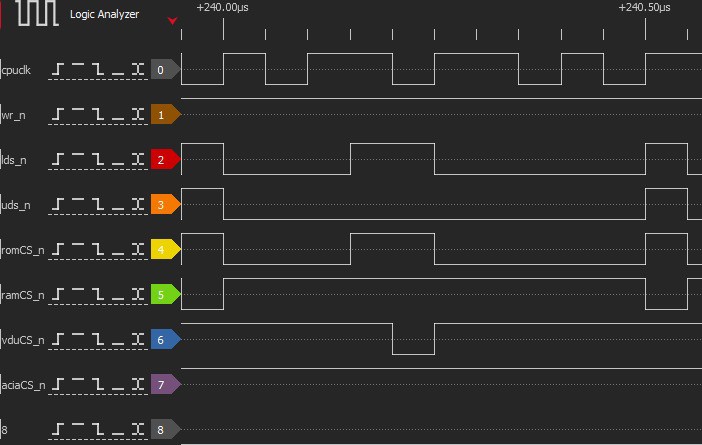

Just like the 68000, the VHDL code has lower and upper Data Strobes (UDS* and LDS*). The relationship to the clock is not documented. For the real 68000, the Data Strobes can be used to gate writes since the data is valid before DS drops and remains valid after DS rises. That is shown below where the red box is the data strobe for reads and the green box is the data strobe for writes. Note the write strobe is shorter.

![]()

That's not the way it works with the VHDL code.

In the end there's nothing like hooking up a logic analyzer and looking at the signals to straighten things out.

![]()

Turns out gating the CPU clock (low) with the Data Strobe works for writes. Took a while to figure that one out. I wish the designers would put just a few notes on differences to the real parts when they make them but I am greatful that someone did the heavy lifting in the design.

The CPU runs fine at 25 MHz.

-

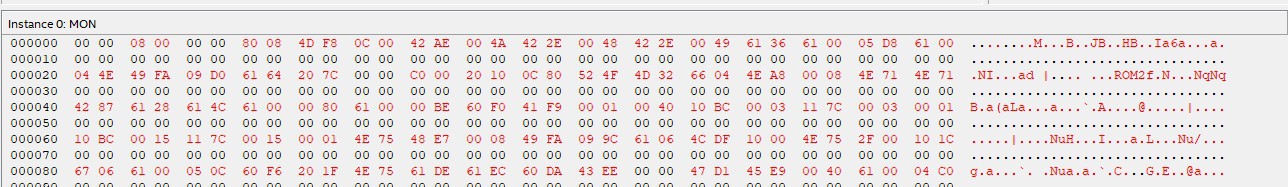

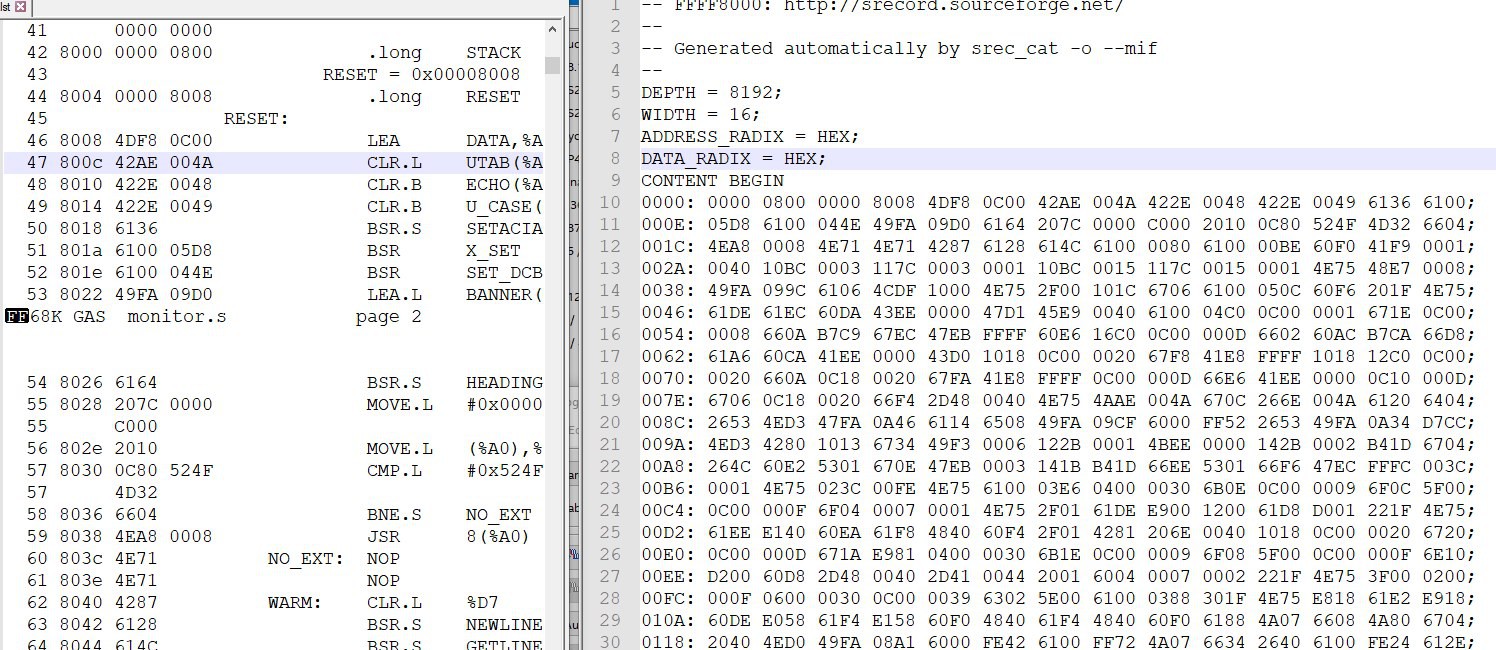

Loading the Monitor into the FPGA ROM

07/10/2020 at 11:27 • 0 commentsThe HEX file initialization in Quartus is not well behaved. When you make 8-bit ROMs it works fine. When you make a 16-bit wide ROM it doesn't load corrected. That seems to be because the HEX loader in Quartus sees the file addresses as the offset to the 16-bit value rather than the byte address. For this code it then loads the address for every 16-byte line but bumps down by 1 line and tries to load the next line.

![]()

The workaround is use the srecords utility to shift the address and save the result as an Altera MIF file. The steps are:

Shift ROM addresses for Quartus FPGA Tool

- Assembler output (monitor.hex)

:2080000000000800000080084DF80C0042AE004A422E0048422E00496136610005D861009E :20802000044E49FA09D06164207C0000C00020100C80524F4D3266044EA800084E714E71EF

- Addresses start at 0x8000 (AAAA below):

:2080000000000800000080084DF80C0042AE004A422E0048422E00496136610005D861009E __AAAA_____________________________________________________________________

Shift the records down

- First convert to S-Records using srec_cat - My copy of s-record tools

[PATH_TO_SRECORD_UTILITIES]\srec_cat monitor.hex -Intel -o monitor.srec -Motorola

- S-Record output (monitor.srec)

S123800000000800000080084DF80C0042AE004A422E0048422E00496136610005D861009A S1238020044E49FA09D06164207C0000C00020100C80524F4D3266044EA800084E714E71EB

- Then shift and save as an Altera MIF file

[PATH_TO_SRECORD_UTILITIES]\srec_cat monitor.srec -offset - -minimum-addr monitor.srec -o monitor.mif -Memory_Initialization_File 16

- Result is (monitor.mif)

-- FFFF8000: http://srecord.sourceforge.net/ -- -- Generated automatically by srec_cat -o --mif -- DEPTH = 8192; WIDTH = 16; ADDRESS_RADIX = HEX; DATA_RADIX = HEX; CONTENT BEGIN 0000: 0000 0800 0000 8008 4DF8 0C00 42AE 004A 422E 0048 422E 0049 6136 6100; 000E: 05D8 6100 044E 49FA 09D0 6164 207C 0000 C000 2010 0C80 524F 4D32 6604; 001C: 4EA8 0008 4E71 4E71 4287 6128 614C 6100 0080 6100 00BE 60F0 41F9 0001; ...

- Load into Quartus in the Monitor_68K_ROM using Megawizard

- Verified using In System Memory Contents tool in Quartus

![]()

Teesside TS2 Monitor (TSBUG2) Commands

For TSBUG 2 Version 23.07.86

<address> is a hexadecimal number, e.g. FF0A Arguments in square brackets are optional.

- JUMP <address>

- Begin execution at <address>.

- MEMORY <address>

- Examines contents of <address> and allows it to be changed. Typing "-" goes to previous address, space allows entering word-size data to write to current address, <Return> exits, and any other key goes to next address.

- LOAD [<string>]

- Loads S1/S2 records from the host. <string> is sent to host.

- DUMP <start address> <end address> [<string]

- Sends S1 records to the host, preceeded by a string.

- TRAN

- Enters the transparent mode. Exited by ESC E.

- NOBR <address>

- Removes the breakpoint at <address> from the breakpoint table. If no address is given all breakpoints are removed.

- DISP

- Displays the contents of the pseudo registers.

- GO <address>

- Starts program execution at <address> and loads regs from pseudo registers.

- BRGT <address>

- Puts a breakpoint in the breakpoint table, but not in the code.

- PLAN

- Puts the breakpoints in the code.

- KILL

- Removes breakpoints from the code.

- GB [<address>]

- Sets breakpoints and then calls GO. IF <address> is omitted, uses PC value in pseudo registers.

- REG <reg> <value>

- Loads <value> into <reg> in pseudo registers. Used to preset registers before a GO or GB.

-

Pieces of the 68000 Design

07/10/2020 at 11:20 • 0 commentsI've gathered the various pieces of the design as follows:

RETRO-EP4CE15 Card

M68000 CPU

- TG68K_2013 VHDL Core

- Tested to run at 25 MHz

Monitor ROM

- TSBUG2 Monitor

- TUTOR Monitor

Internal SRAM

- 32KB

- 16Kx16

Video Display Unit (VDU)

- Based on Grant Searle's ANSI terminal

- Emulates 6850 UART interface

- VGA video

- 80x25 characters

- 640x480 resolution

- 2/2/2 bits RGB (64-colors)

- PS/2 keyboard

6850 ACIA UART

- Neal Crook's modifications to Grant Searle's 6850 VHDL code

GitHub Repository

The repository is here.

land-boards.com

land-boards.com