-

Just have to reorder some memory

03/18/2021 at 19:18 • 0 commentsRunning some tests/applications (e.g. ehBASIC) showed me, I have have to rethink my memory usage in bank $00. I will have to move the monitor stack higher up in memory, maybe start the stack at $BF00. Also I want to move the UART buffer(s) lower in memory. This will free some extra (continuous) memory I can use.

The new memory map might look like this:

$FFFF $FFF0 |________Emulation mode interrupt vectors $FFE0 |________Native mode interrupt vectors $FD00 |________Reset routine(s) $FCA0 |________Fixed jump table $FC00 |________Interrupt Service Routine(s) $D800 |________Supermon816 (adapted from original by BigDumbDinosaur) $D000 |________Intel Hex Uploader (adapted from original by Ross Archer) $CD00 |________UART driver (inspired by and based on code by BigDumbDinosaur) $C020 |________UART I/O registers (mapped to UART card using GAL) $C000 |________Start of ROM $BFFF |________Supermon816 stack | (growing down...) | $A000 |________Bottom of stack (?), giving 8kByte of stack $9FFF |________Top of free RAM | | (Giving 37.5 kByte of free RAM) | $0A00 |________Free RAM $09FF | | $0980 |________UART Channel B TxD buffer $097F | $0900 |________UART Channel B RxD buffer $08FF | $0880 |________UART Channel A TxD buffer $087F | $0800 |________UART Channel A RxD buffer $07FF | | $02E6 |________Free RAM / RESERVED? $02E4 |________Character scan routine vector $02E2 |________Character input routine vector | (Reserved) $02DE |________Software BRK vector $02DC |________Software BRK vector checksum $02DA |________Software INT/IRQ vector $02D8 |________Software INT/IRQ vector checksum $02D6 |________Software NMI vector $02D4 |________Software NMI vector checksum $02D2 |________Software Reset vector checksum $02D0 |________Software Reset vector $02EF | $0266 |________Free RAM $0265 | | $0246 |________(Supermon 816 auxbuffer) $0245 | | $0200 |________Keyboard buffer $01FF | | $0100 |________Hardware stack $00FF | | $0000 |________Zero Page -

ehBASIC works

03/08/2021 at 20:24 • 0 commentsCompleted my changes to the ehBASIC source (v2.22p5C) in order to run BASIC in Adria. The source, with my changes, will be available in my GitHub repository.

Unfortunately ehBASIC is too large right now to be implemented in ROM. This means it has to be loaded everytime I want to play with BASIC.

Also found a few little bugs in the Supermon816 source, these are now corrected.

-

Some housekeeping done...

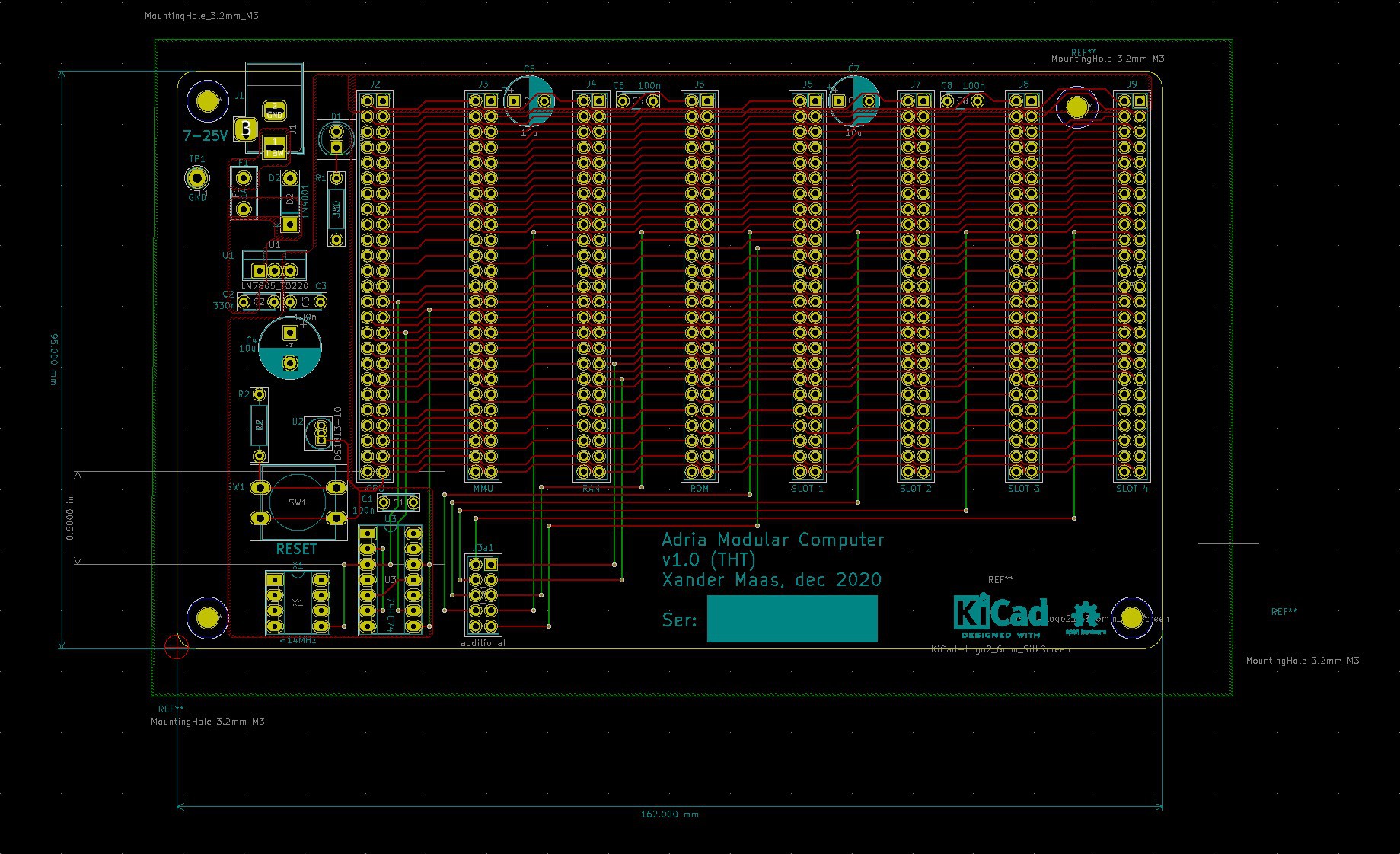

02/24/2021 at 16:39 • 0 commentsReceived the v2.0 version of the backplane. The backplane is now 4-layer, with ground and power planes as layer 2 and 3. I forgot to remove the ground-fill on the bottom layer, let's see how that works out.

Also published the project files on GitHub and write down the memory map (as it is right now) in the project details.

-

Just a backlog of logs

02/22/2021 at 20:22 • 0 commentsThe project has been started in december 2020. A first run of boards has already been done, as has a second run.

![]()

In the meantime, I have updated the backplane to a 4-layer PCB, with ground and power (+5V) in the inner layers and signals routed at the top and bottom layers. These haven't arrived yet, but should in a few days. This new (4-layer) revision should make it possible for me to run the computer at higher clock speeds.

Also the first run of the backplane had some "small" issues:

- U3 missed the feedback from pin 8 to pin 12 (/PHI2) for the clock divider

- Missed all /IRQ and /NMI traces to and from the CPU slot and all peripheral slots

![]()

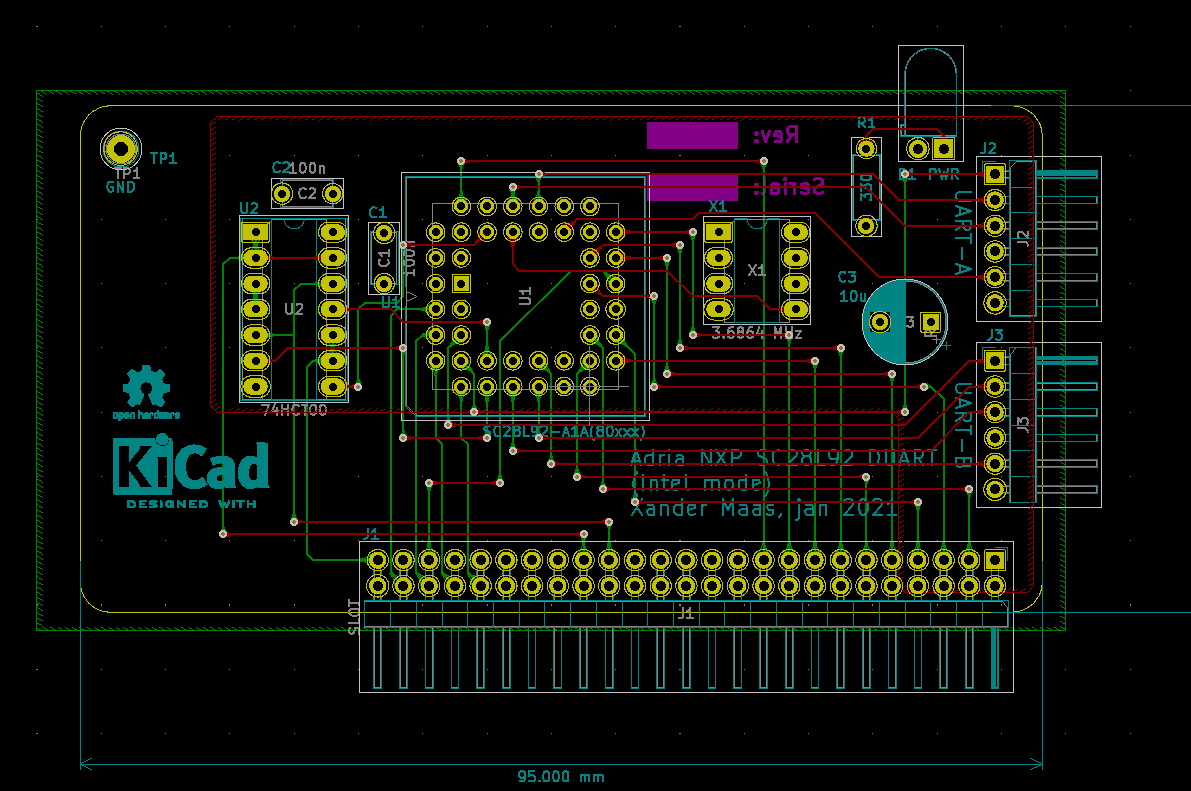

Also I have had a few 6551 (I used a SY6551) UART and NXP SC28L92 UART boards manufactured. With the help of some great people at forum.6502.org, I now have a working driver in ROM for the SC28L92, so the (speed) limited 6551 board isn't in use right now.

Adria - A 65C816 based computer

Adria is a WDC65C816 based computer, inspired by RC2014. Main goal is to create a DIY friendly computer

Xander Maas

Xander Maas