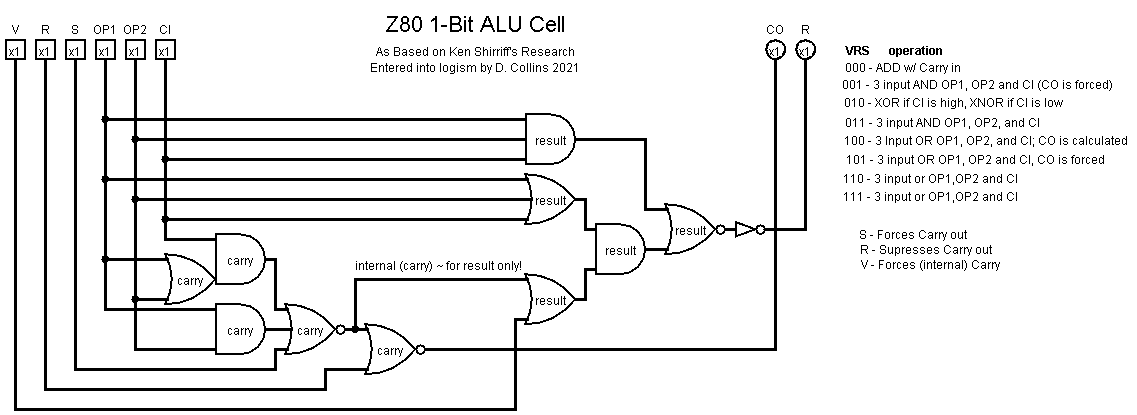

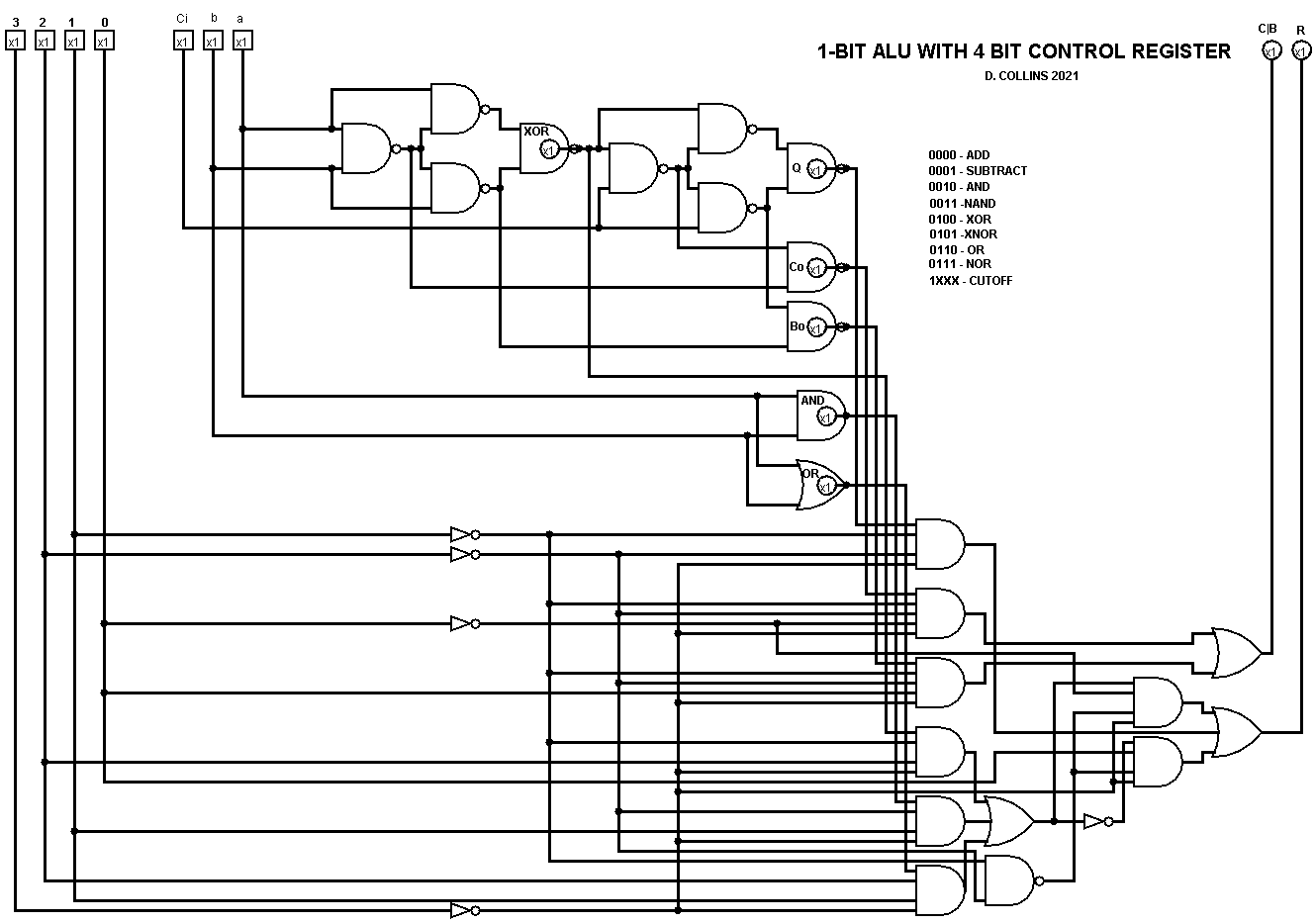

This was going to eventually be a 1 bit CPU with a 4 bit control register. I've sense shifted my sights on building a MC14500 Like state machine, which i'll post the link to the project once it's up on hackaday. I have not decided on an architecture though this project is going to be very much inspired by the UE14500 being built by David from Usagi Electric, which is a vacuum tube computer based on the MC14500 Industrial Control Unit.

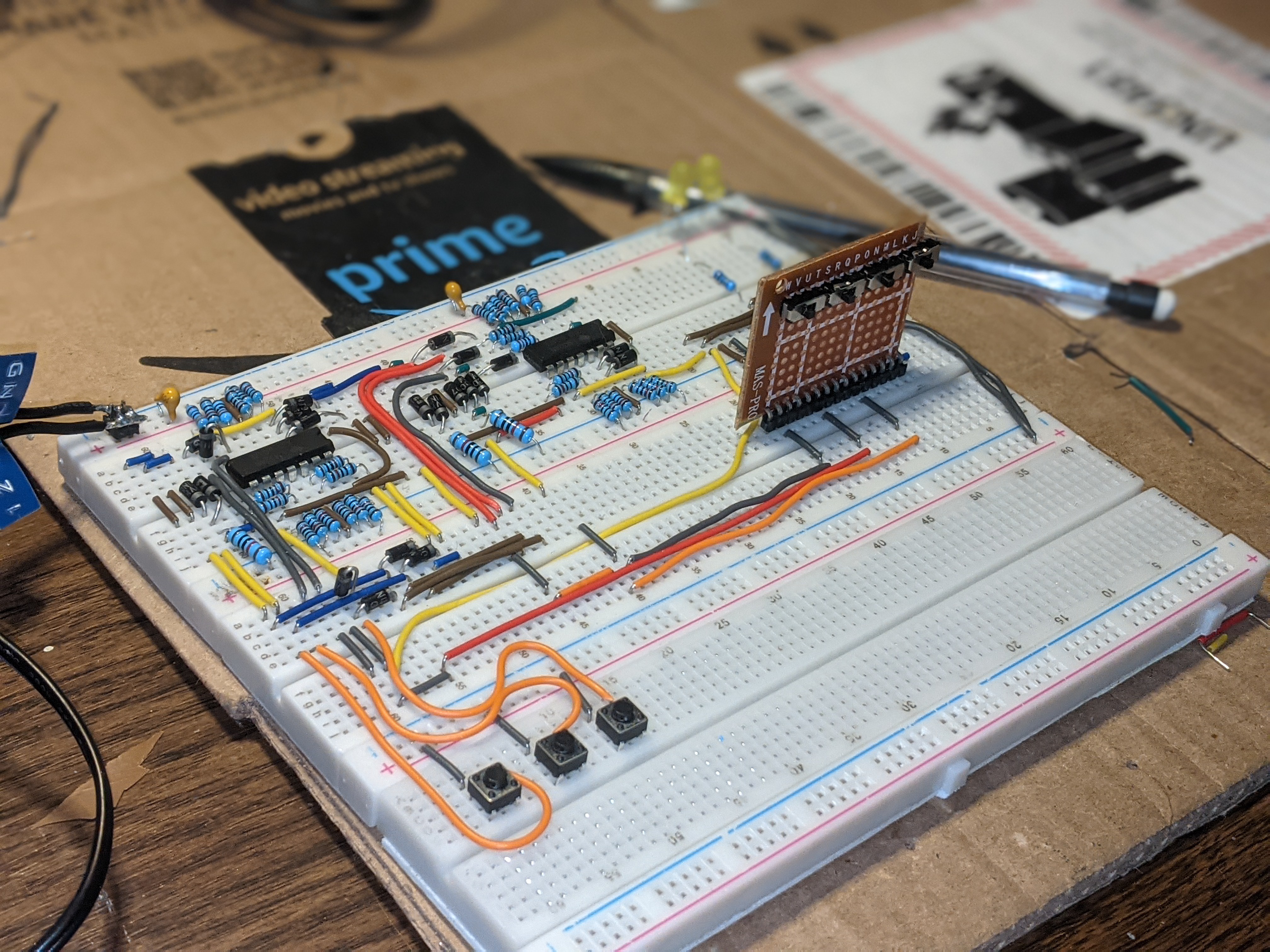

1-Bit ALU useing Open Loop Op-Amps

using the lm324n quad 1mhz op amp to build simple logic; which are then used to create a simple ALU

Dave Collins

Dave Collins

Tim

Tim

Blair Vidakovich

Blair Vidakovich

Usagi Electric (David)

Usagi Electric (David)

Nice project! Certainly one of the most complex ways to build logic gates I have seen :)