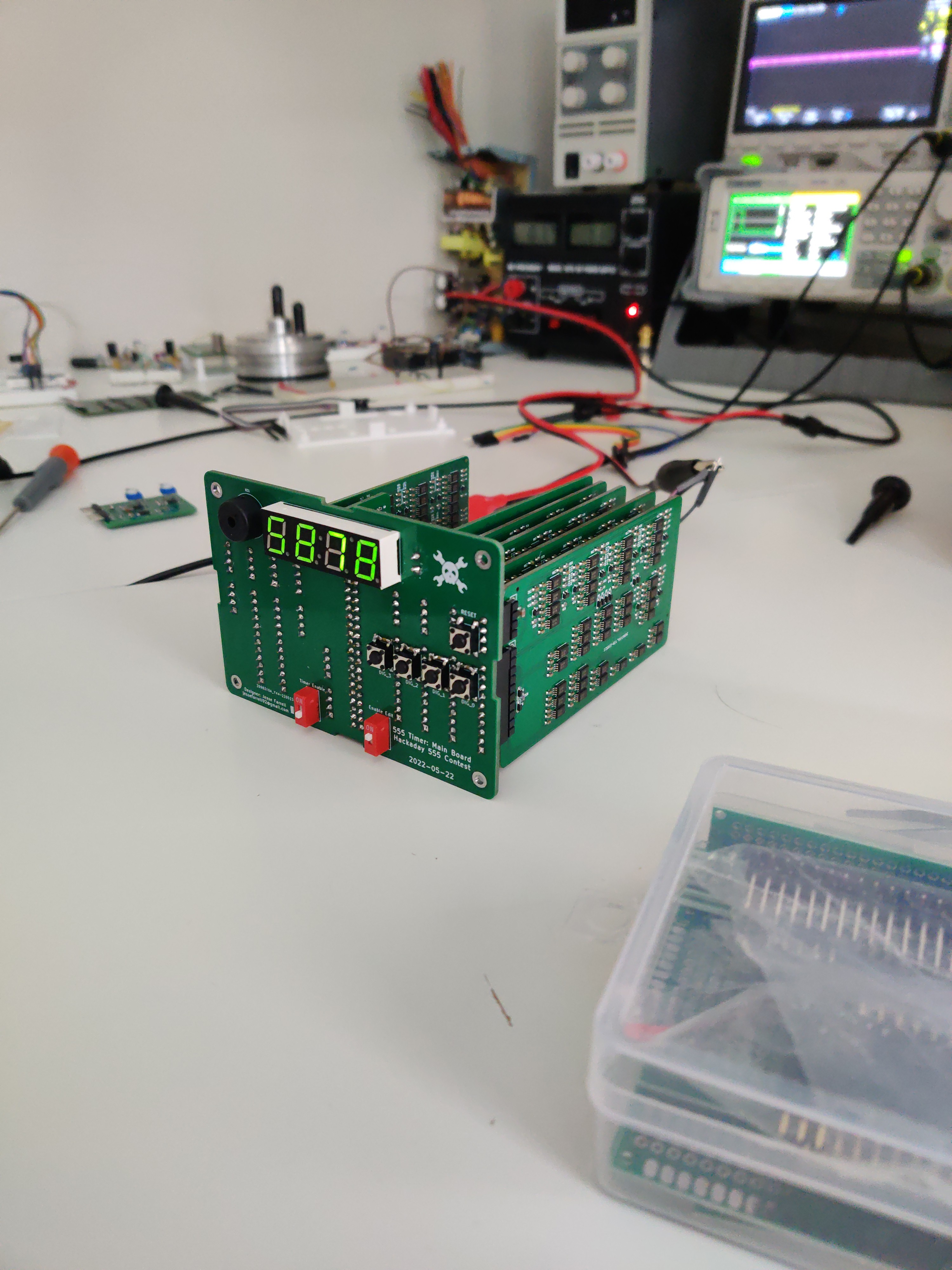

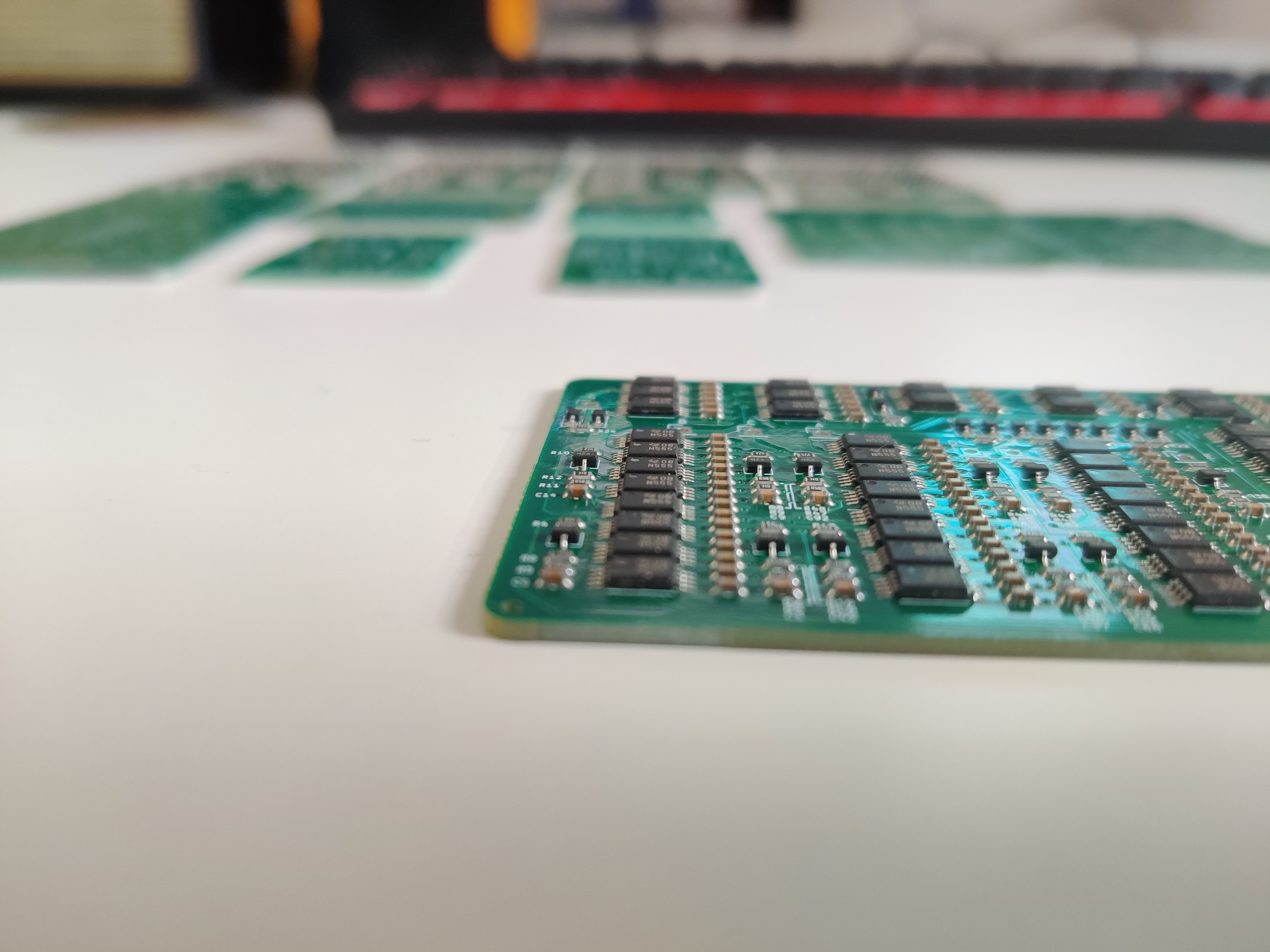

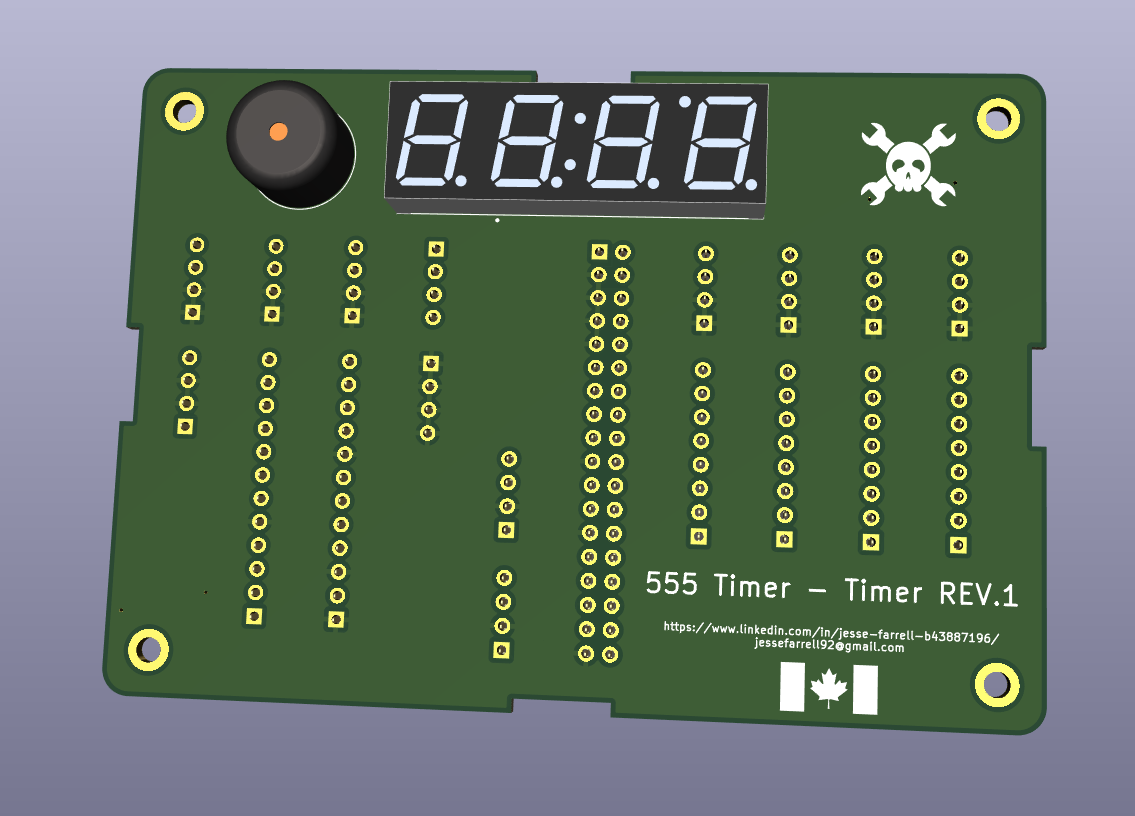

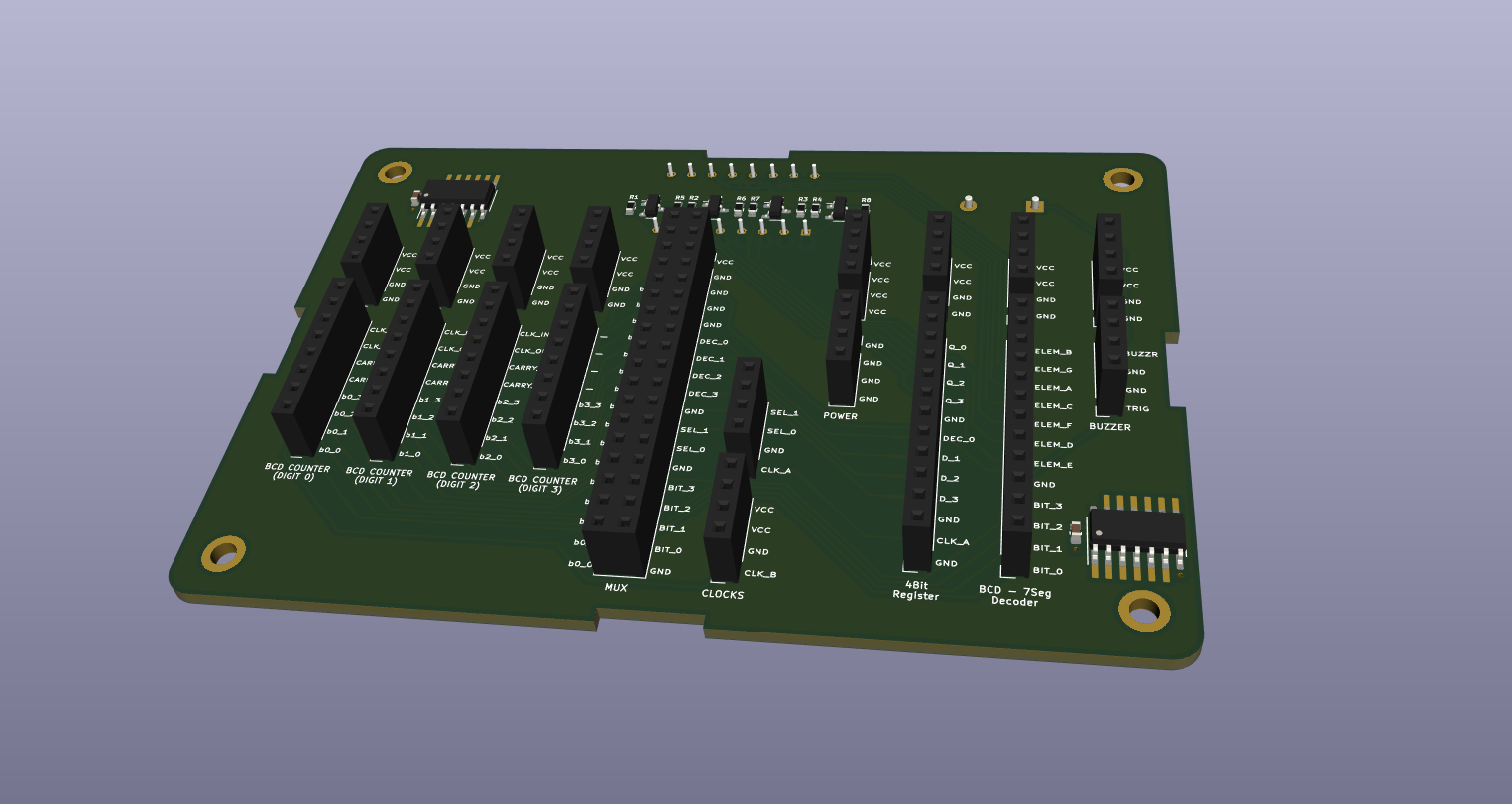

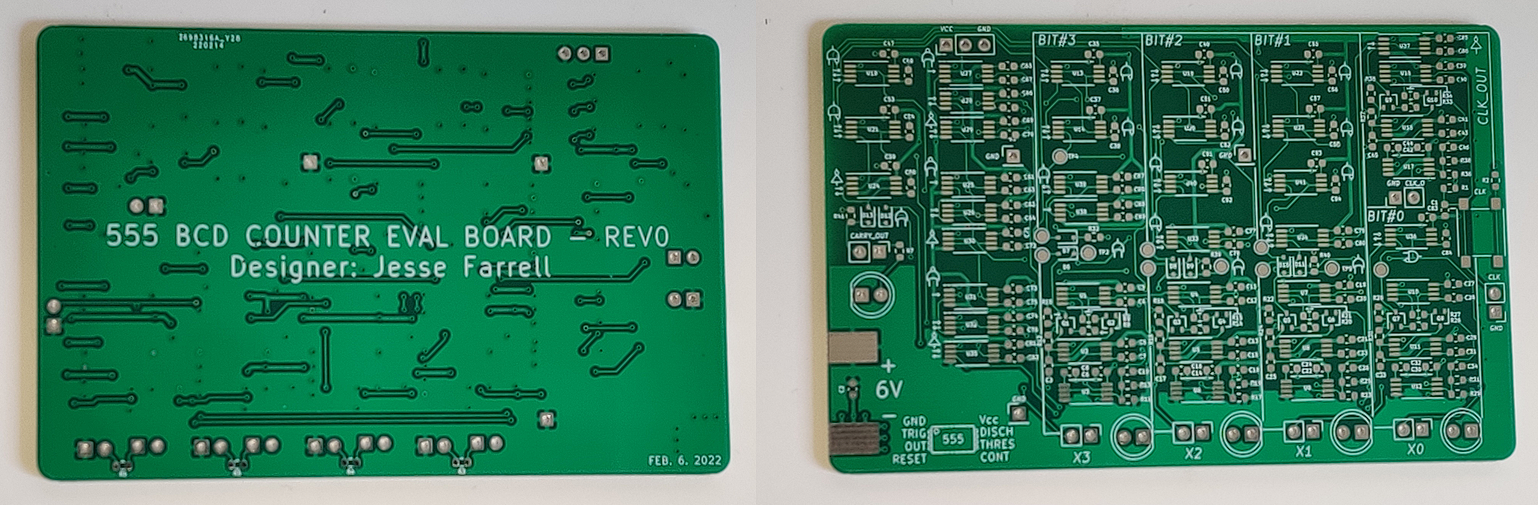

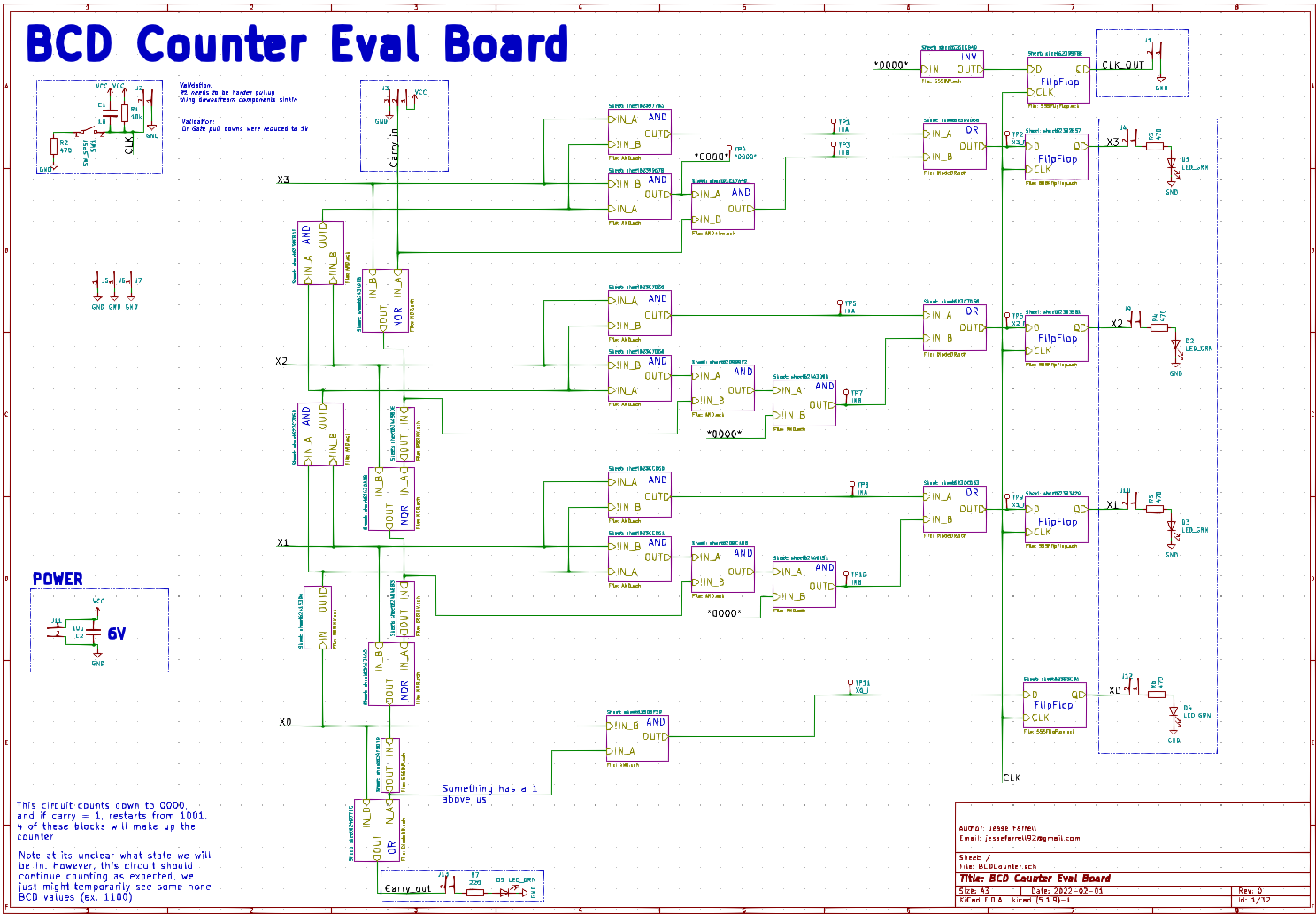

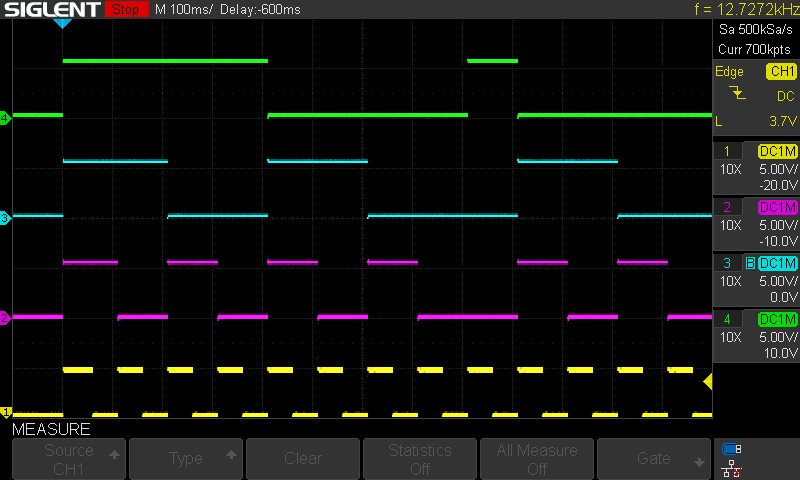

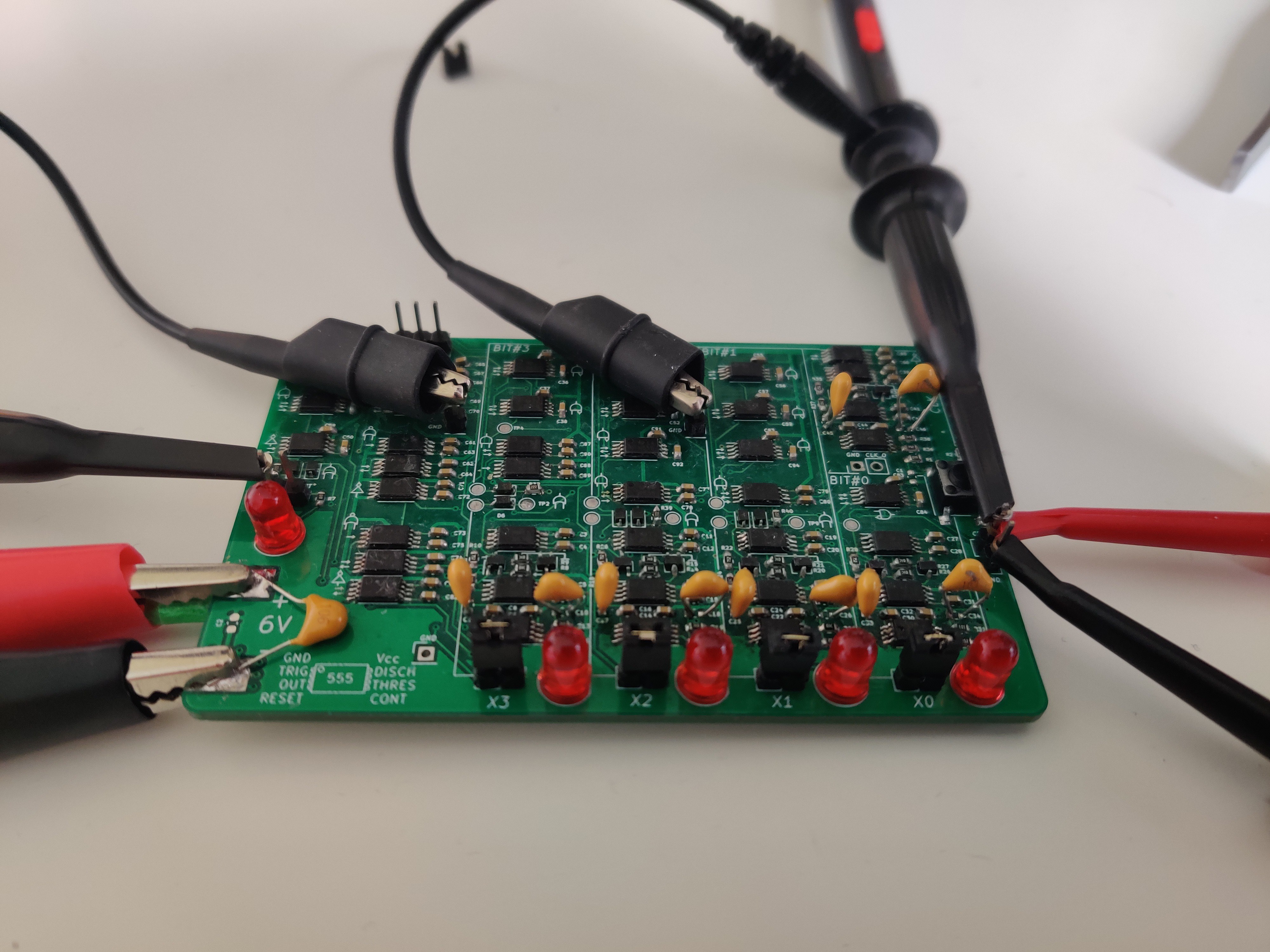

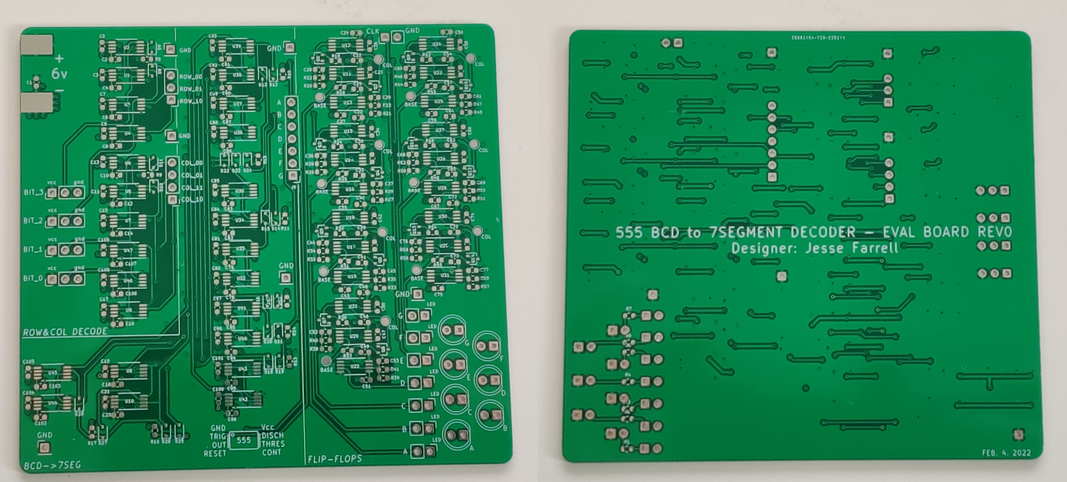

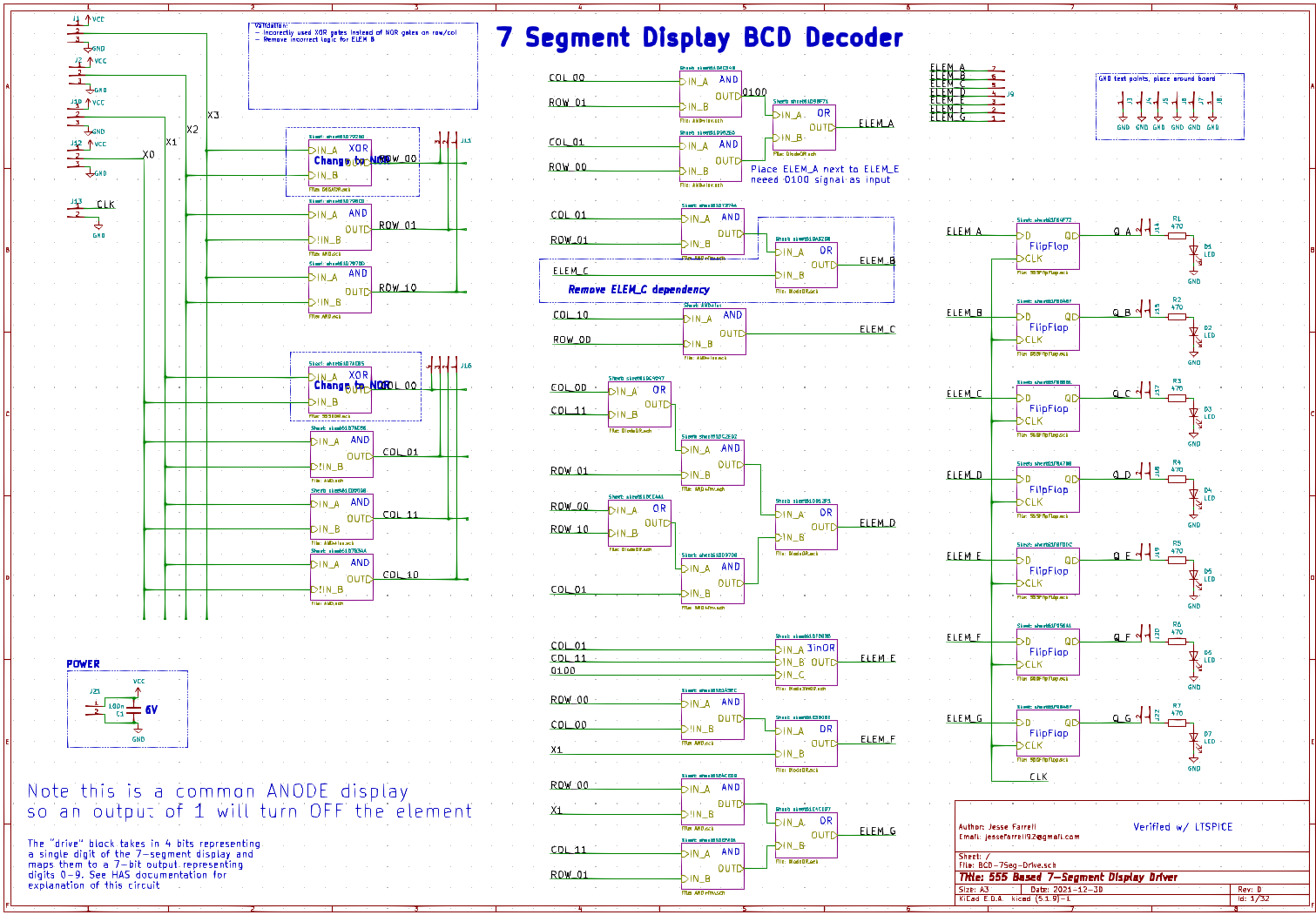

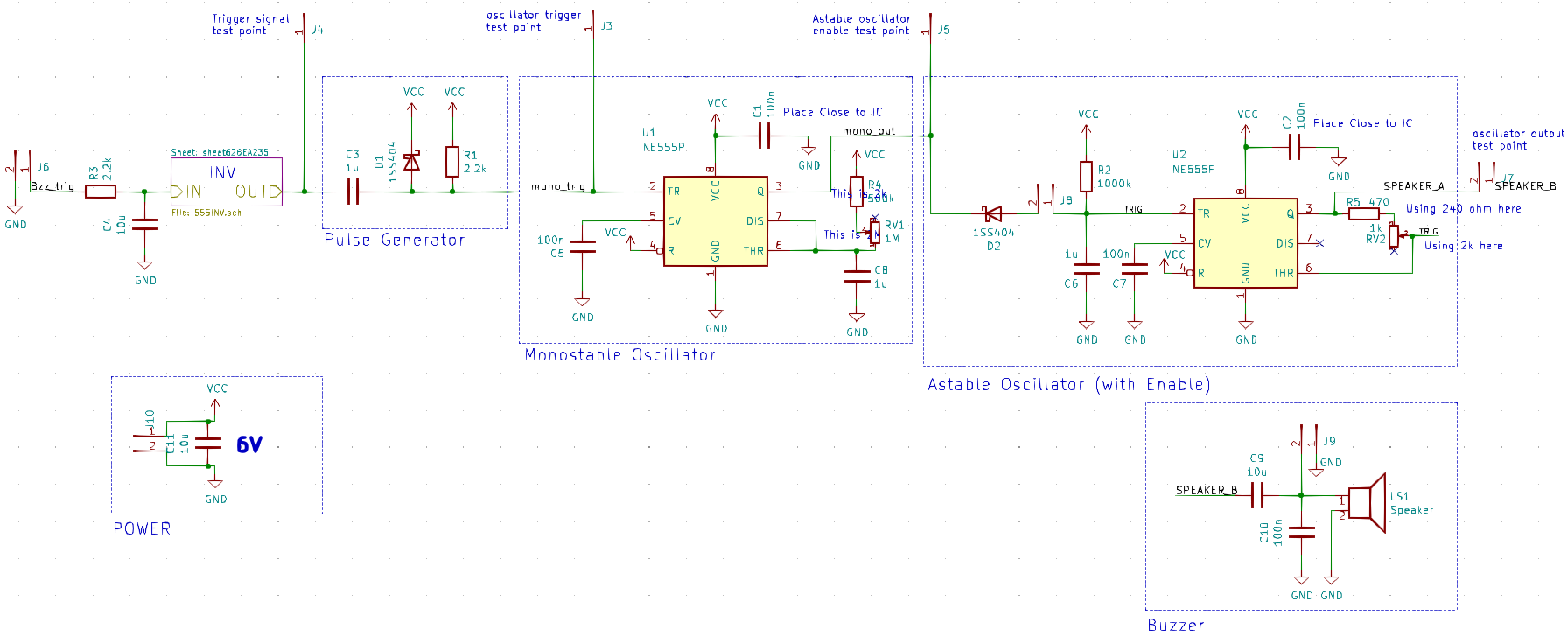

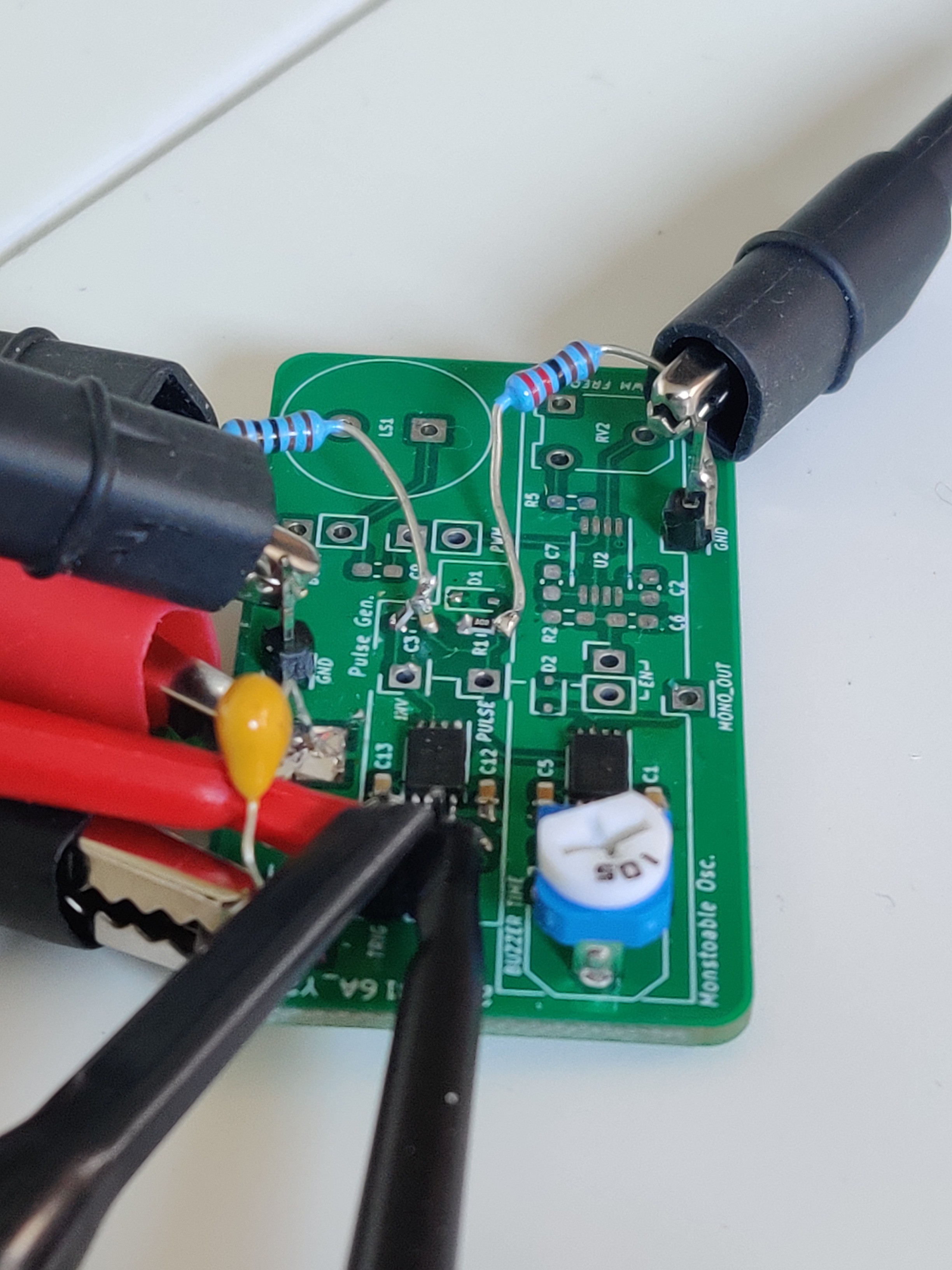

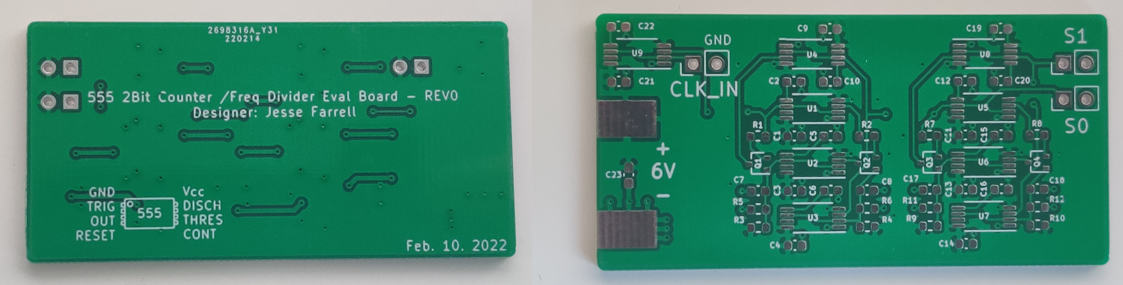

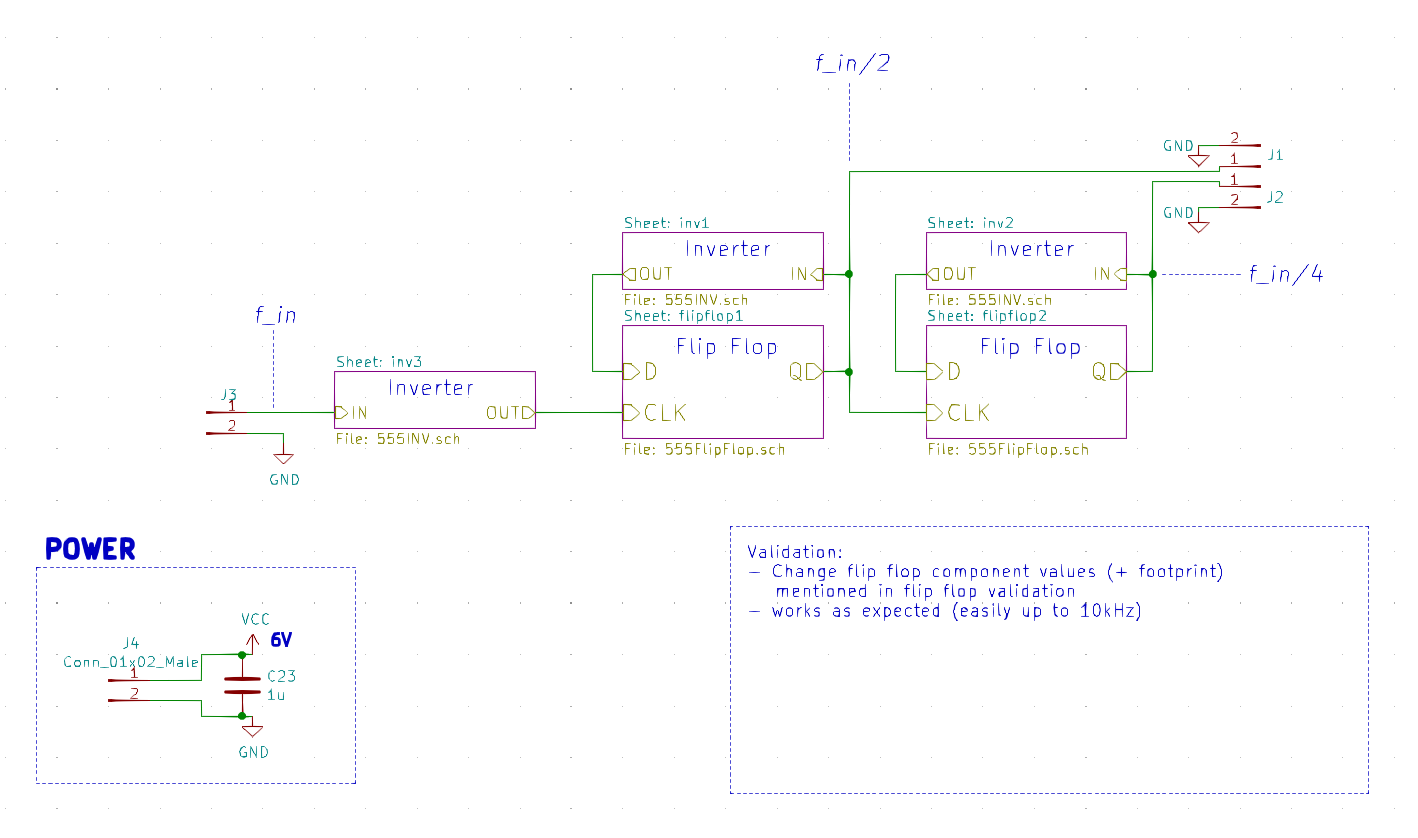

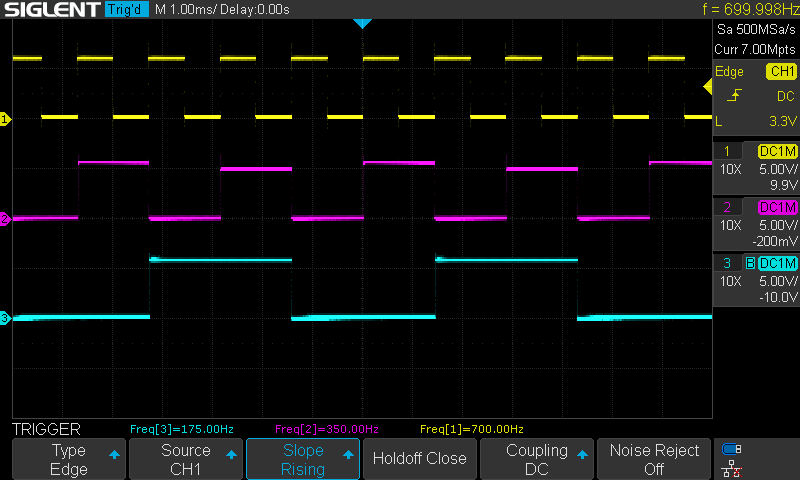

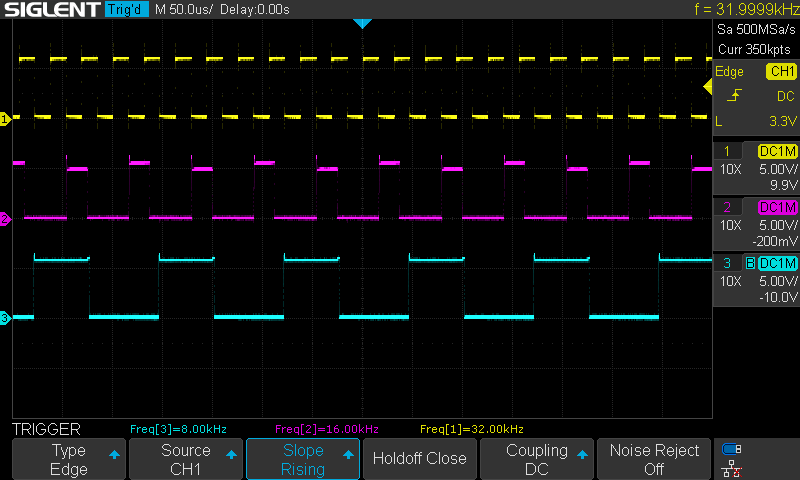

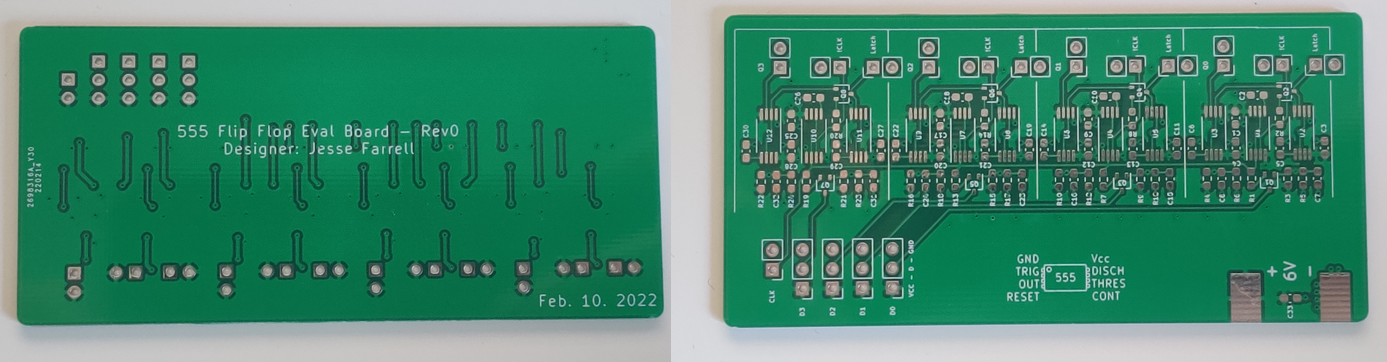

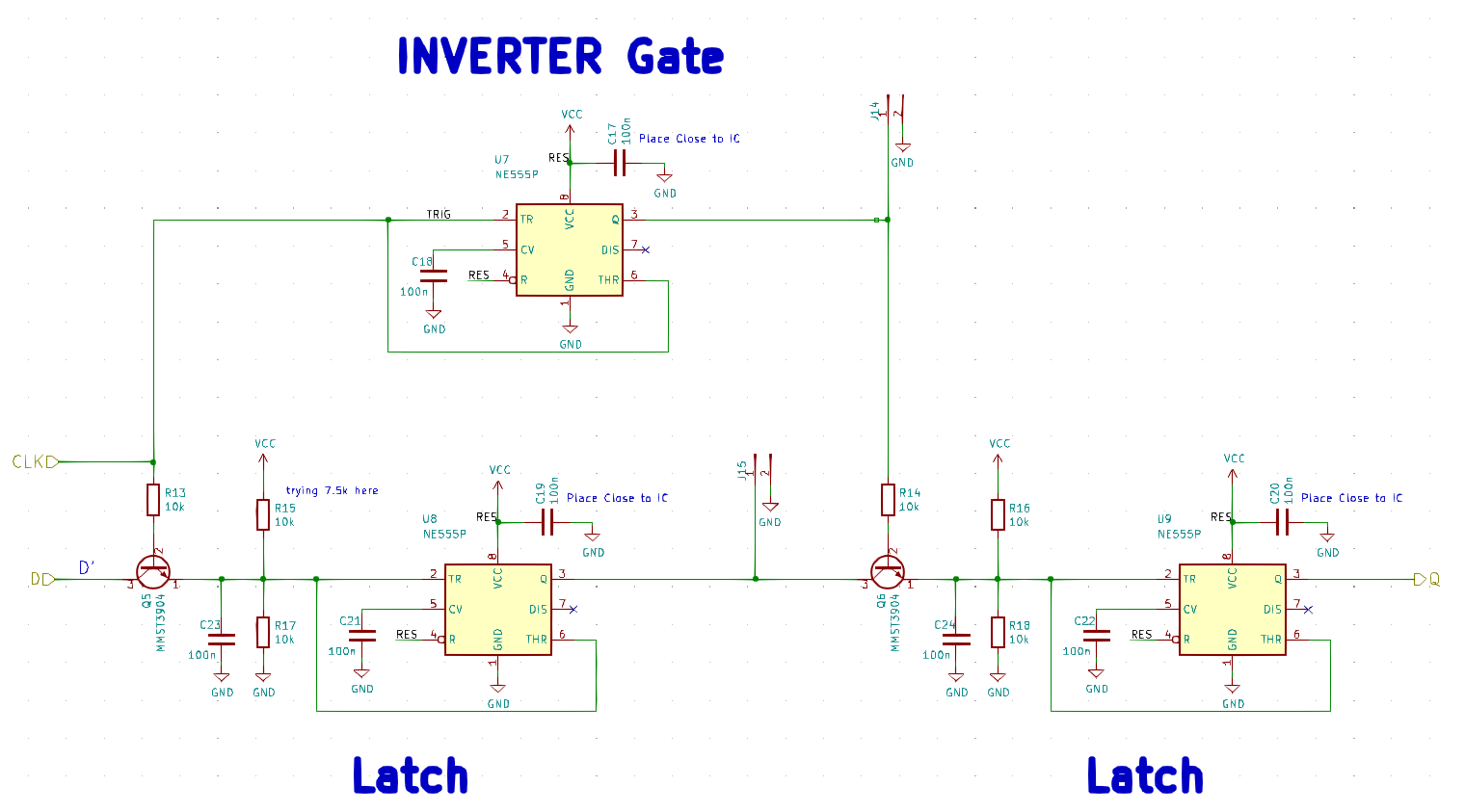

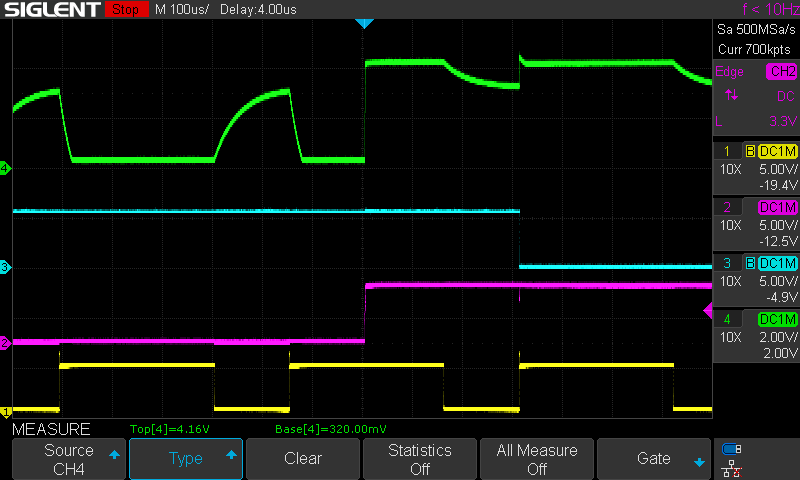

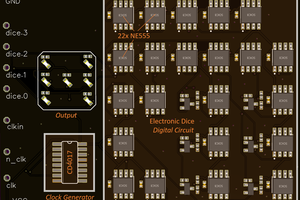

This widget is intended as a somewhat cheeky response to Hackaday’s 555 contest. You've likely come across many different timer or alarm based circuits in the past, possibly even ones featuring 555’s to some extent. This timer of timer’s is somewhat different; it's almost entirely made up of 555's. The widget was rightfully dubbed the 555 Timer Timer, and consists of 277 NE555's!!

555 Timer - Timer

We've come full circle. Here's a timer made up of timers...

Jesse Farrell

Jesse Farrell

Tim

Tim

Yann Guidon / YGDES

Yann Guidon / YGDES

Eric Ljungquist

Eric Ljungquist

It seems @Tim is not following this project yet...