This is for the NE555 "timer" contest

You probably came across electronic dice do-it-yourself kits many times. The design of those has remained virtually unchanged for decades. All of them are based on exactly two ICs: A NE555 and a CD4017.

Two examples found on the internet

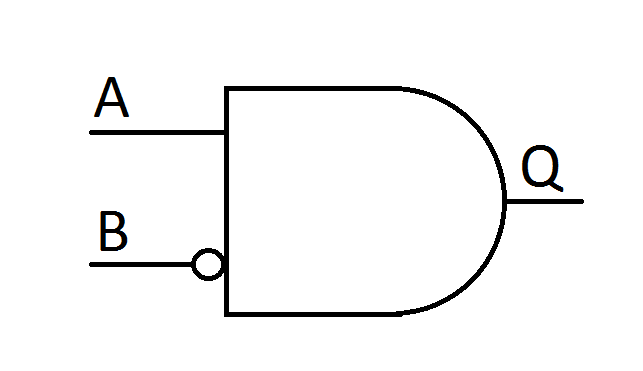

The CD4017 is a counter that is used to cycle through the states. The counter output is converted to the die pattern using a combination of diodes, resistors and transistors. An oscillator based on a NE555 generates counting pulses when the die is activated.

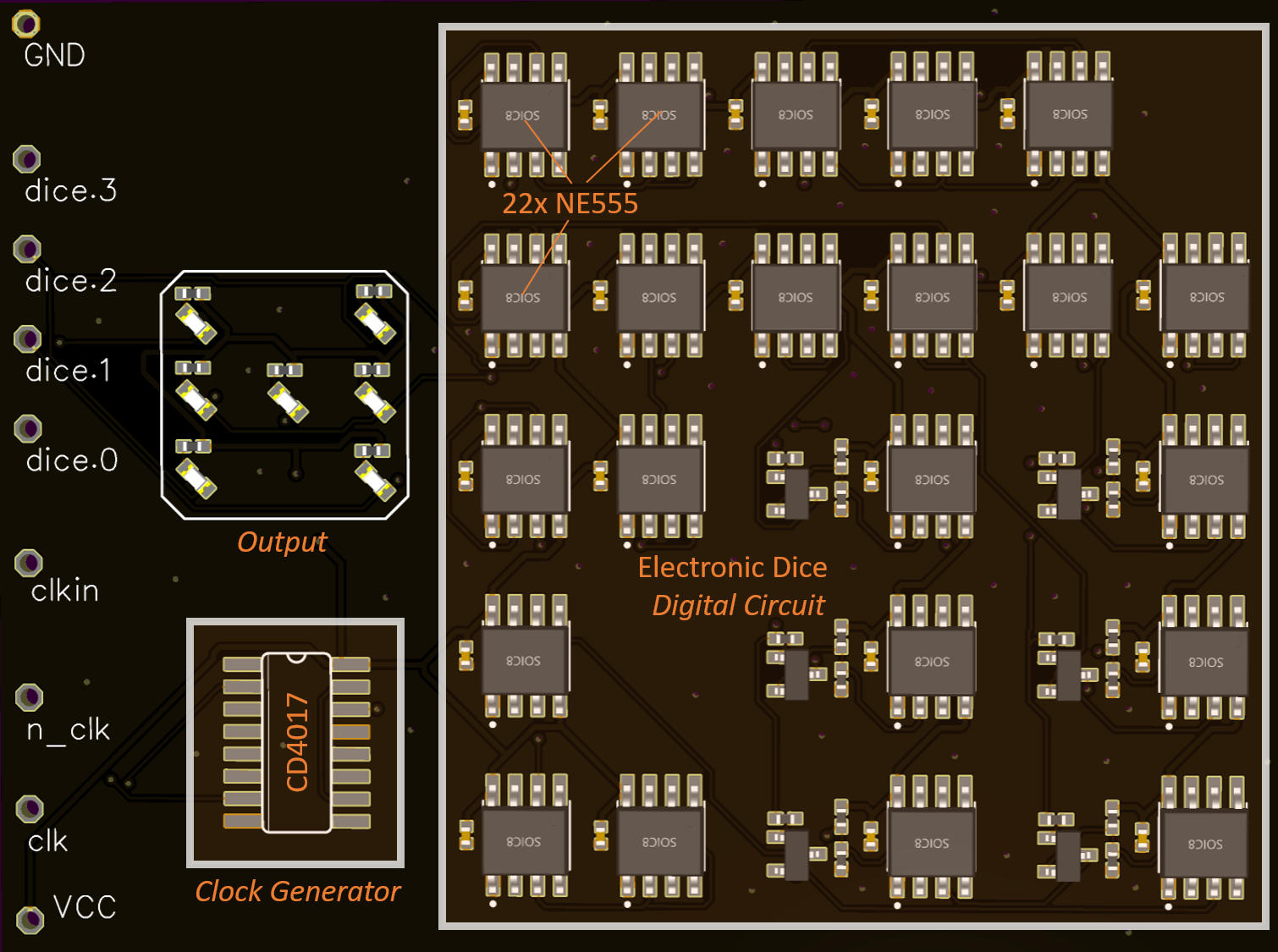

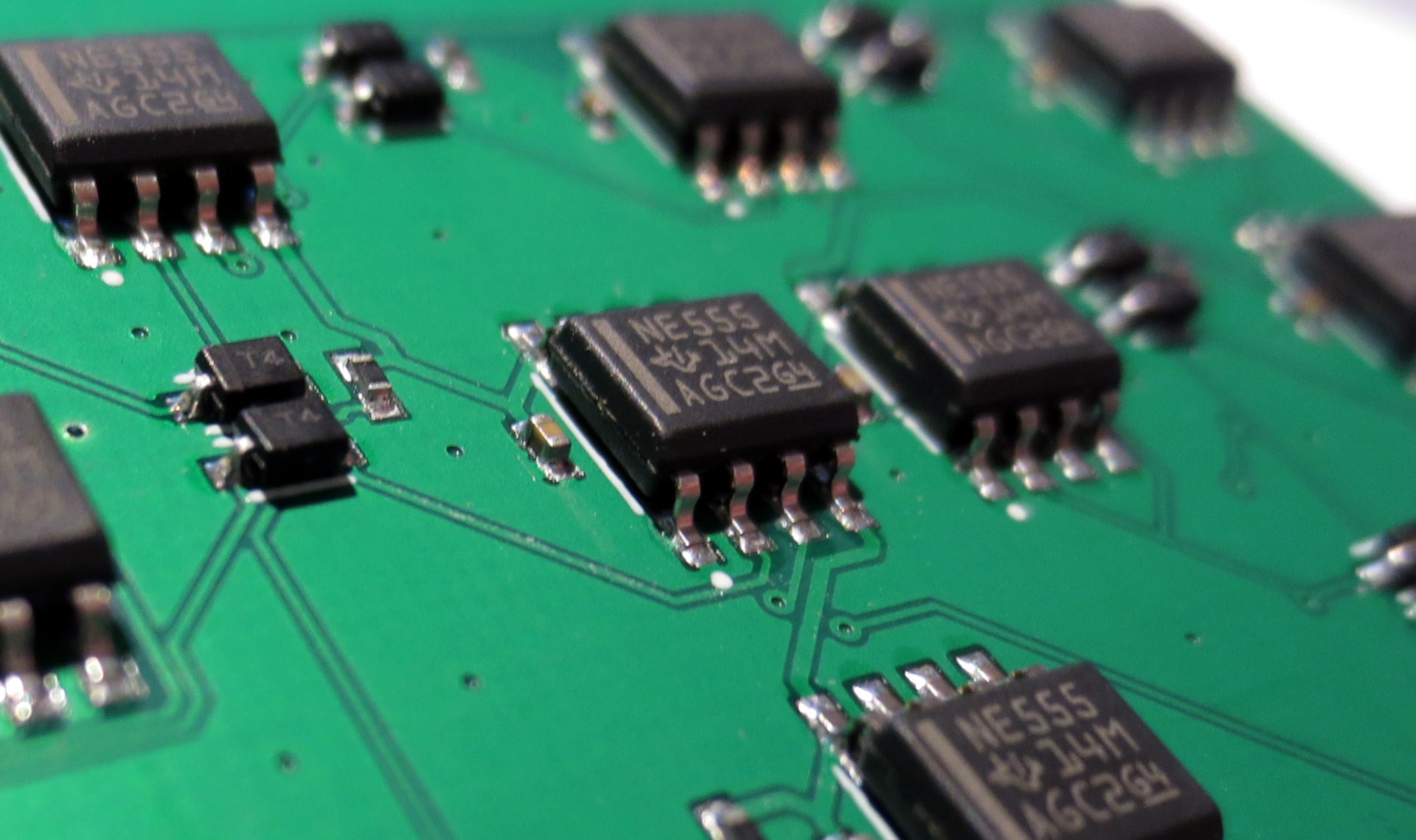

Isn't that a bit limiting? The NE555 surely can do more than being a sidekick to the CD4017. In this project we will bring the NE555 to it's full potential and implement the entire dice using only NE555s. Along the way I also found a nice new job for the CD4017 as a two phase clock generator.

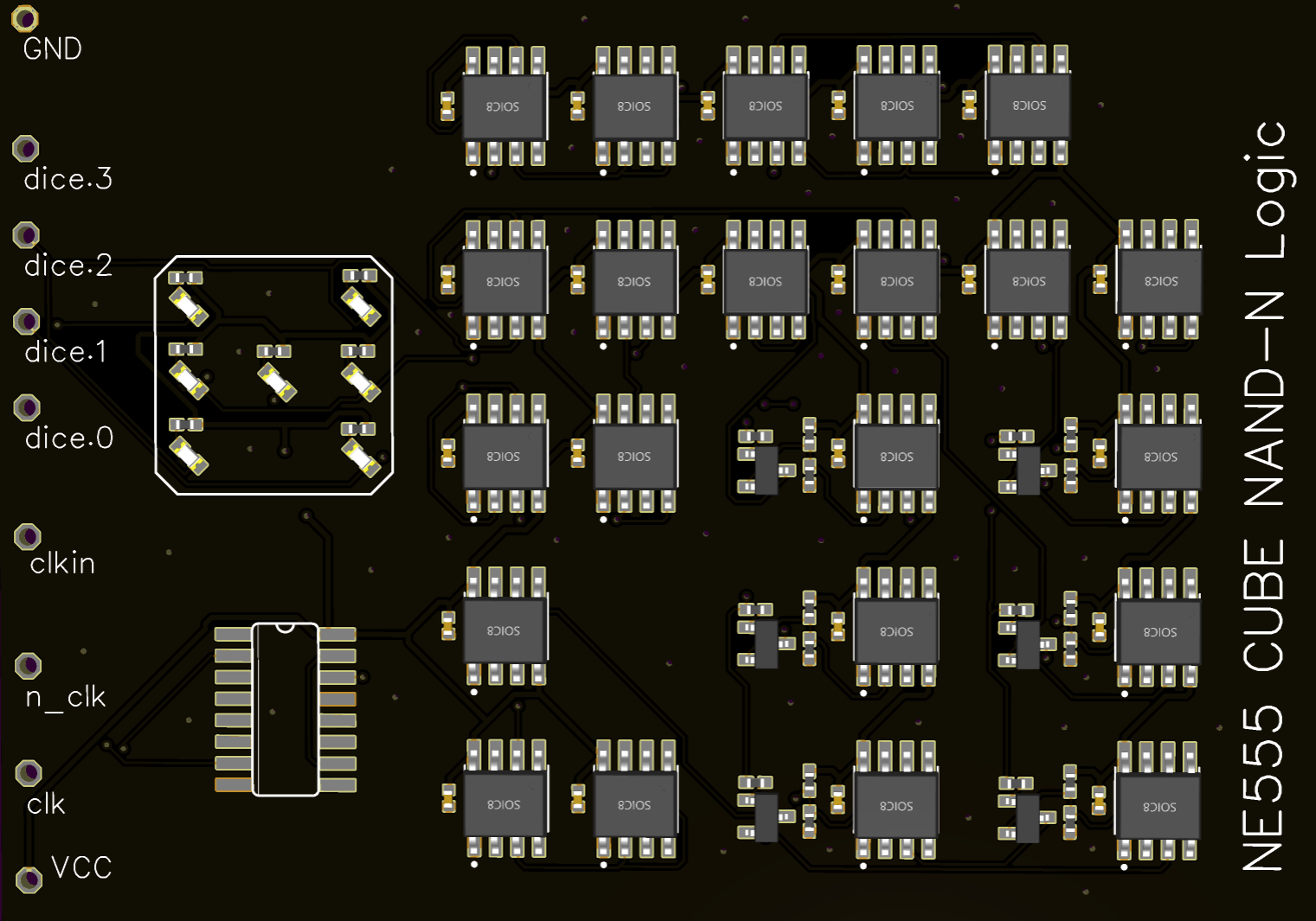

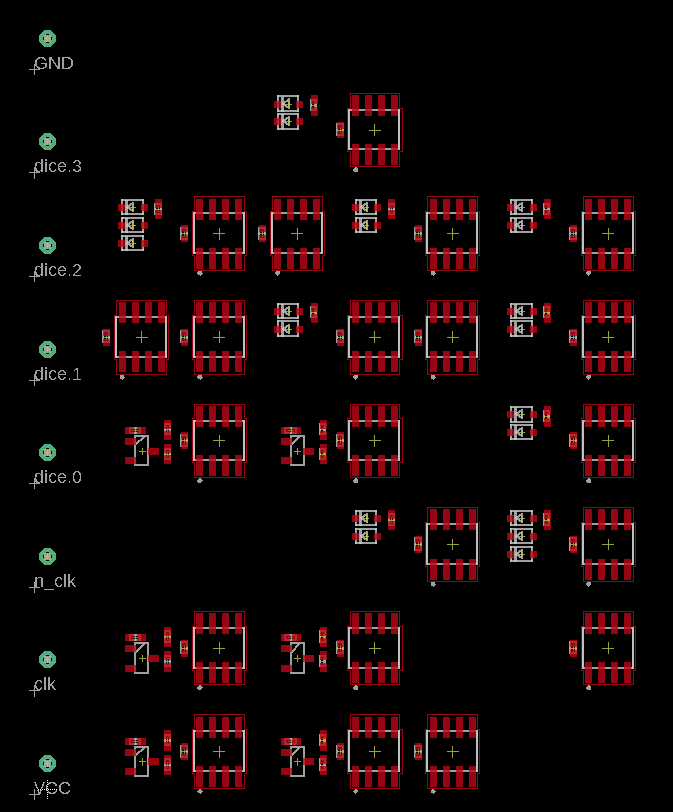

This is a companion project to the NE555 microprocessors to actually test the logic style in real hardware.

The 2021 NE555 Electronic DICE

Tim

Tim

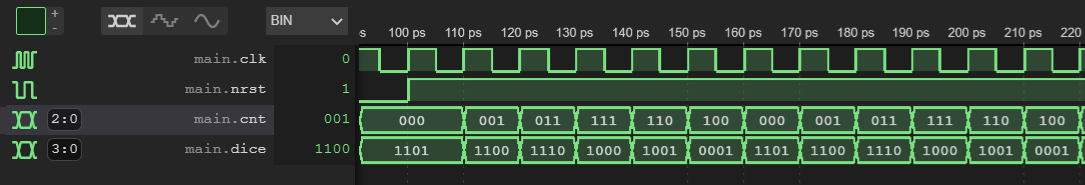

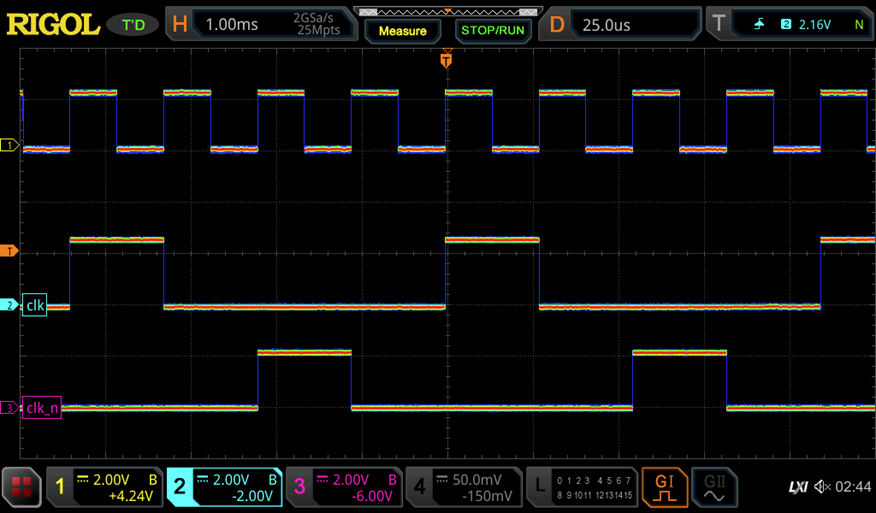

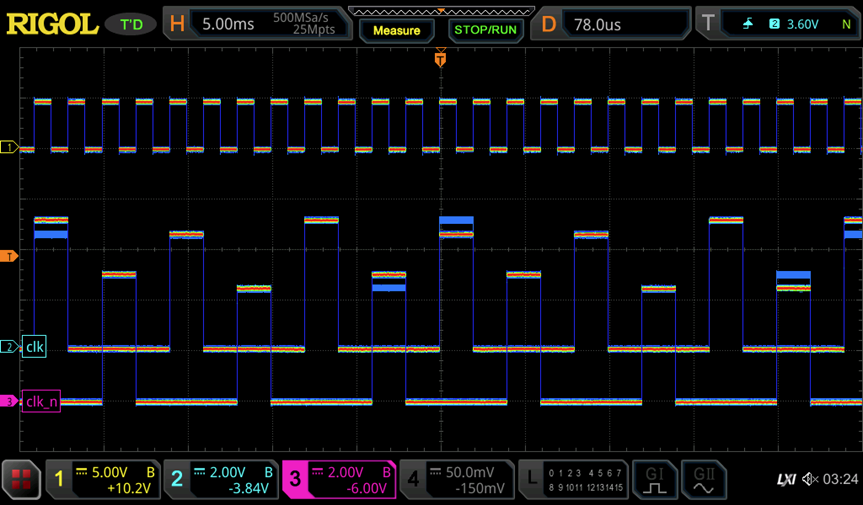

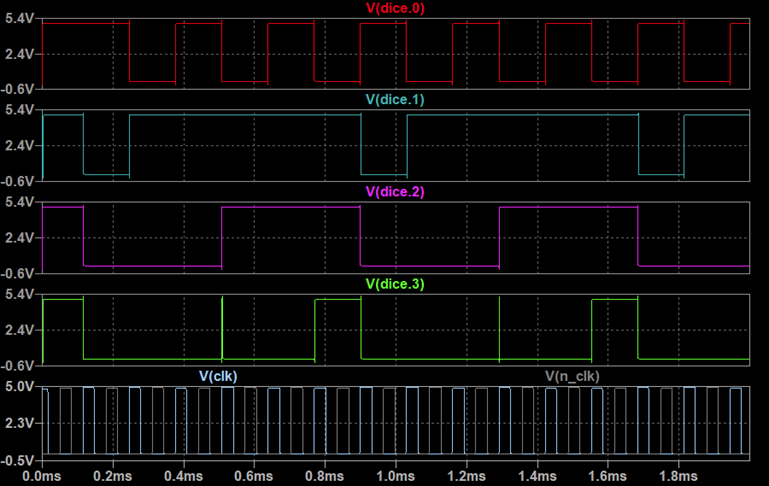

Unfortunately, things did not go as smoothly from there. After some debugging I found that I had to raise the operating voltage to 6V for the dice to function properly. The reason for that is the loading of the clock nets when the input to the latches is low. In that case, the output of the CD4017 has to drive a VBE-diode and a 3.3kohm resistor vs ground. Apparently this is too much and we can observe a significant drop in output voltage which which does not allow the NE555 flip flop to switch. (See

Unfortunately, things did not go as smoothly from there. After some debugging I found that I had to raise the operating voltage to 6V for the dice to function properly. The reason for that is the loading of the clock nets when the input to the latches is low. In that case, the output of the CD4017 has to drive a VBE-diode and a 3.3kohm resistor vs ground. Apparently this is too much and we can observe a significant drop in output voltage which which does not allow the NE555 flip flop to switch. (See

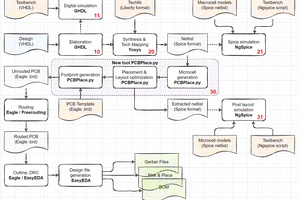

The statistics are as follows:

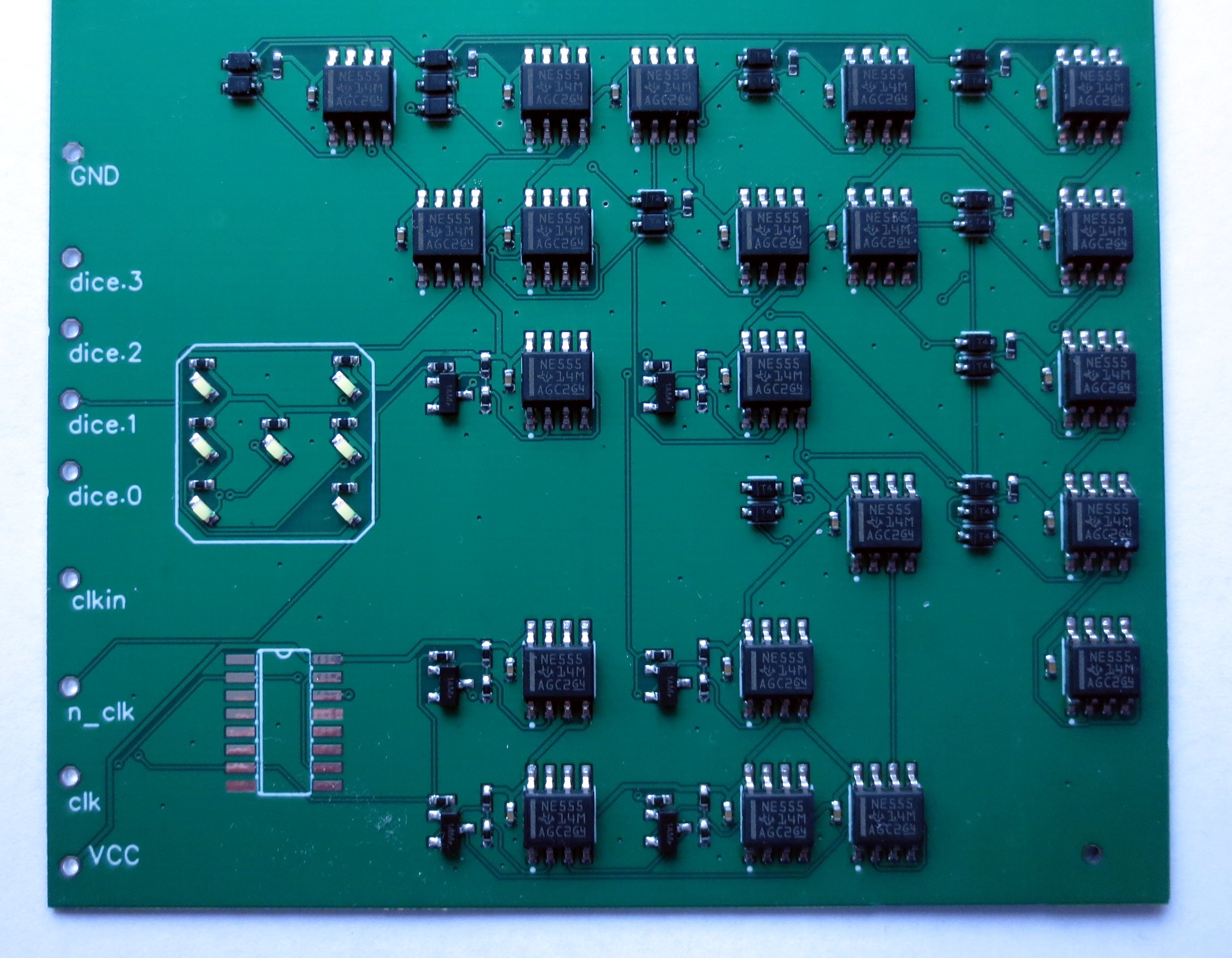

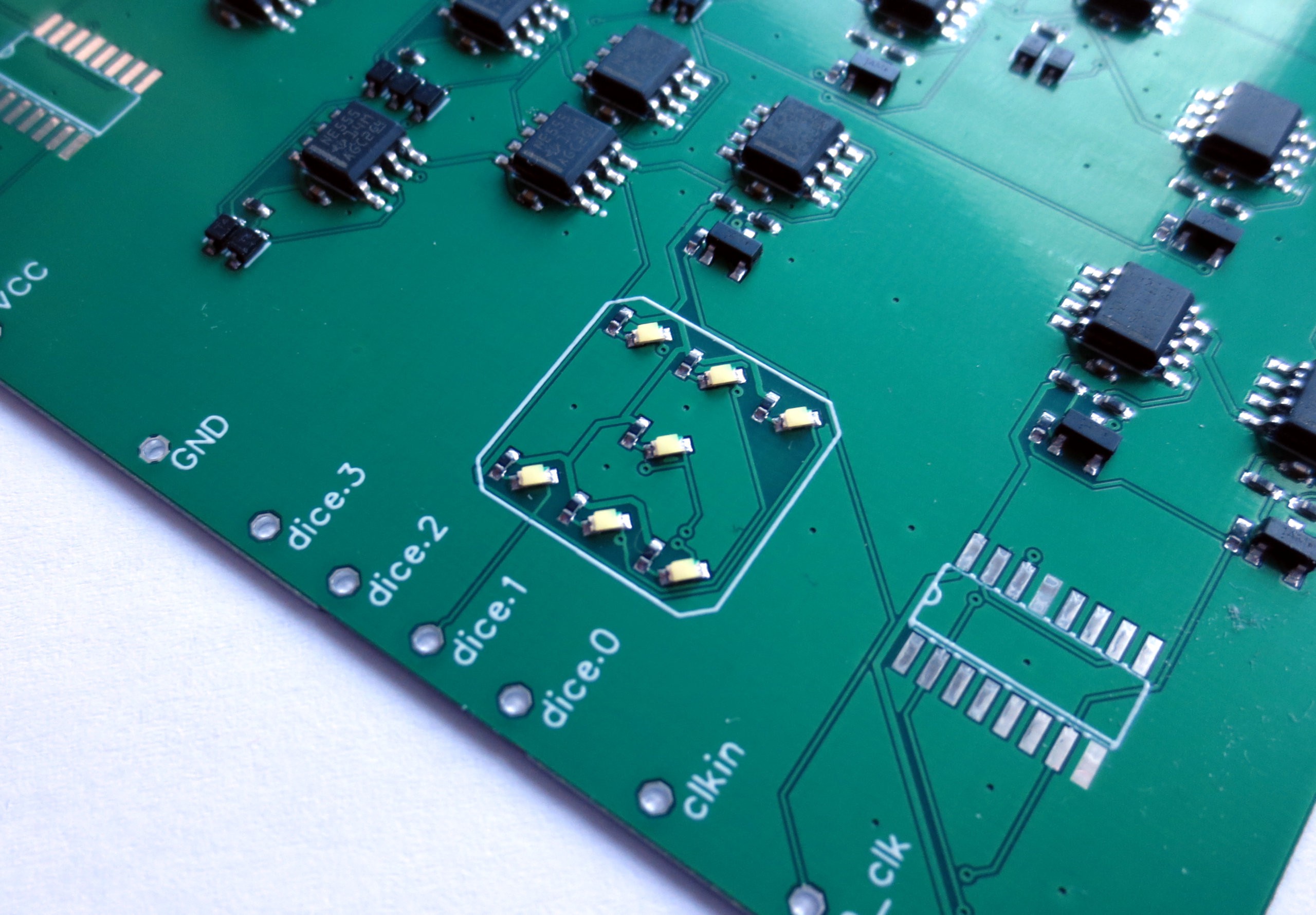

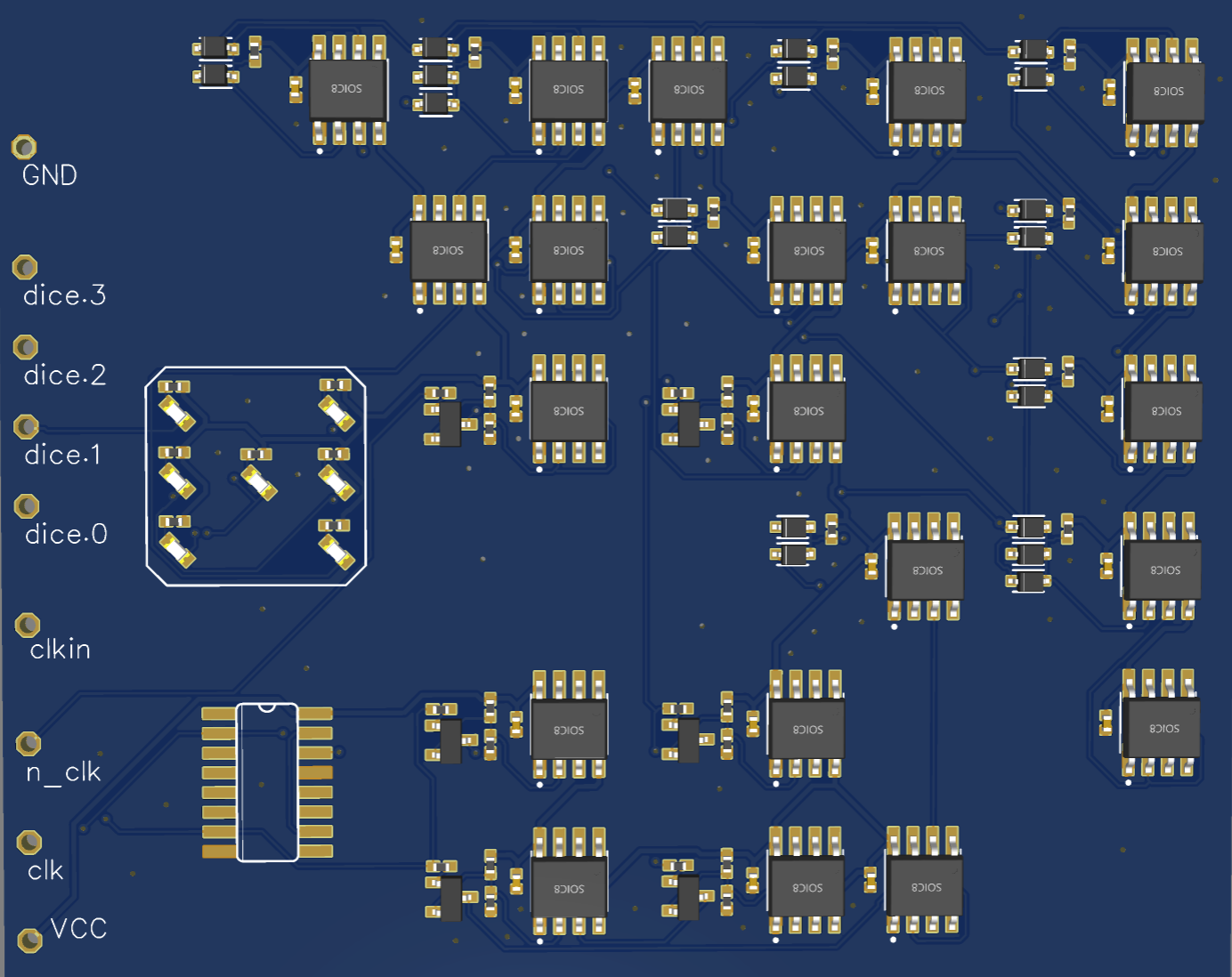

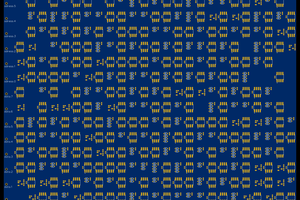

The statistics are as follows: PCBs are being made now and should arrive soon.

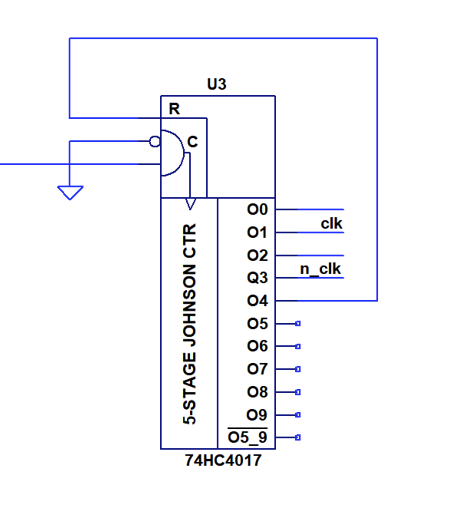

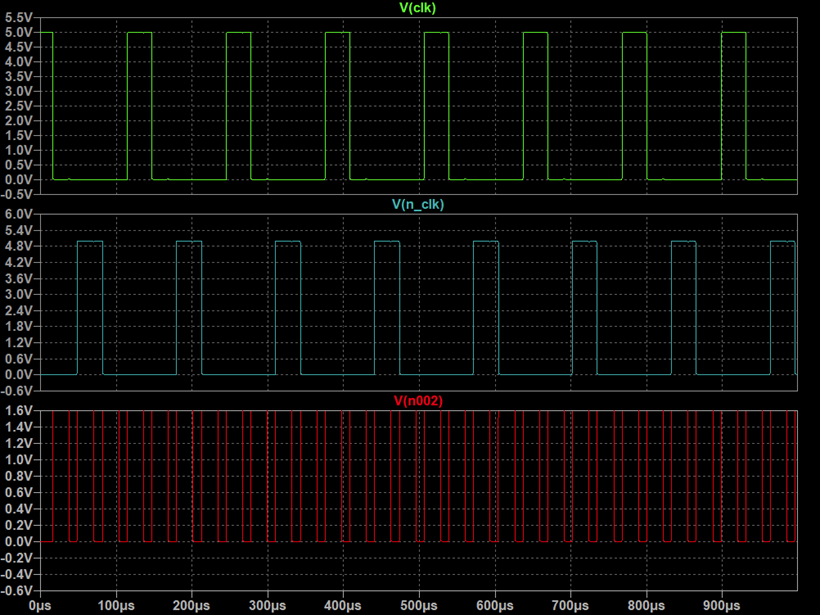

PCBs are being made now and should arrive soon. The circuit above will convert a single clock signals into two non-overlapping clocks. Exactly as needed for the NE555 logic. A simulation of this circuit is shown below. The signal in the lower row is the clock input.

The circuit above will convert a single clock signals into two non-overlapping clocks. Exactly as needed for the NE555 logic. A simulation of this circuit is shown below. The signal in the lower row is the clock input. Things are coming together nicely...

Things are coming together nicely...

https://hackaday.com/2022/01/08/555-timer-on-its-own-in-electronic-dice/