-

One Last Bug Solved

05/29/2023 at 22:32 • 0 commentsMay 29, 2023 - While working with this circuit I noticed that there were times that reading back a bit would be incorrect. It comes down to if I have all the power leads connected and the the power supply to the cores is turned on, then a current spike seems to get into the X and Y wires even if I have not pressed the pulse button. If I first turn on the power supply then connect the power leads, the cores read back their state correctly. I need to remember this for future builds.

-

Video Presentation

05/05/2023 at 23:51 • 0 comments -

Magnetic Core Memory Circuit

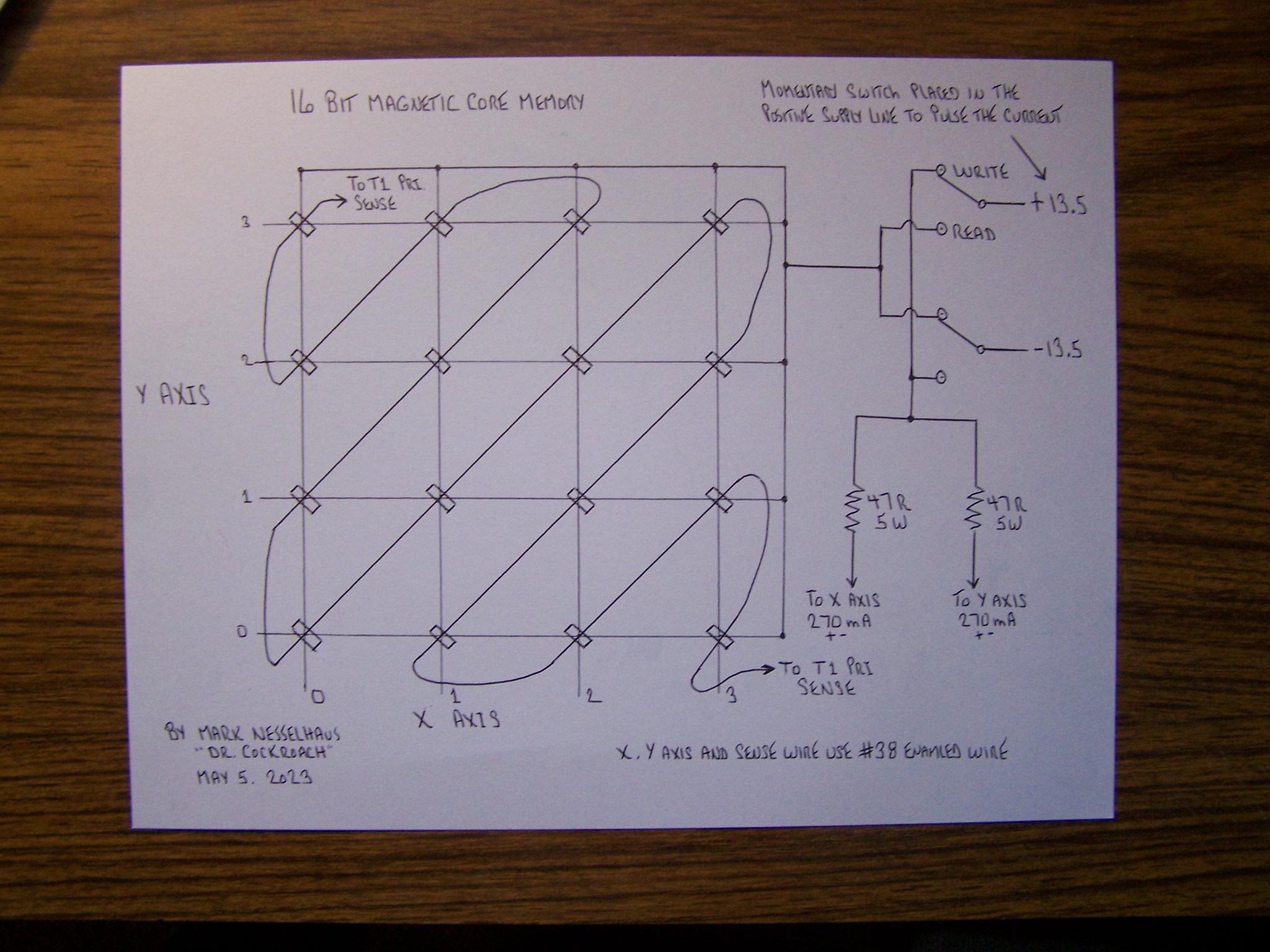

05/05/2023 at 10:51 • 0 commentsMay 5, 2023

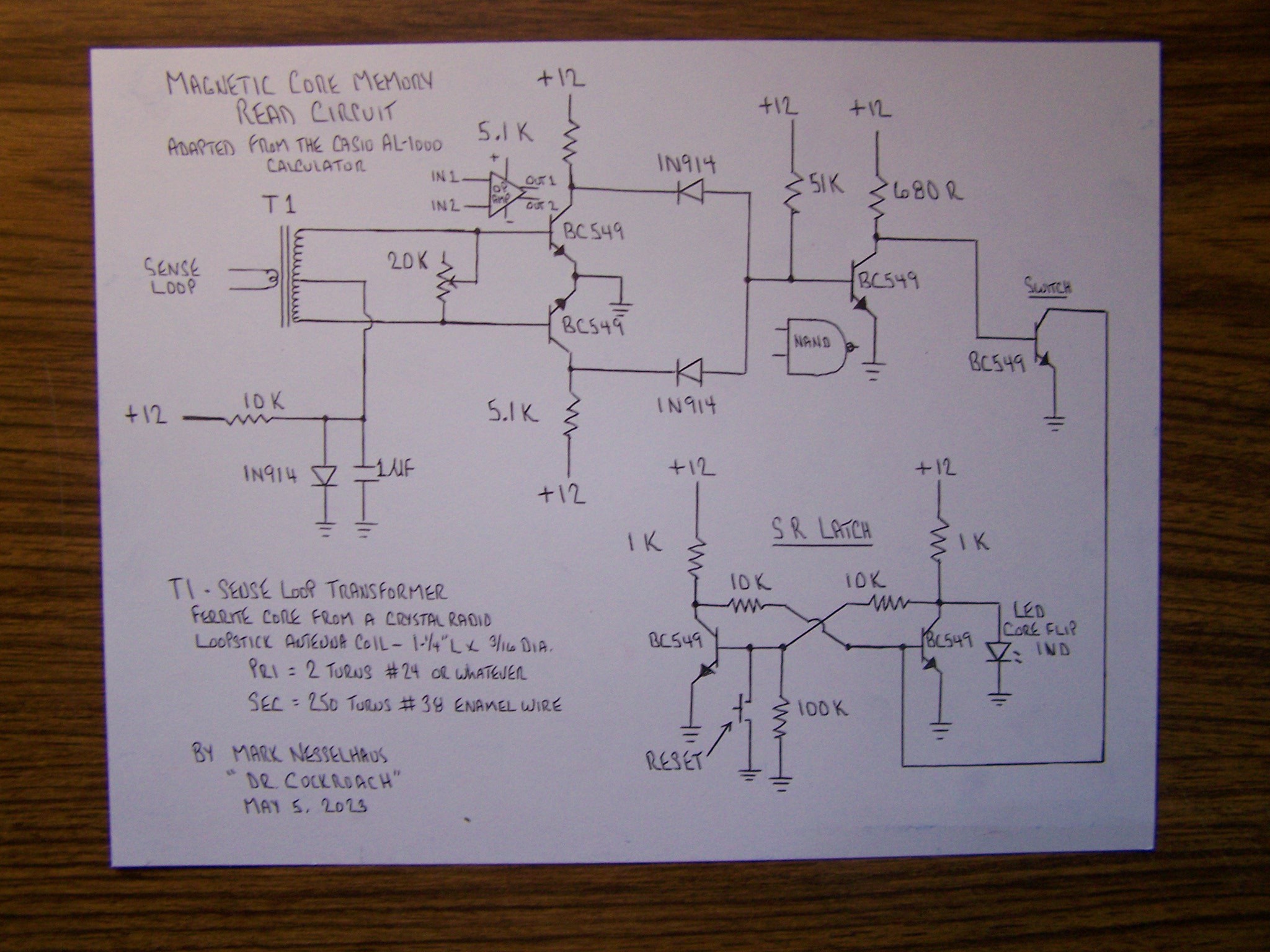

This is about as basic/bare bones of a circuit that I think will work and still give solid Read results. The stringing of the core wires using number 38 enameled wire was not as much of an issue as I was fearing.

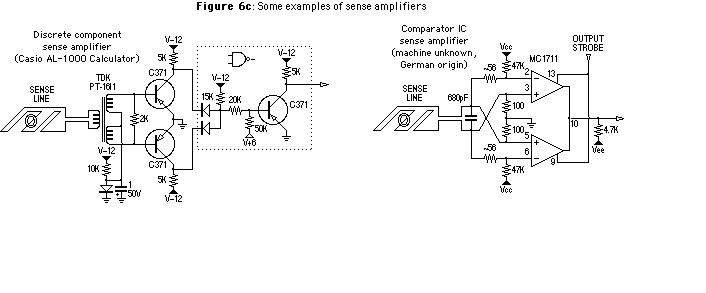

The Sense circuit starts off with the Transformer and feeds into a very basic Differential Op Amp. The detected read pulse then triggers a Nand gate and switch that then sets the S-R Latch. This circuit is adapted from the Casio AL-1000 calculator from 1967/1968.

-

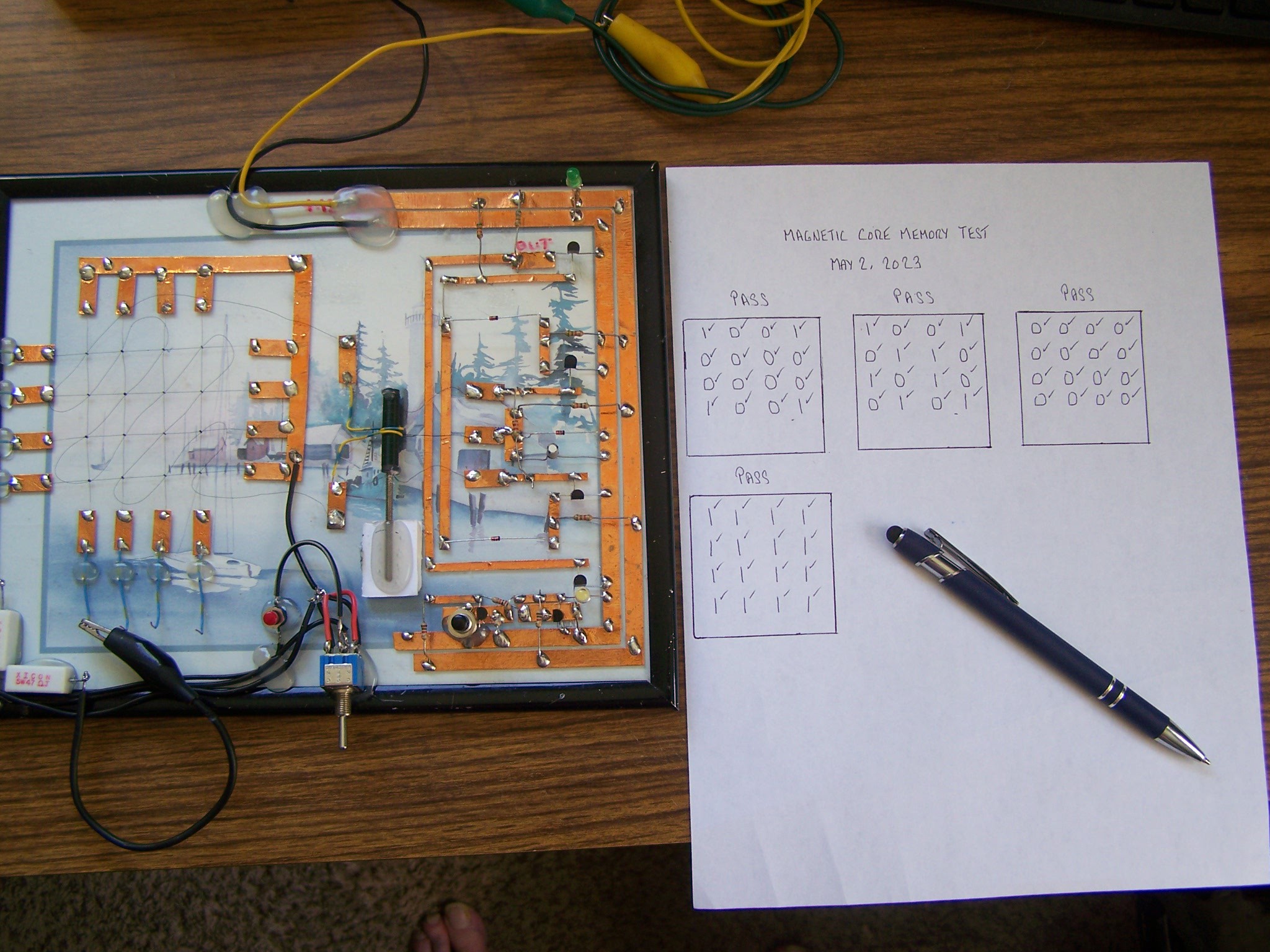

Formal Core Test Day

05/02/2023 at 19:57 • 0 comments -

Noise Spikes, I Jinxed Myself

05/01/2023 at 18:20 • 0 commentsMay 1, 2023 - Seems like I jinxed myself the other day when I stated that this core memory had worked without errors for four days. I should learn to keep my mouth shut. I started seeing glitches and dropped bits for the last two days. I checked solder joints and such and thought I solved the issues but then they started up again. Just now thought that perhaps I was seeing noise spikes getting through the power supply for the transistor section of the circuit so I have added a choke of about 100mH to the power lead. I also reduced the voltage to the transistor section from 12V to 5V and everything seems to be back in good order. Going to have to cycle the cores many times to see if all is happy once again.

Well, the glitches started up shortly after adding the choke. I took a long close look at all my solder connections and lo and behold I noticed that where two copper foils met, they were barely touching at a tiny speck of one corner and not soldered. That is now soldered and starting another round of testing. I feel good that the glitches have been solved at last.

Four hours later and still working as it should.

-

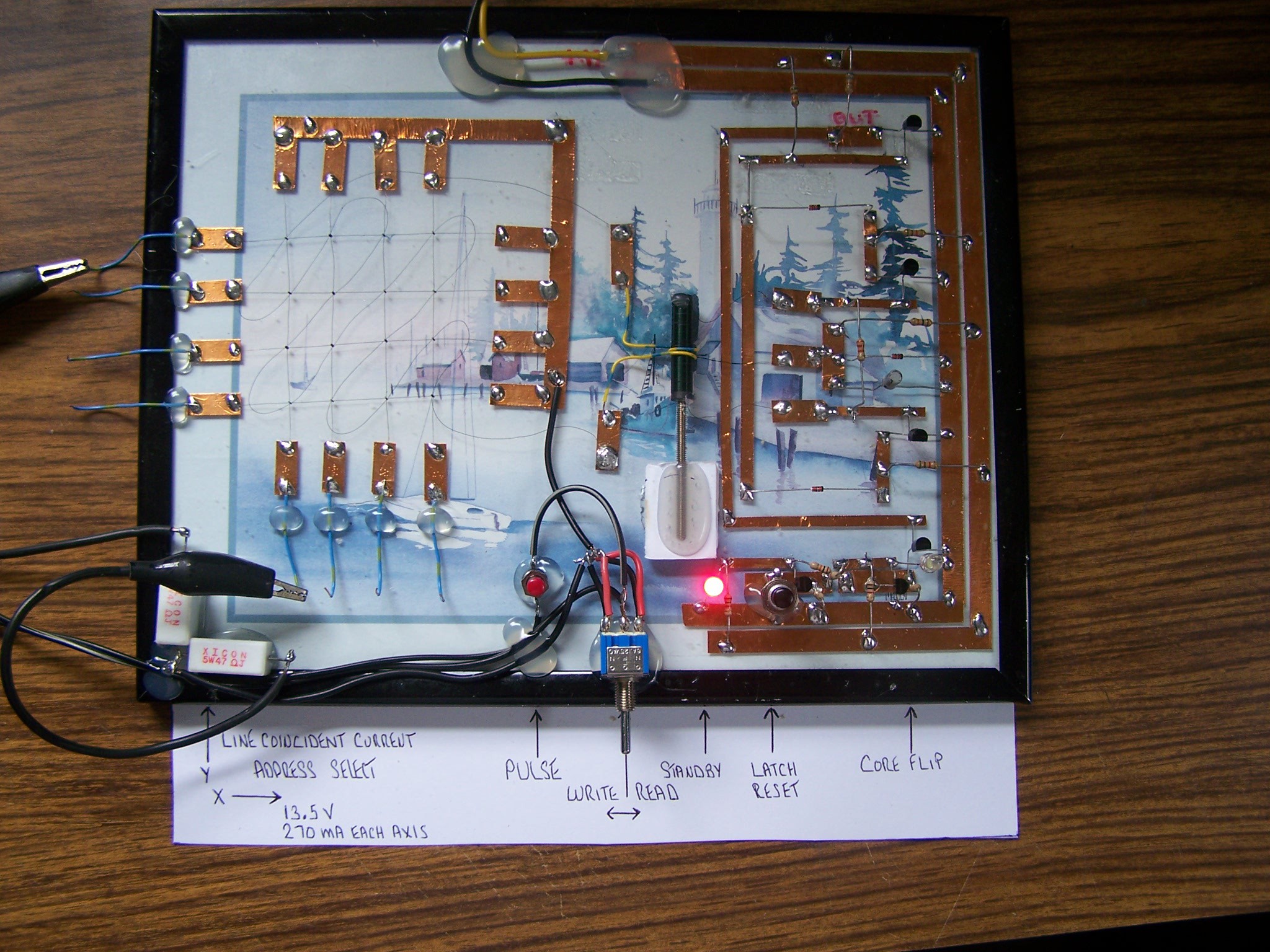

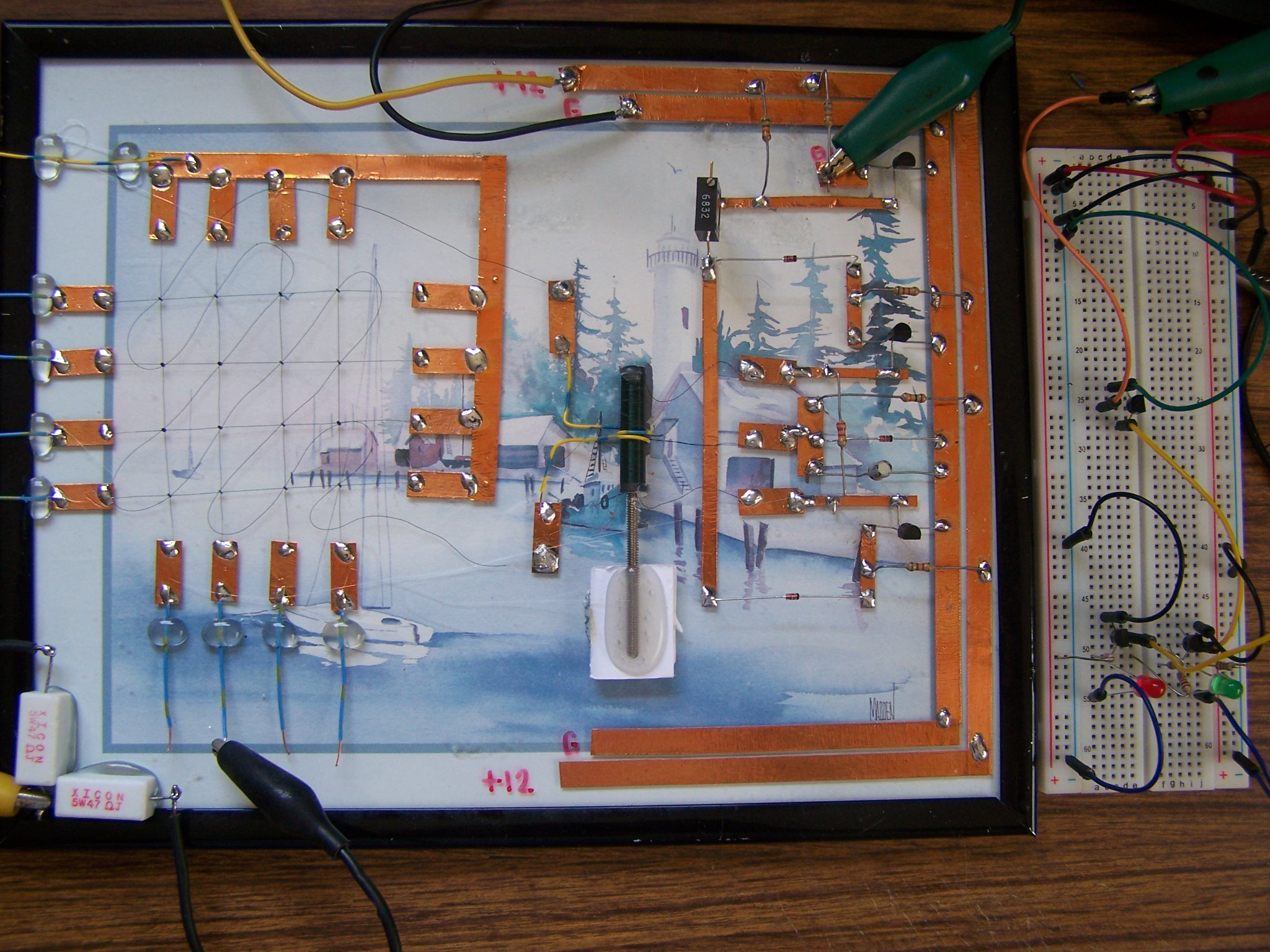

Added the SR Latch to the main board

04/28/2023 at 18:44 • 0 commentsApril 29, 2023 - Cleaning up some of the clip leads and moved the SR Latch to the main glass board. Now three days without any bit flip errors.

The SR Latch is now located at the lower right with the black reset switch to the right of the red Led. The toggle switch selects between Write and Read and the red push button switch left of the toggle sends current to the selected core via the clip leads. The clear white Led at the far right indicates a flip of the selected core.

-

Dealing with the cores

04/27/2023 at 11:56 • 2 commentsApril 27, 2023 - The cores that I bought via Ebay came from Bulgaria and I have no idea of the core material specs. Andy Geppert told me what he used as far as a voltage and current with his Core64 project so I started with that but with these cores I was not getting consistent results. With a lot of flip cycles, I am now Writing and Reading at 13.5 Volts at 270 mA in the X and Y matrix wires. The two 47 Ohm resistors actually measure out as 50 Ohms. So far today I have not had a mis-read and feeling that I am on the right track as the cores held there state overnight.

-

The Circuit at the Heart

04/25/2023 at 22:03 • 0 commentsThe very basic Sense Read circuit is directly from the Casio AL-1000 calculator. The only issue I had was the Sense Transformer as I could not find any information on the TDK part called out so I just took a wild guess and wound my own transformer. I also used NPN transistors and reversed the voltage polarity but other wise the same functional circuit. There are quite a few good articles on the internet to help learn how Magnetic Core Memory works and what is required. This is the Read portion of a three wire system where the memory Read is destructive and once a bit is read as a 1, the core flips to the reverse magnetic orientation which requires the bit to be rewriten to its prior state. In 1965 IBM patented a 4 wire non-destructive system but the timing is much too complex for this current experiment.

The voltage on the X and Y address wires is currently about 13.5 Volts @ 270 mA per active wire using a pair of 47 Ohm 5 Watt resistors, one for each axis.

I also used BC-549 NPN transistors and reversed the voltage polarity. The NAND gate circuit can be what ever you want to use.The experimental board on the right is a basic transistor switch and a SR-Latch.

Magnetic Core Memory The Dr Cockroach Way

My not so fancy example of Magnetic Core Memory using fairly cheap cores and free parts from my junk box.

Dr. Cockroach

Dr. Cockroach