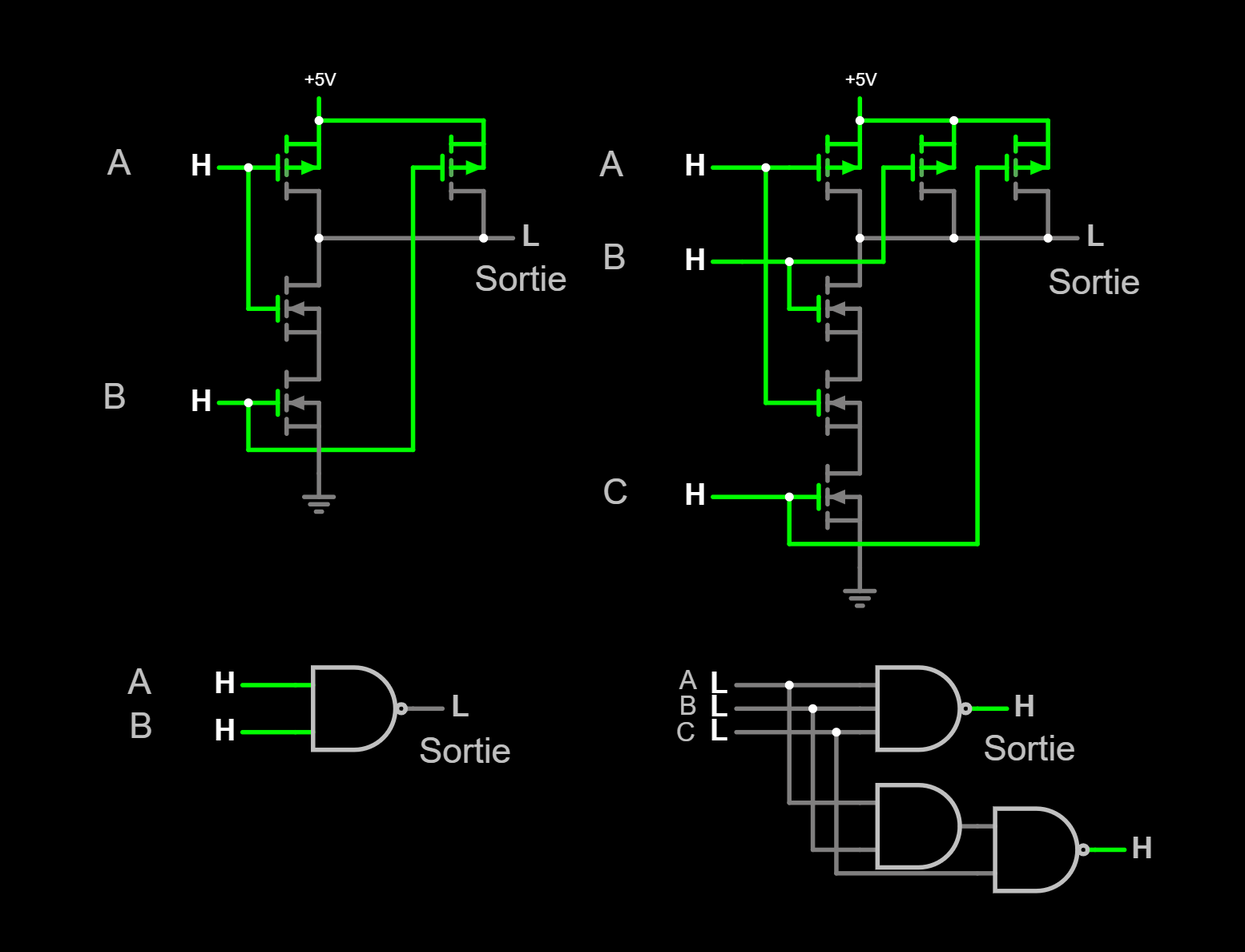

| nand2 -> nand3 | ! (A & B) | ! (A & B & C) |

Depuis nand2 on ajoute :

- Haut

- 1 pmos en parallèle(OR)

- Bas

- 1 nmos en série(AND)

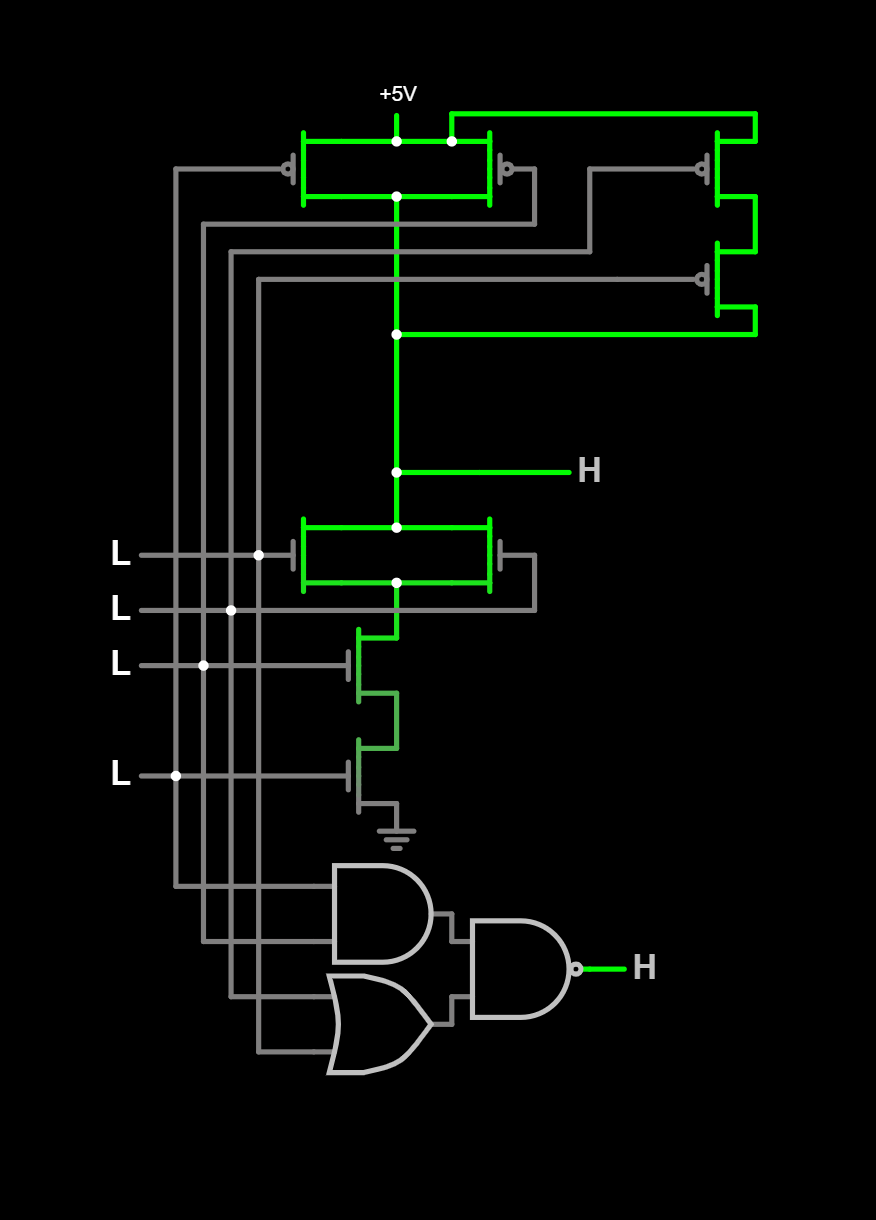

| nand3 -> aoi_2_1 | X = (A & B) !(X | C) |

Depuis nand2 on ajoute :

- Haut

- 1 pmos en série(AND).

- Bas

- 1 nmos en parallèle(OR).

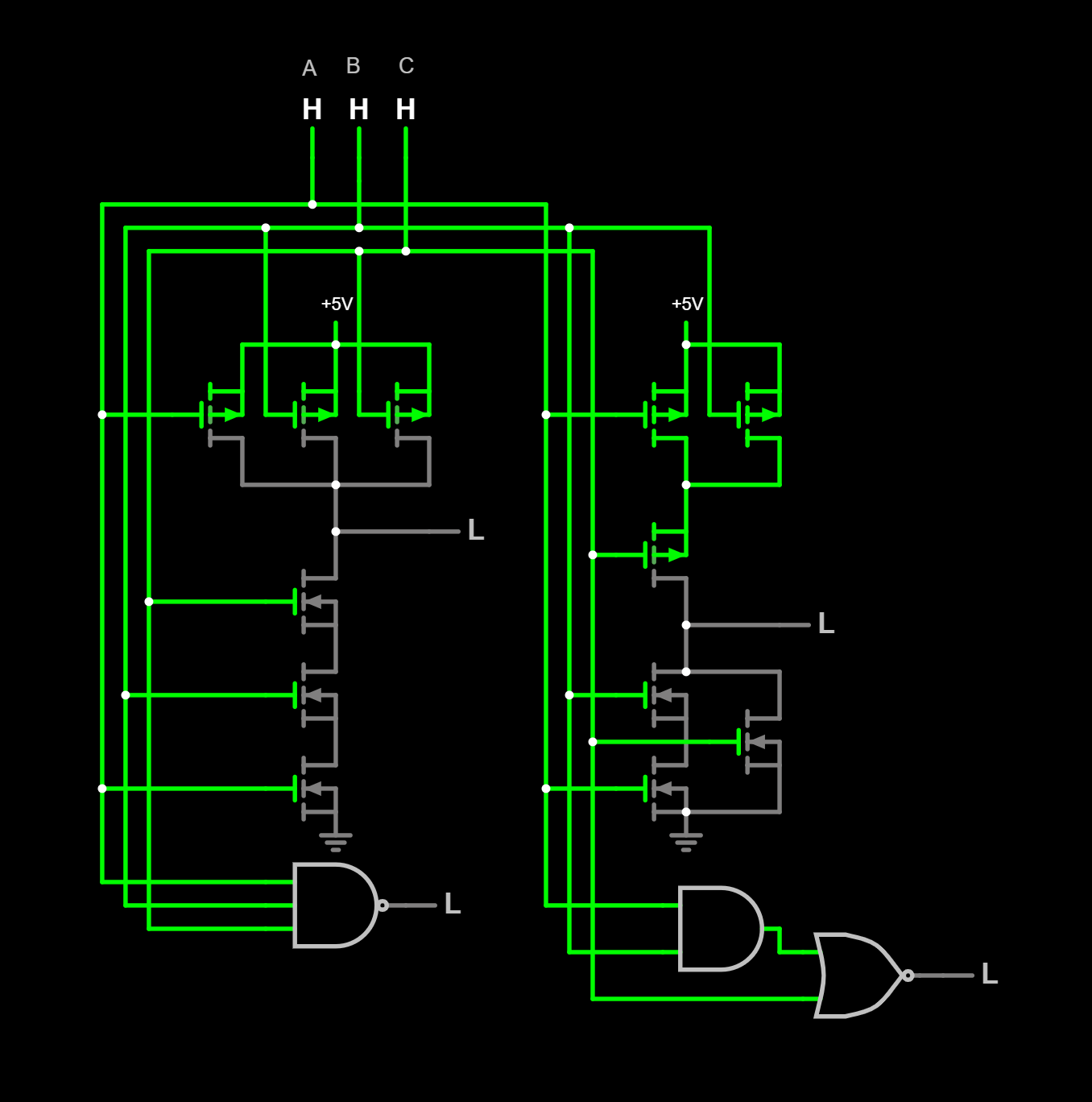

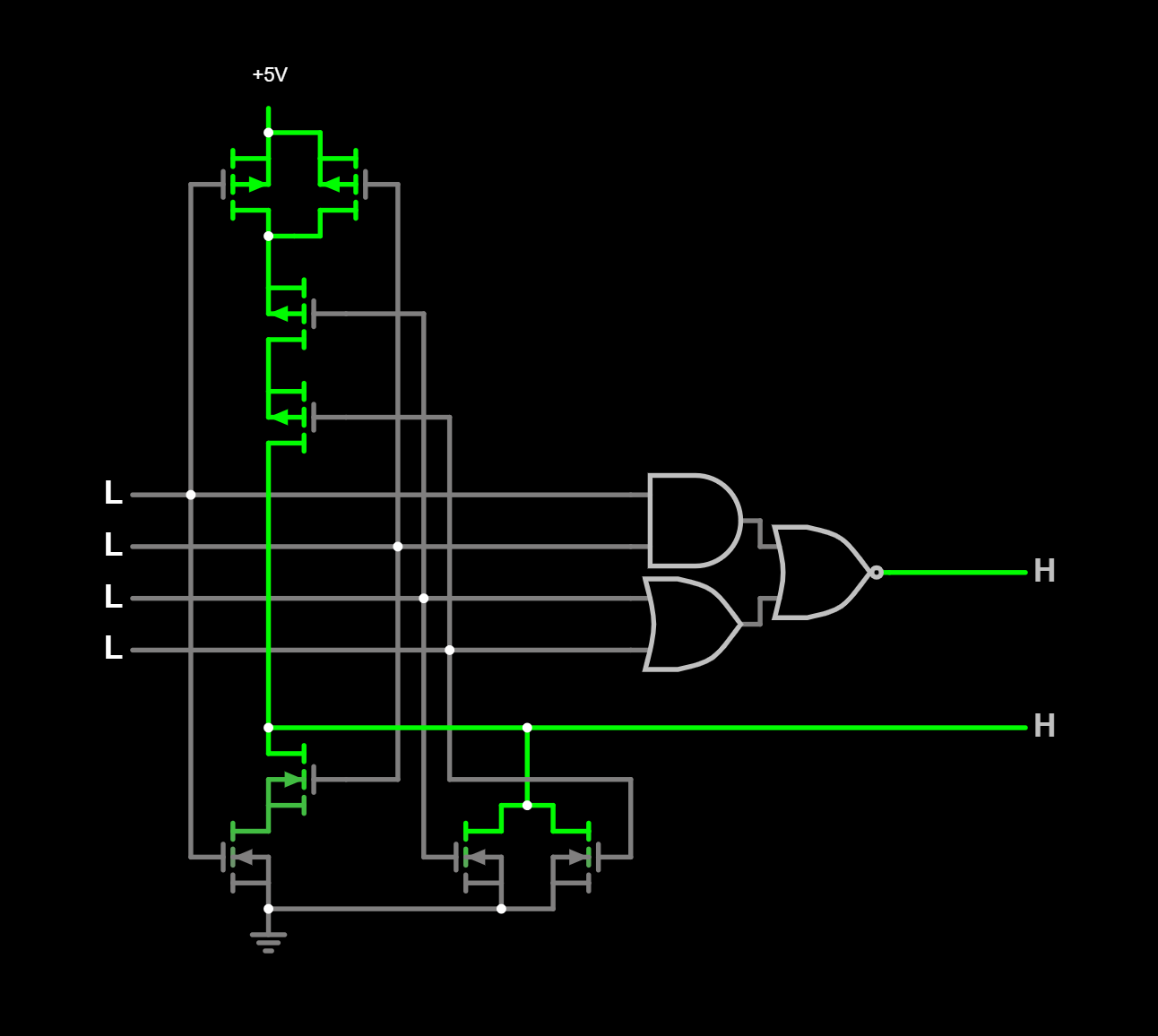

| nand3 -> aoi_2_1 -> aoi_2_2 | X = (A & B) Y = (C & D) ! (X | Y) |

Depuis nand2 on ajoute :

- Haut

- 2 pmos parallèle(OR) en série(AND).

- Bas

- 2 nmos série(AND) en parallèle(OR).

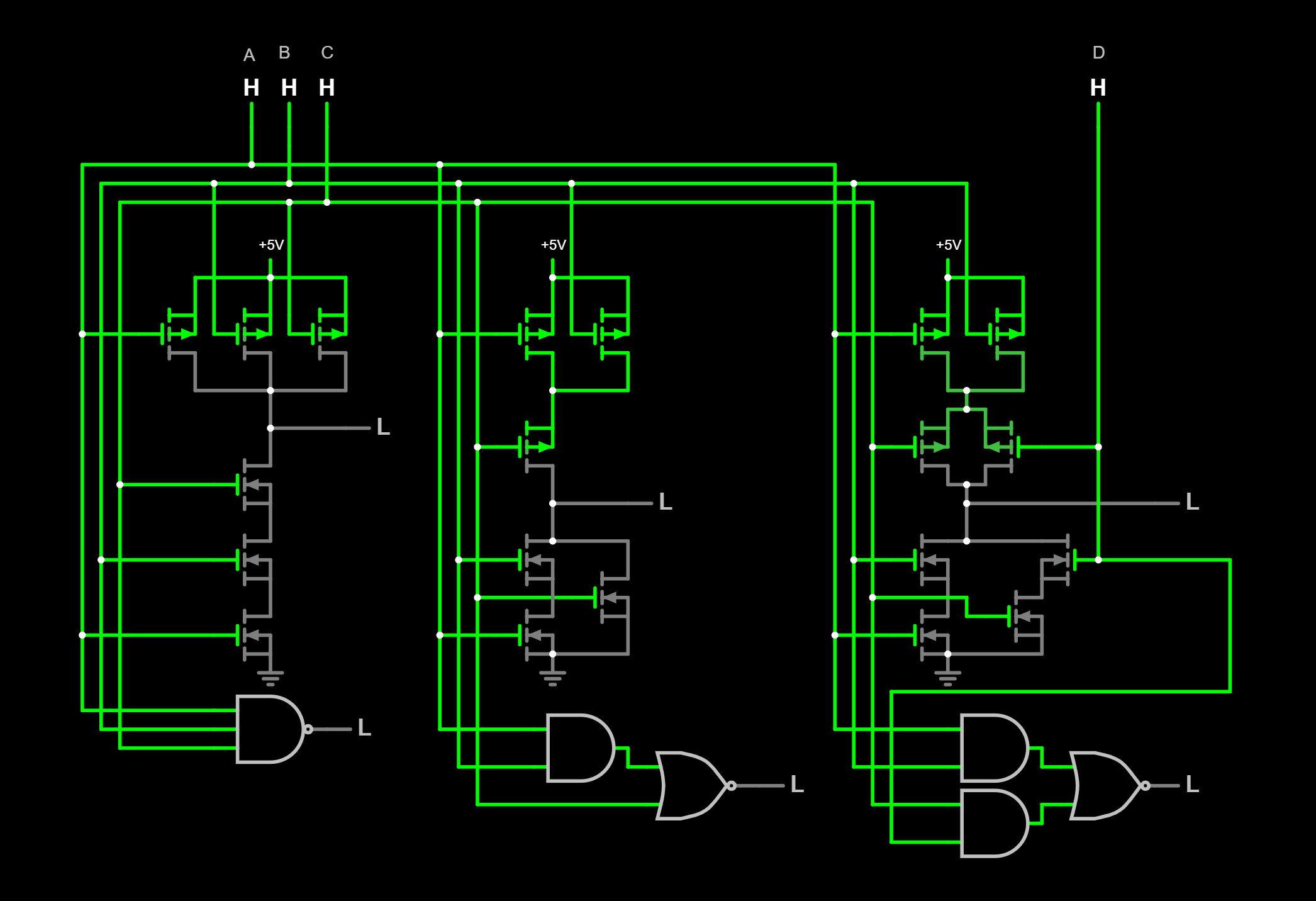

| aoai_3_2_1 | X = (A & B & C) Y = (D & E) Z = ( X | Y) ! ( Z & F) |

Ce circuit contient :

- Haut

- 3 pmos parallèle(OR).

- 2 pmos parallèle(OR) en série(AND) du OR.

- 1 pmos en parallèle(OR) des 3 gates du dessus.

- Bas

- 3 nmos série(AND).

- 2 nmos série(AND) en parallèle(OR) du AND.

- 1 nmos en série(AND) des 3 gates du dessous.

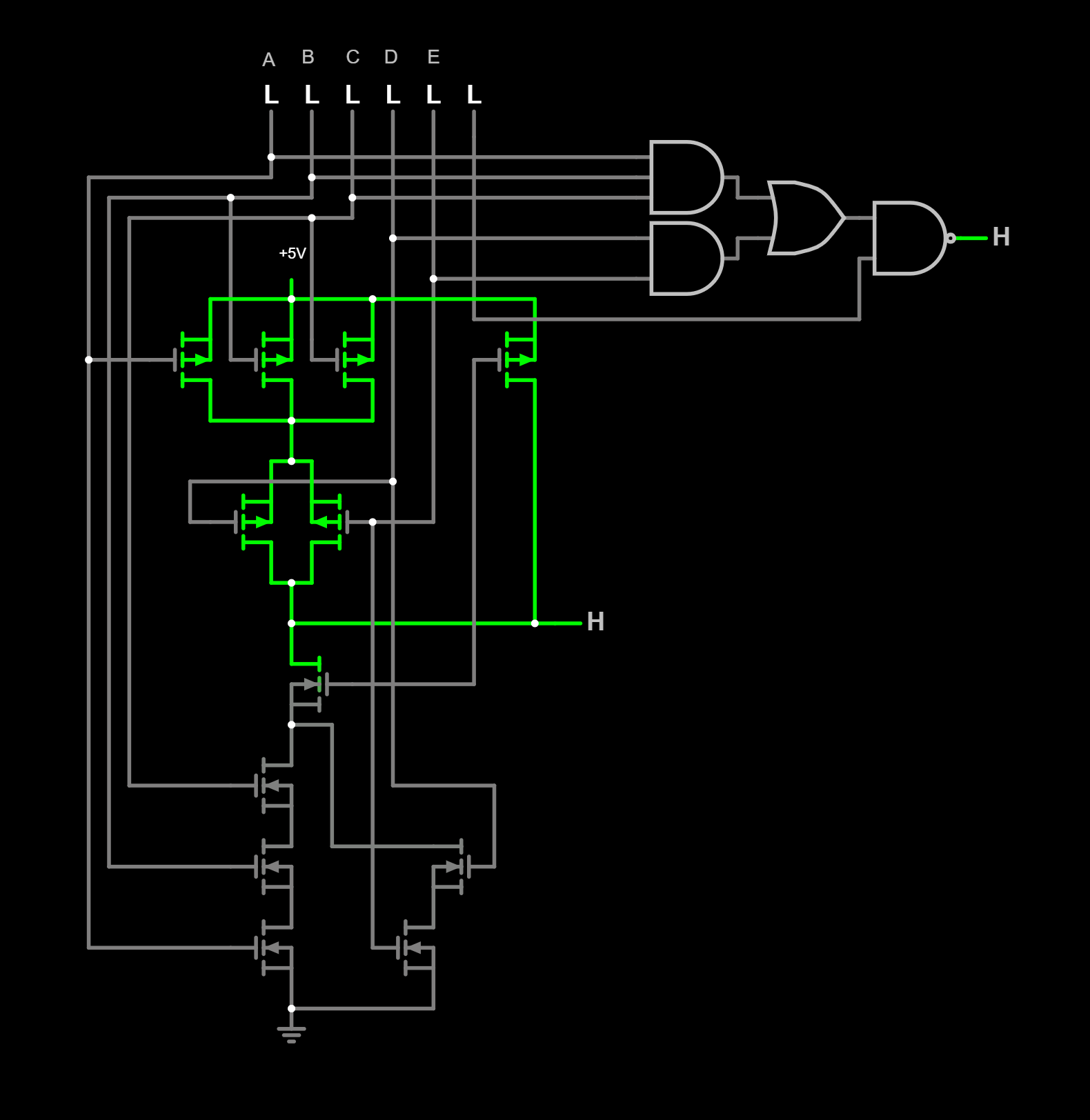

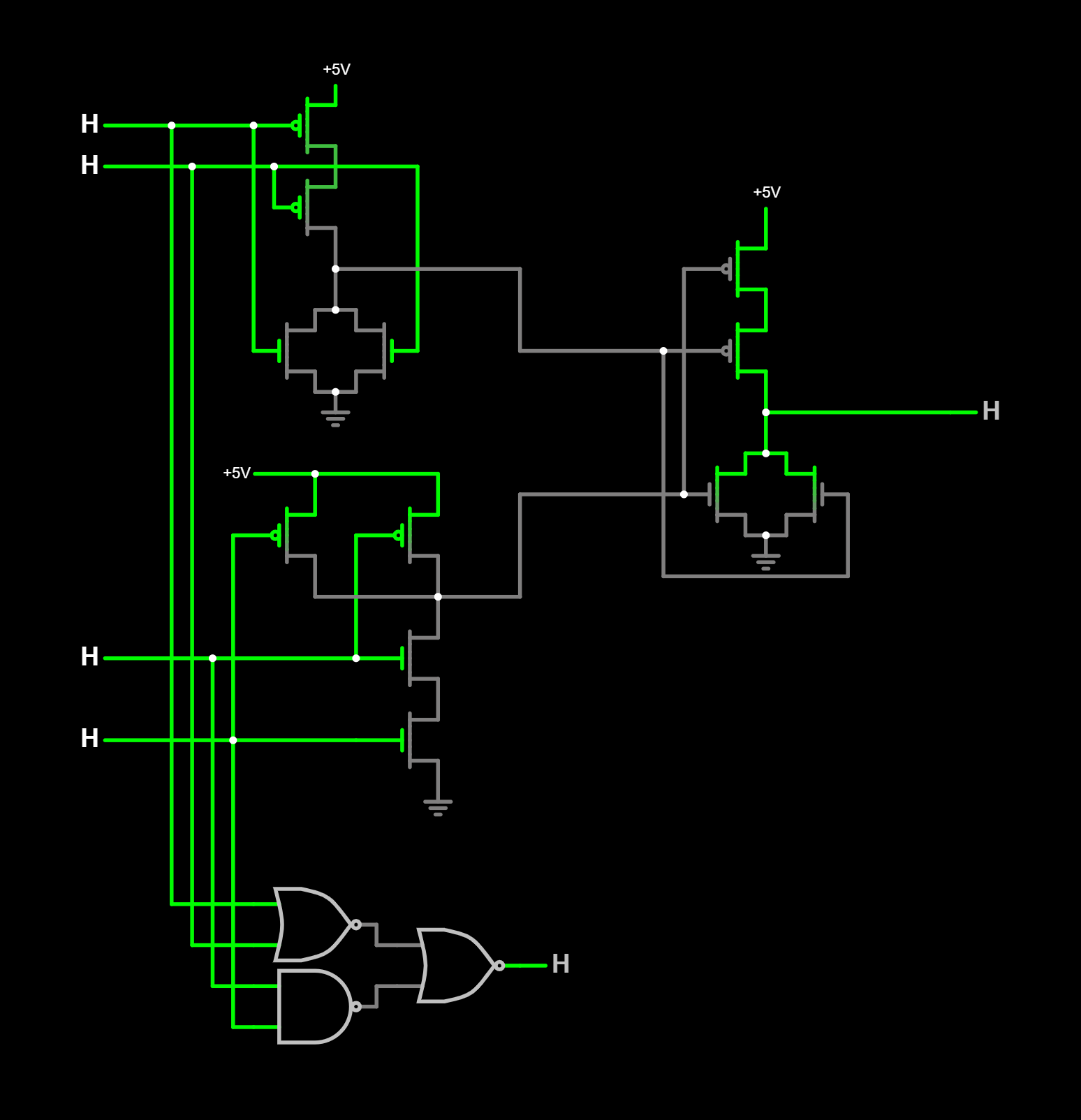

| mixed_NAND |

Ce circuit contient :

- Haut

- 2 pmos parallèle(OR)

- 2 pmos série(AND) en parallèle (OR) du OR

- Bas

- 2 nmos série(AND)

- 2 nmos parallèle(OR) en série(AND) du AND

| mixed_NOR |

Et on inverse mixed_NAND !

Ce circuit contient :

- Haut

- 2 nmos parallèle(OR)

- 2 nmos série(AND) en série(AND) du OR

- Bas

- 2 pmos série(AND)

- 2 pmos parallèle(OR) en parallèle (OR) du AND

Constat :

- Ajouter un cmos en séries reviens a ajouter une gate AND.

- Ajouter un cmos parallèles reviens a ajouter une gate OR.

- Ajouter 2 cmos (AND / OR) en série(AND) ou en parallèle(OR), reviens a ajouter 2 gates.

- Toute jonction entre nmos et pmos donne lieu a une inversion du résultat.

- Le dernier niveau est l'inverter (il met automatiquement fin au circuit).

- Inclure une NAND ou une NOR dans un niveau implique un inverseur (fin du circuit).

- L'on peux utiliser ces inverseurs afin de concevoir une combinaison de gates qui mélange les and et les OR dans le même niveaux !

- Cependant cela reviens a utiliser 3 porte logique, et n'est donc d'aucun intérêt.

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.

I have think with a matrix !

I have start a experimental project where you enter your algebre and its make your configuration.

Are you sure? yes | no

The last gate has 4 transistors in series on the lower leg... so it must be used sparingly I guess.

But the others aoi_3_1_1 and aoi_3_2 are good arguments to extend #Libre Gates to support a LU5.

Are you sure? yes | no

Yes its true !

If you start with this logic, you can extend without end your LU (aoai_3_2_1)

Are you sure? yes | no

Using some graph theory, it might be possible to enumerate all configurations of series and parallel arrangements up to X transistors in series...

Oh wait, it's a trap ! you got my gears started and now I have to do it :-(

Are you sure? yes | no