Le log Expansion des portes logique en cmos a dégagé plusieurs règles de construction, qui s'ajoutent à la métrique FO4.

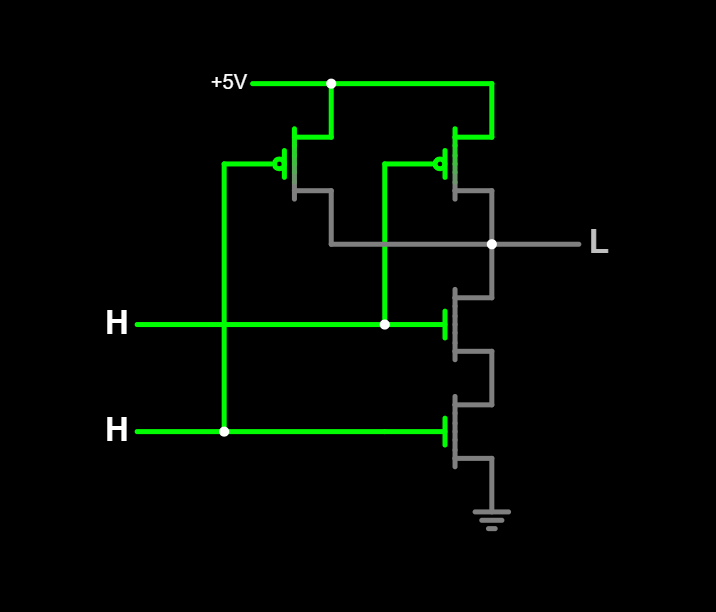

Cependant dans une implémentation physique il existe un paramètre supplémentaire : la profondeur maximale des transistors, ou le nombre de transistors qu'on peut mettre en série.

C'est une conséquence du fait que chaque transistor a une résistance à l'état passant. Cette résistance affecte la performance et mène a des compromis entre :

- surface

- vitesse

- consommation

En suivant la règle t=RC, augmenter la résistance diminue la fréquence de fonctionnement. il devient donc nécessaire de définir le nombre maximal de transistors, "Tmax", admis en série.

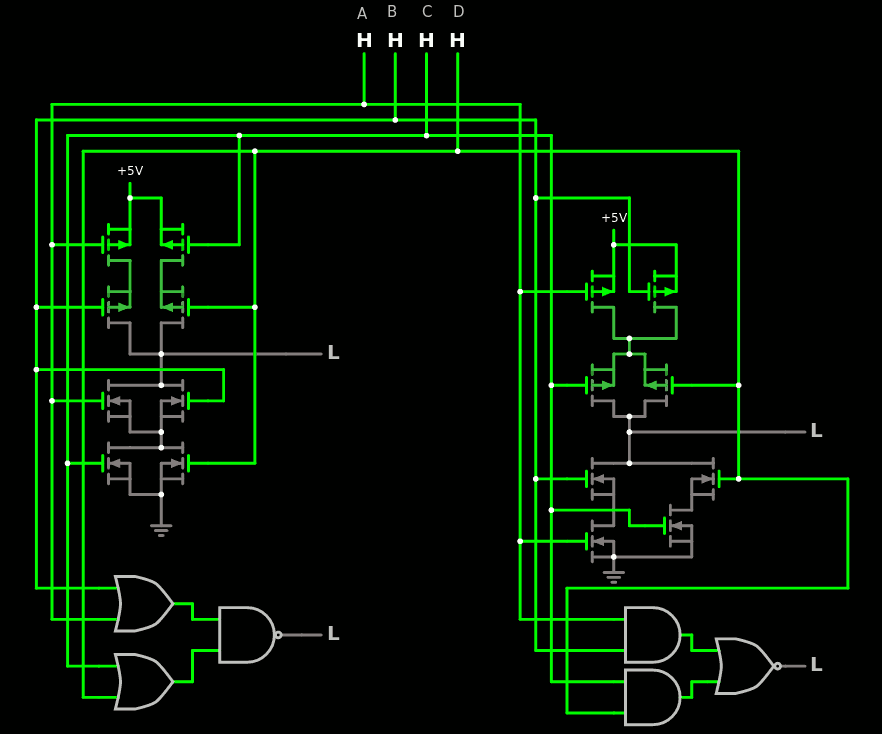

Pour cela nous allons utiliser une matrice de cmos, car ce qui se trouve en série en haut, se trouve en parallèle en bas !

Ainsi une complexité Tmax = 1, est un inverseur (1x1).

Pour Tmax=2, cela donne une porte à 4 entrées (2x2)

Matrice que l'on peux ensuite élaguer pour donner une NAND ou une NOR simple.

Tmax=3 donne un bon compromis en terme de complexité et de complexité de routage, si on limite le nombre d'entrées, car ce dernier peut monter à 3×3=9.

Ces configurations "maximales" ont deux avantages :

- D'abord, chaque entrée séparée a un fan-in de 1 donc pas besoin d'ajouter un inverseur pour booster en enrée de la porte. (Par contre si un signal va sur plusieurs entrées, il faut soit ajouter un inverseur en entrée, soit en tenir compte en amont)

- Ensuite, la matrice des "configurations maximales" peut être réduite à volonté. On peut ainsi construire n'importe quels autre configuration plus petite en élaguant des entrées. Et donc, on choisit si chaque noeud est un AND ou un OR en prenant l'équation booléenne a l'envers, puis on élimine le superflu.

L'utilisation de profondeurs plus grandes a un avantage si cela permet de réduire la profondeur logique du circuit (le nombre de nœuds d'inversion traversés pas une entrée vers la sortie).

Par exemple,

Un OR4 prendra moins de place et peut-être un peu moins de temps que deux 0R2 en série. Mais les fronts seront plus lents !

C'est en effet un compromis à trouver et à tester, en fonction des caractéristiques de la technologie.

Mais surtout, il faut aussi limiter le nombre d'entrée car sinon, la cellule correspondante devient trop grande et difficile à router.

Conduisant au débordement probable sur un autre niveau de métal.

Une limitation à 4 entrées est un bon début mais ce n'est pas une limite absolue puisque nous voyons plus haut que pour atteindre un compromis de Tmax=3, on peut monter à 9 entrées et de nombreuses portes à 5 ou 6 entrées peuvent être très utiles.

Le layout de la cellule correspondante peut devenir difficile.

Les PDK "minimalistes" (type OSU) permettent de synthétiser la plupart des circuits courants mais il est plus efficace de synthétiser les portes à la demande, en fonction du circuit.

C'est plus lourd mais la performance demande toujours plus d'efforts !

Yann Guidon / YGDES

Yann Guidon / YGDES

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.

Citation :

La vitesse de l'information est la vitesse de la lumière dans le milieu, soit environ 273'000km/s dans le cuivre (courant électrique dans un fil)

Je crois savoir que la fréquence de fonctionnement dépend de la célérité de propagation du champ électrique dans le milieu (cuivre, silicium, etc).

Serait-il possible de développer un peux ce sujet ?

Exemple :

La célérité du champ électrique dans le cuivre est de 273'000'000 m/s.

Cela veux donc dire qu'en 1 ns, elle peux traverser 273 mm de cuivre.

Ainsi pour un "circuit" fais d'une unique ligne de cuivre de 273 mm,

La fréquence de fonctionnement maximal, serais de 1 ghz.

Question :

Quel est le rôle de la résistance la dedans ?

Aurais-tu un lien expliquant t=RC ? (google n'est pas très clair).

Pourrais tu donner un exemple concret avec un circuit de référence quelconque ?

Are you sure? yes | no

à toi de créer un nouveau log à ce sujet, je te laisse ouvrir le bal :-)

Are you sure? yes | no

Très instructif !

Merci camhackade !

Are you sure? yes | no

De rien !

Are you sure? yes | no