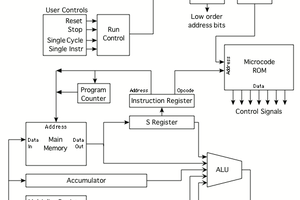

About this project

In 1838-1858, Charles Babbage designed a programmable (punch card) digital mechanical computer, the analytical engine, with conditional branching and loops. It was never built, as it was too difficult.

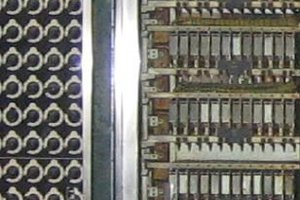

From 1938 to 1941, Konrad Zuse built a programmable (35 mm film) digital electromechanical computer (relays). It worked (22 bits floating point), but had very limited capabilities (no jumps, no tests, no subroutines).

After seeing a replica of the Zuse Z3 in Berlin, I thought: Babbage had the idea but not the technology, Zuse had the technology but not the ideas. What if Zuse had had the ideas?

This project is about designing circuits that could have been made with the technology available at the time (i.e., no semiconductors). Whether I will actually build a computer with it is undecided yet.

General technology

These circuits assume 3 logic states: 0 (GND), 1 (=relay activation voltage), Z (high impedance). The 0 and 1 should be able to source and sink the current of a number of relays (limited by relay contact current). Relay settling time is represented by the letter T (e.g. 5 ms, likely slower for pre-1940 relays). Pre-1940 there were no reliable diodes, relay coils should have something to damp large voltage spikes. A small neon bulb over the coil limits the spike for my relays to about 125V, a R of coil resistance and C of 10 nF in series over the coil limited it to about 225 V. Measurement with an oscilloscope shows neither method slows relay settling time (a diode does). This damper circuit is not shown in the circuits.

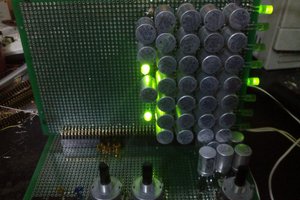

All relays are 2 form C (DPDT), because they are easy to get now. Pre-1940 4 form C (4PDT) would be available, and save quite a few relays in certain circuits, like the DRAM/ROM address decoders.

Tools used

- Circuit drawings: KiCad, can do PCB drawings too (but cannot simulate relays).

- Simulations: circuitjs. Not all circuits might have simulation files. circuitjs1 offline use: https://www.falstad.com/circuit/offline/

circuitjs1 online use https://www.falstad.com/circuit/

- Timing diagrams: wavedrom-rs https://github.com/coastalwhite/wavedrom-rs/releases

Clock generator

Choose R1 so that the relay reliable engages.

R2 is ideally such, that the parallel resistance of the relay coil and R2 equal R1. In the example, 1500 parallel with 700 gives 477 ohm.

R2 determines duty cycle (within limits), I got 75+85 ms per cycle. Different relays will need different component values.

C1 determines frequency, in my test I selected for 6 Hz. Lower C1 values give higher frequencies, but the relay switch time becomes a larger part of the total cycle time.

If the clock generator drives only a single DPDT relay, that relay can be wired to provide both clock and inverse clock, with some small dead time between the two due to relay switching time.

With another relay one could at selected times add Cs parallel, to lower frequency, when a slower clock is desired e.g. for a slower circuit. Such a C should always be connected to GND at the minus side, and permanently fed at the plus side via a high resistance value (say, 1 M Ohm) from a voltage equal to the lowest voltage on the relay, to prevent wrong pulses when it is switched parallel to the existing C.

Latch with clear

This 2 bit latch uses the fact that the hold current of a mechanical relay is lower than the activation current. VDC is the relay voltage.

Choose R1 and R2 so that the relays reliably holds. In my tests, with 24V/700ohm relays, 1k2 ohm gave the minimum hold voltage according to the datasheet, but my relays held fine with 1k8 too. It saves considerable energy too, when in hold mode.

If the "write" relay is activated, input data (here D0 and D1) is connected to the associated latch relay. If the input is VDC, a latch relay will be activated if it was not, otherwise it stays activated. Once activated, it stays activated if K1 is de-activated because of the R. During the latch relay activate time...

Read more » MatNieuw

MatNieuw

Yann Guidon / YGDES

Yann Guidon / YGDES

Stefano

Stefano