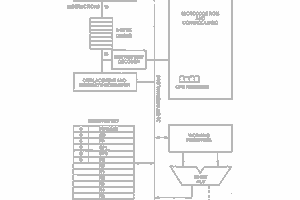

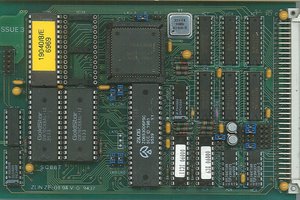

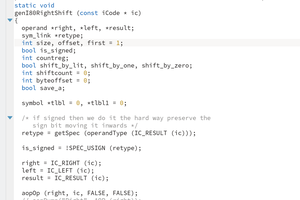

Overtly, this project provides a disassembly listing of the Cefucom-21 system, which is a vintage Computer-Aided lnstruction device (c. 1982) for teaching English to native Japanese speakers.

Who would care about such? Maybe no one, unless you have one of these rarities and want to hack.

Less overtly, this project is a chronicle of of my activities and discoveries along the way, which is useful for me to record, but I though could be interesting to someone else to see the process, so I decided to publish it here instead of in my usual private journal.

It will be a little bit of a challenge in that I do not have the hardware, nor schematics. Just the ROM dumps. Well, and some photos of the boards, which are immensely helpful. And also now knowledge that this system is based on a then-existing general-purpose system -- the Sanyo PHC-25. That system itself is pretty obscure as it seems to have done poorly in the marketplace.

But the fun is in figuring things out, so those handicaps add something....

ziggurat29

ziggurat29

Keith

Keith

Ken Yap

Ken Yap

I'm currently working on emulation of the CEFUCOM, and have the majority of the hardware mapped to IO ports. I'm interested in your interrupt findings, and anything you can work out about how the two Z80 boards communicate with each other via the Z80PIO's.