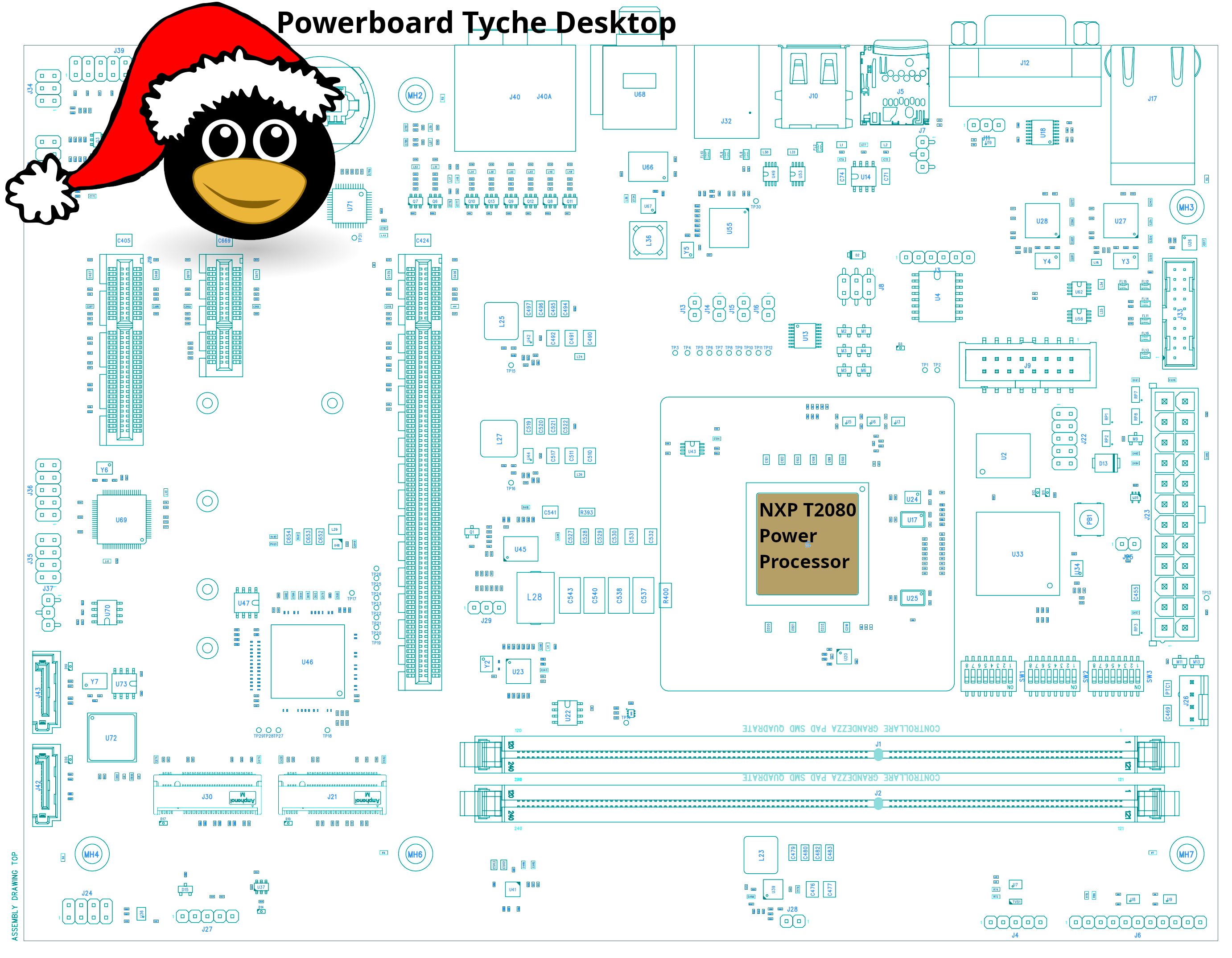

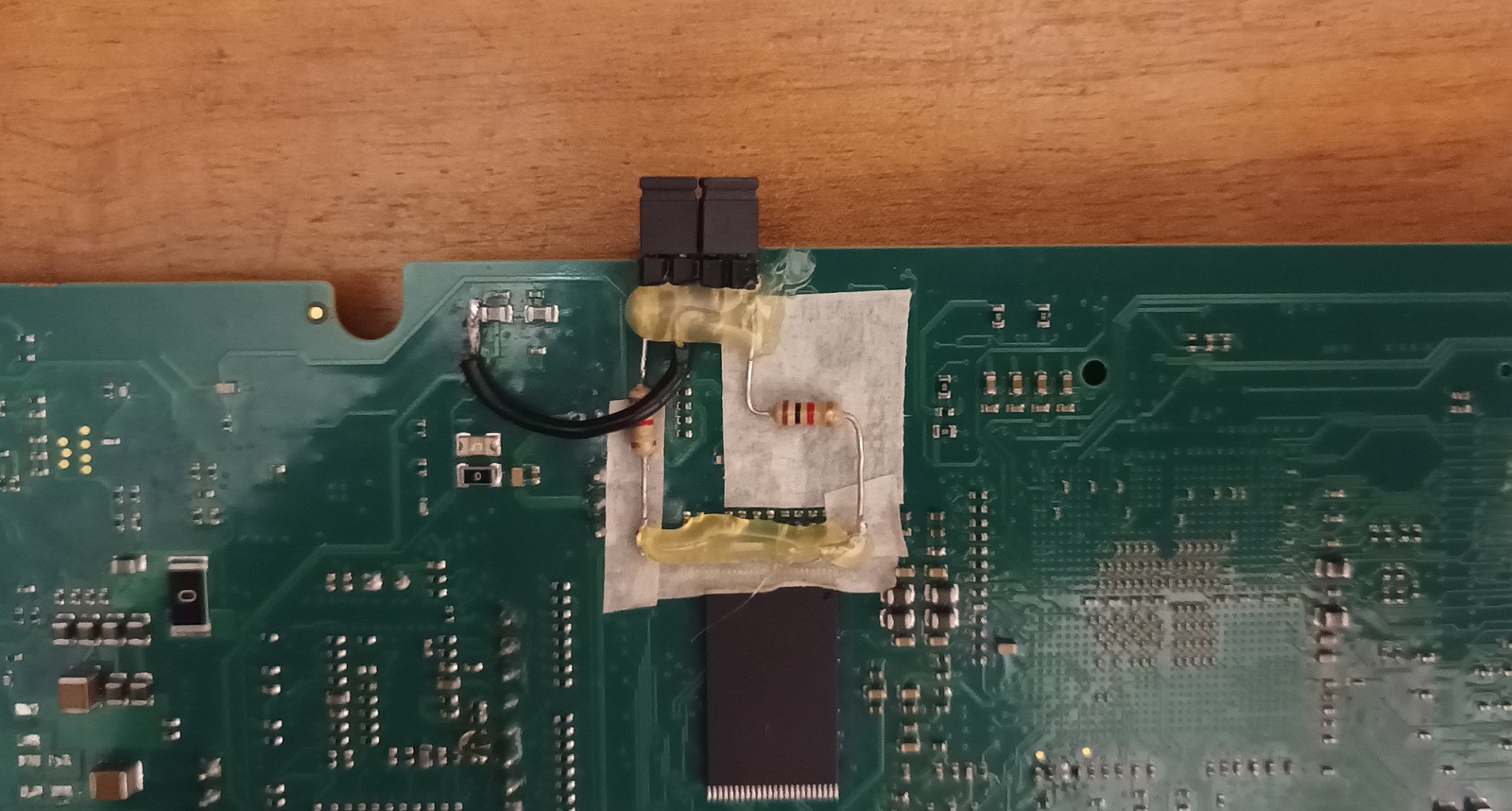

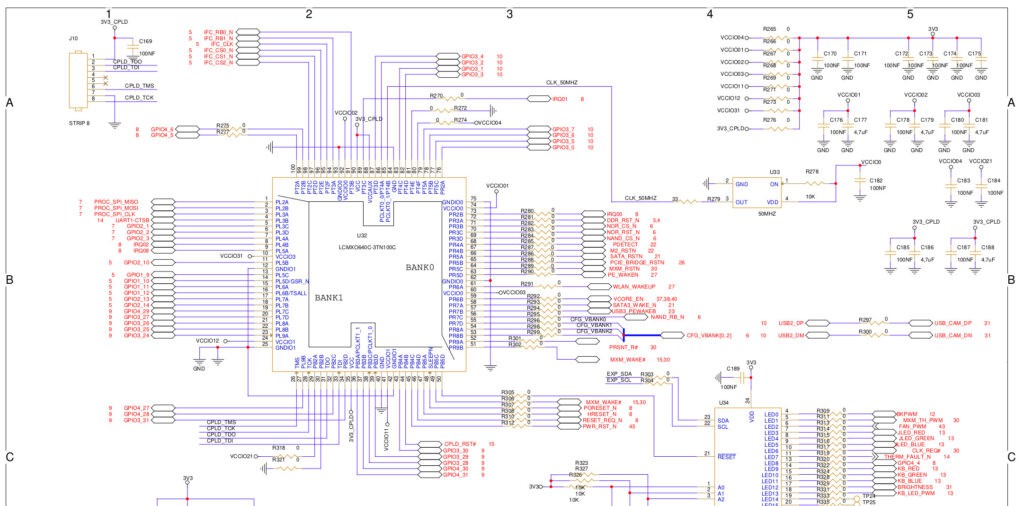

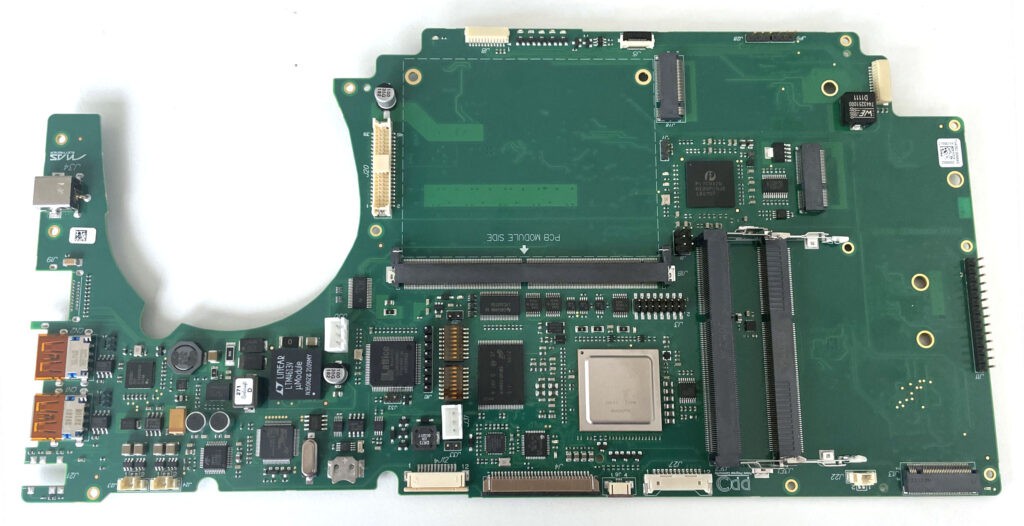

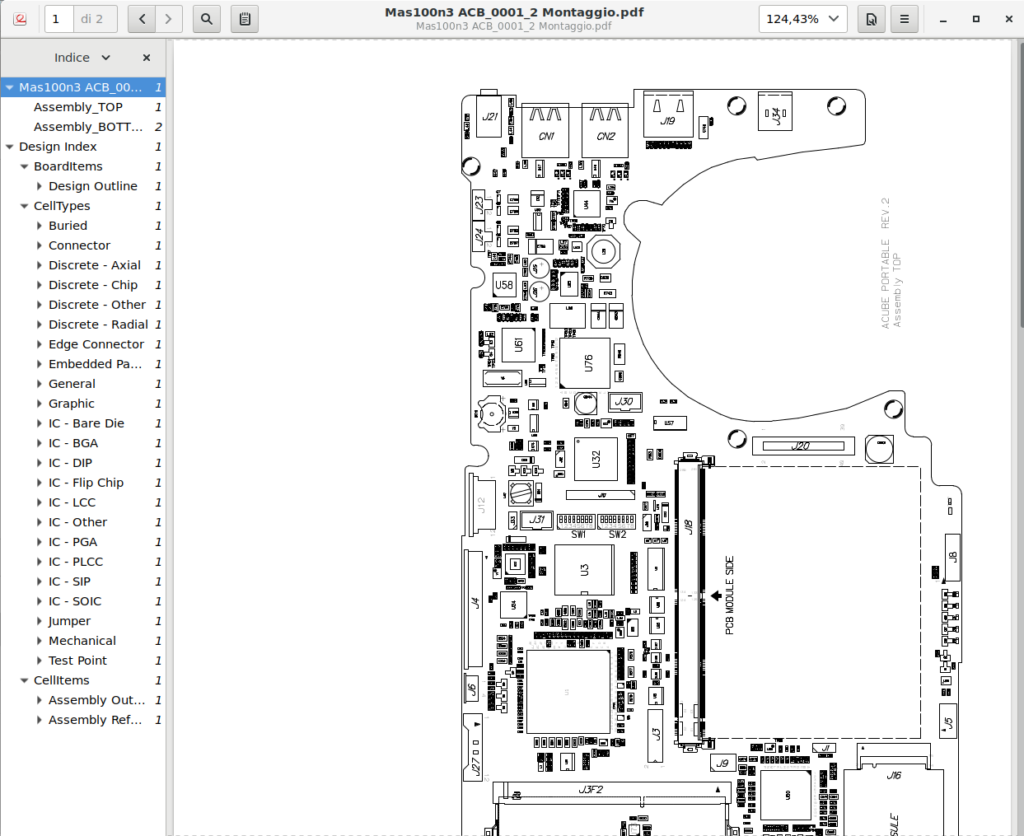

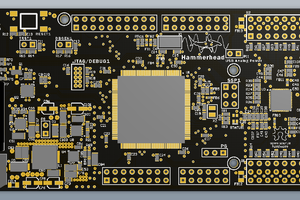

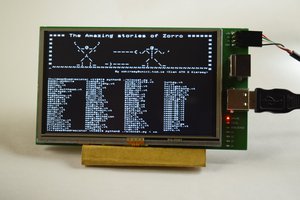

We are in the process of building an ethical purchasing group aimed at commissioning a notebook based on the PowerPC platform. The design is Open Hardware with CERN license 1.2, and the notebook will support Linux natively.

The choice of a small and local producer for making this notebook is both an ethical and forced choice, as on the Italian territory it was the only PowerPC experienced company matching our criteria based on the paradigms of an economy based on the human beings and not on a pure financial gain. We strongly feels that where you can find passion and cooperation making money is not the reference value, and for the selected company it is enough to gain just a little margin, solely aimed at maintaining the company running.

The community that is shaping around this project is much more than a classical ethical purchasing group as, in addition to collecting the necessary funding for producing the notebook, is actively contributing to making possible that GNU/Linux and other operating systems will be fully supported.

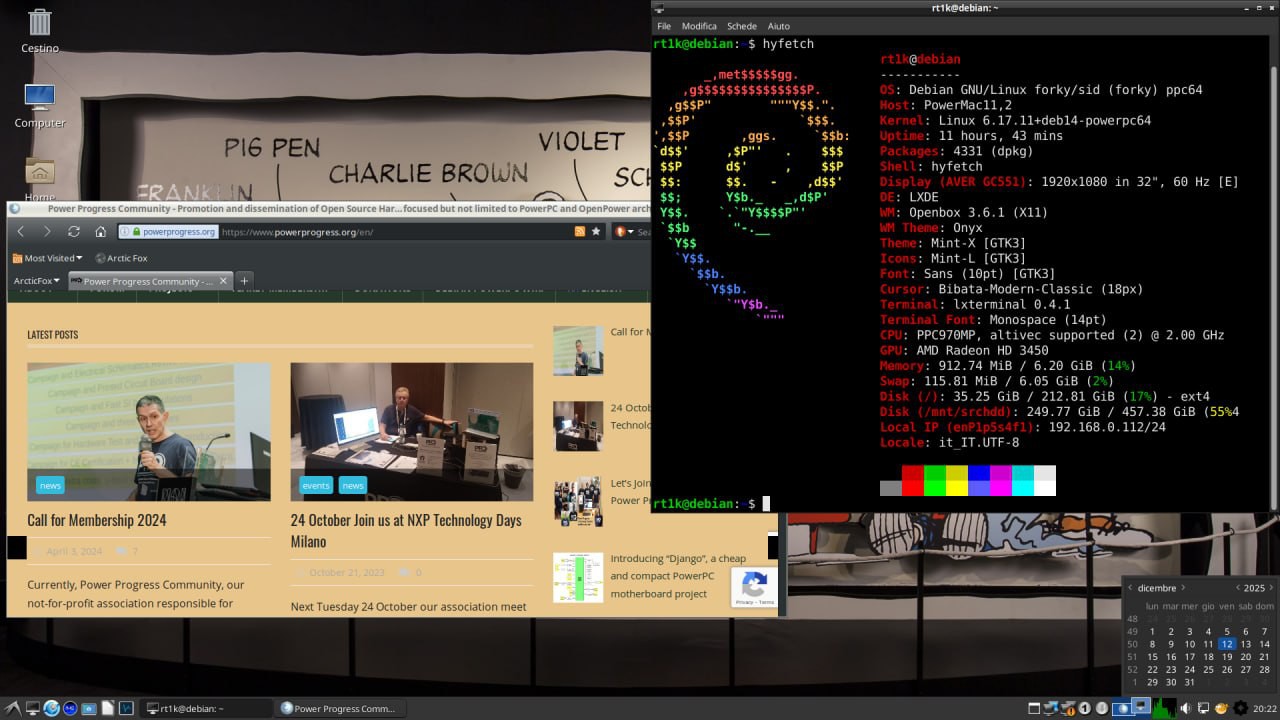

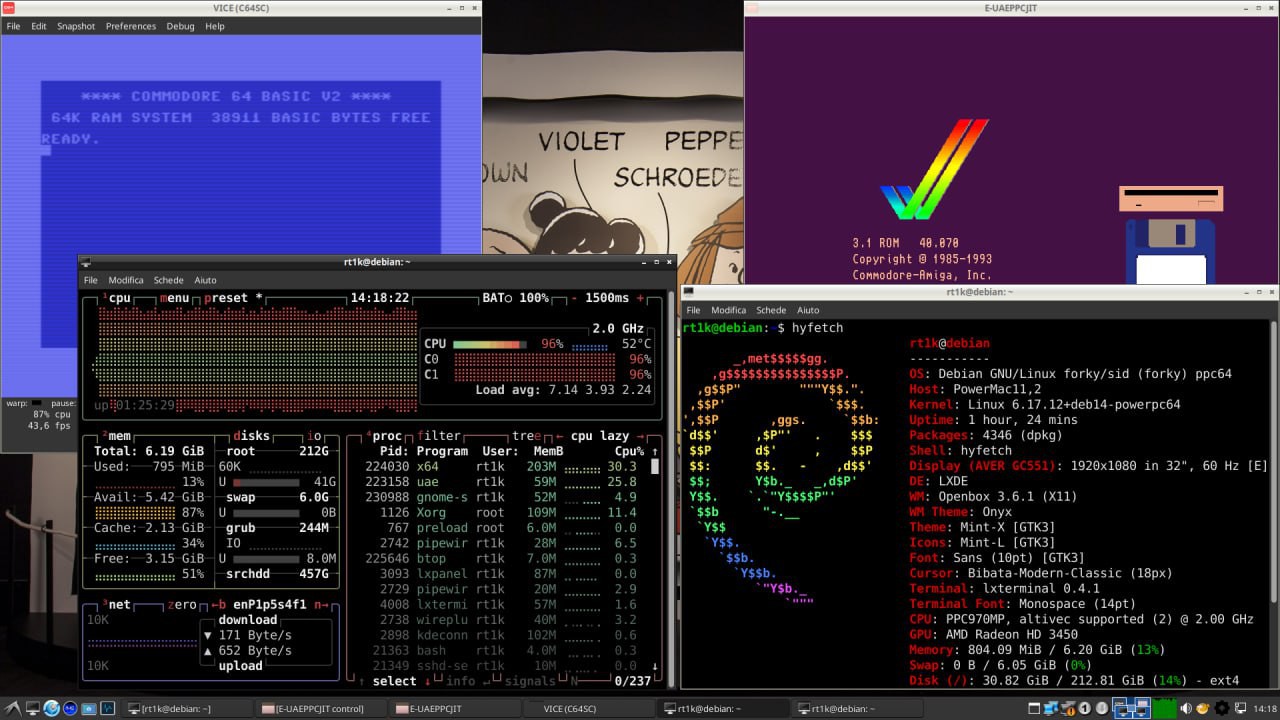

The choice of the PowerPC platform is justified by an interesting technological situation: PowerPC CPUs that are produced today have good computational power with regards to the power consumption, they are well supported by the Linux kernel, and many Linux distribution supports the PowerPC architecture. The biggest challenge is a total lack of visibility, as the biggest information technology firms do not use PowerPC in their mainstream products, resulting in the general public completely ignoring their existence. Just count the number of companies, association and groups dealing with the -now mainstream- ARM platform: there is way too much competition in this field, and surely there is no need for new supporters.

Our community is aimed at advertising the notebook project in order to build a group enough big to be able to actually realize the project.

- Main project website: http://powerpc-notebook.org/

- Side project aimed at designing and building a notebook chassis: http://open-laptop-chassis.powerprogress.org/

- “Power Progress Community”, the association supporting the initiative: http://powerprogress.org/

- Update slides describing the project: https://www.slideshare.net/RobertoInnocenti1/linux-day-2017-italia/RobertoInnocenti1/linux-day-2017-italia

- Latest public presentation of the project (in Italian): https://www.youtube.com/watch?v=Zn13AXbboY8

- Donation campaign, first phase aimed at the design of the electrical schematics of the mainboard: https://fundraising.powerpc-notebook.org/

Forum: http://forum.powerpc-notebook.org/ Questionnaire: http://survey.powerpc-notebook.org/ Wiki http://wiki.powerprogress.org/

Social media: https://twitter.com/powerpcnotebook https://www.facebook.com/powerpcnotebook/ https://www.linkedin.com/groups/7300932

We are building a vast group spread over the 5 continents, a group of creative people having a very heterogeneous background and knowledge and that is willing to collaborate for a common goal: designing and building a notebook following the Open Hardware philosophy. This is a courageous project, some say a little bit crazy, a project that little or nothing has to share with strict market principles followed by mainstream firms.

Having people spread in the world collaborating on a voluntary basis was made possible by a shared vision: everyone can contribute its own knowledge and competence, share views and experience with others to reach the goal of building a notebook perfectly suiting IT enthusiasts that see in the Open Hardware a viable path for innovating. Altogether we learn the pleasure of discovering al technological aspects that are precluded to the general public when buying a ready-made off-the-shelf notebook, and discovering at the same time the pleasure of sharing such experience and pushing for a virtuous behavior that has generosity at its core.

In the community there are people taking care of carefully...

Read more » Roberto Innocenti

Roberto Innocenti

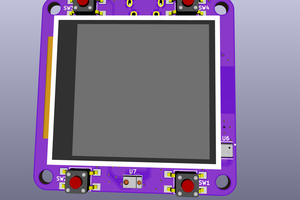

oshpark

oshpark

AVR

AVR

Kuldeep Singh Dhaka

Kuldeep Singh Dhaka

Supplyframe DesignLab

Supplyframe DesignLab

What a great pleasure to read this impressive project details I am also working on a similar type of project you can see here.