-

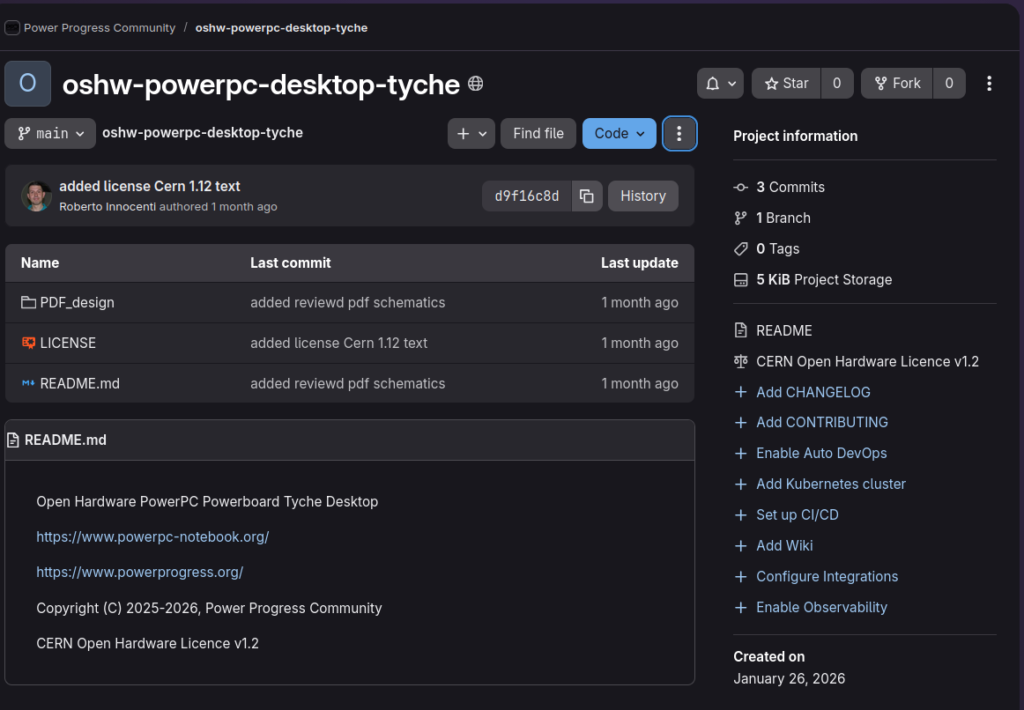

KiCad Schematics sources published, waiting funds for prototypes

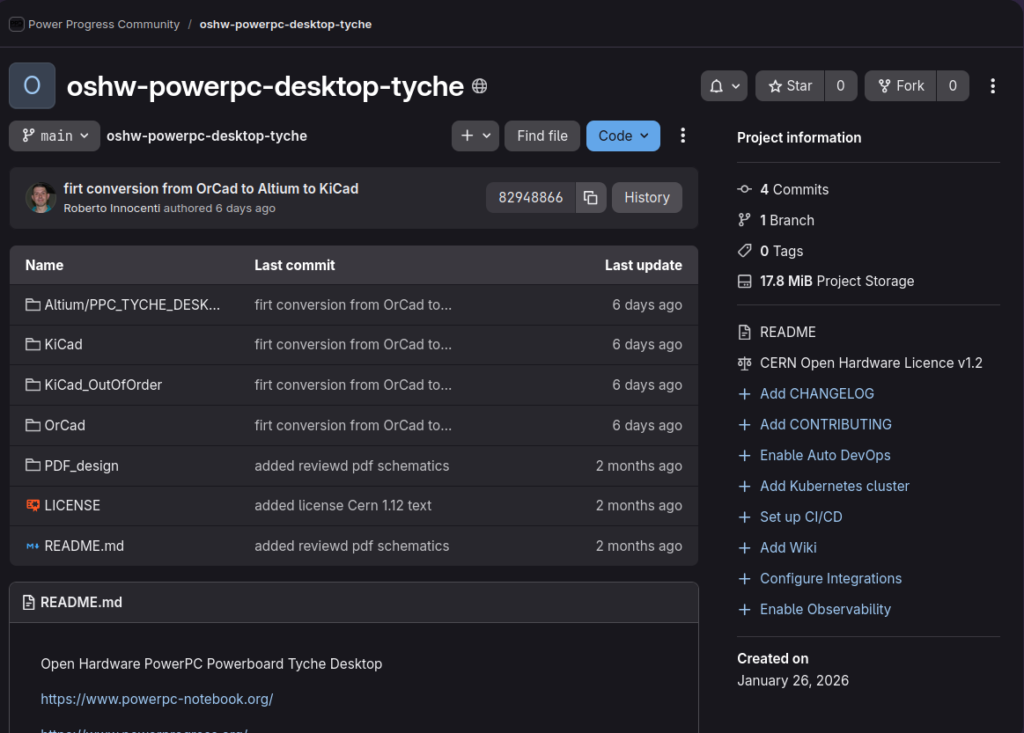

13 hours ago • 0 commentsOn the 24th of April 2026 we published on our GitLab repository https://gitlab.com/power-progress-community/oshw-powerpc-desktop-tyche/-/tree/main/KiCad?ref_type=heads the OrCad schematics source, converted to Altium and then imported into KiCad, thanks to our association members.

![GitLab Powerboard Tyche Kicad sources conversion GitLab Powerboard Tyche Kicad sources conversion]()

As KiCad cannot yet import OrCad schematics, this is a 2-hop OrCad→Altium→KiCad flow.

The KiCad pages are out of order. There are two KiCad directories in this repository: one exactly as imported from Altium (KiCad_outOfOrder), and another where our volunteers attempted to change the page numbers to match the filenames, but they did not reorder in the sheet page listing — they are still in the same random-looking order. We are investigating how to fix this at some point, as the file with “01” in the filename should come first, since it contains the table of contents, in order for everything to line up correctly. Other than the ordering issue, it looks reasonable.

![Kicad source Powerboard Tyche Desktop Kicad source Powerboard Tyche Desktop]()

If you would like to help check the quality of the conversion to KiCad and potentially work to improve it, please contact us.

Schematics Donation Campaign updated its goal and completed — PCB Donation Campaign updated its goal with around €3,500 still needed to reach it

On 6th April 2026, thanks to the funds collected for the Notebook CE certification and due to the temporary halt of Notebook motherboard production, the association used €2,130 from that previous campaign to pay and balance the Desktop Schematics design costs that are €6,250.

A further €8,000 from association funds was used to pay a portion of the PCB costs in advance. The total cost of the PCB design is around €12,500; since €8,000 came from association funds, we have reduced the goal of the PCB donation campaign to €4,500.

PCB Design of Desktop Powerboard Tyche

Starting from the source of the Electronic Schematics design design the PCB means prepare all physical PCB layers lanes and components disposition and connection to go in production with prototypes. Designer have take from NXP Devkit design ( 2023 version) everything is related to boot process and many parts from our Notebook design, except what is not needed for Dekstop version, like the Battery part.As you can see to reach the goal of this campaign we need to receive donations of around €3,100 to settle the balance with ACube for the PCB design before the end of May.

![]()

From March 2026 the PCB design has been completed and is in our hands, we are waiting funds to start prototype production.

To produce the first five prototypes, we need a total of around €9,000. Once we have the cash flow to balance the PCB design and to make this commitment to the manufacturer, we will sign the contract to proceed with production. To avoid further delays, we need significantly more donations.

Join us to Help on Debian PPC64 Big Endian packages

Do you have already installed Debian 13 PPC64 on your G5 or Debian 13 PPC on your G4?

More info how to do it on our forum.

In case you have not PowerPC hardware we can give you access to the Power9 VM we have free at OSU thanks to the support of , so you can test and fix the package inside this VM.

If you want to investigate which are the packages that are compiled successfully on PPC64

powerpc ( 32 bit) https://buildd.debian.org/status/architecture.php?a=powerpc&suite=sid

To verify if a bug is already reported on the Debian bug tracking system

How to report a bug https://www.debian.org/Bugs/Reporting

To fix and build a debian package

‘sbuild’, which is the software used to build Debian packages in a clean environment.

To get it working, all you need to do is create a file called ‘release-name-architecture.tar’ in the ~/.cache/sbuild/ folder, which contains a minimal Debian system.

To create these tar files containing Debian images, is suggested to use another little tool called ‘mmdebstrap’. It’s very similar to its cousin, “debootstrap”, which you may have heard of, but it’s a bit faster.

Finally, if you’re comfortable working with Git, we recommend the tool “dgit”, which essentially allows you to download and build any Debian package in a consistent manner, without having to worry about how the package maintainer themselves works with it.

So, in terms of the commands to use on your machine:

mmdebstrap --variant=buildd unstable ~/.cache/sbuild/unstable-amd64.tar dgit clone mbedtls cd mbedtls dgit sbuild

Contacts us

-

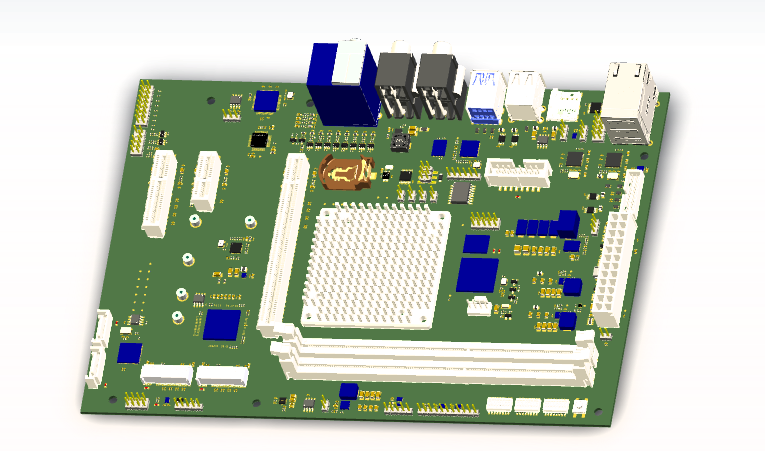

We are ready for prototype production!

03/28/2026 at 18:35 • 0 commentsThe PCB design is finally complete, and we are officially ready for prototype production.

![]()

![]()

However, before taking the big step, we need to balance the PCB design costs:

- 3,050 euros at the end of April;

- 3,050 euros at the end of May;

To produce the first five prototypes, we need a total of around 9,000 euros. Until we have the cash flow to make this commitment with the manufacturer, we will not sign the contract to go into production.

Schematics are already published in pdf format on our gitlab repository

![]()

Why aren’t we publishing the PCB design yet?

We will only be able to publish the open-source design after paying the design costs and only when prototype production is underway. This is for two fundamental reasons:

- Before paying, we do not own the rights to the source files.

- The source files will only be considered final after physically testing the prototypes.

Furthermore, our manufacturer ACube Systems can only afford to produce the Desktop board for the first time if no one else beats them to the market. After all the hard work done to make this dream a reality, it is our duty to protect them.

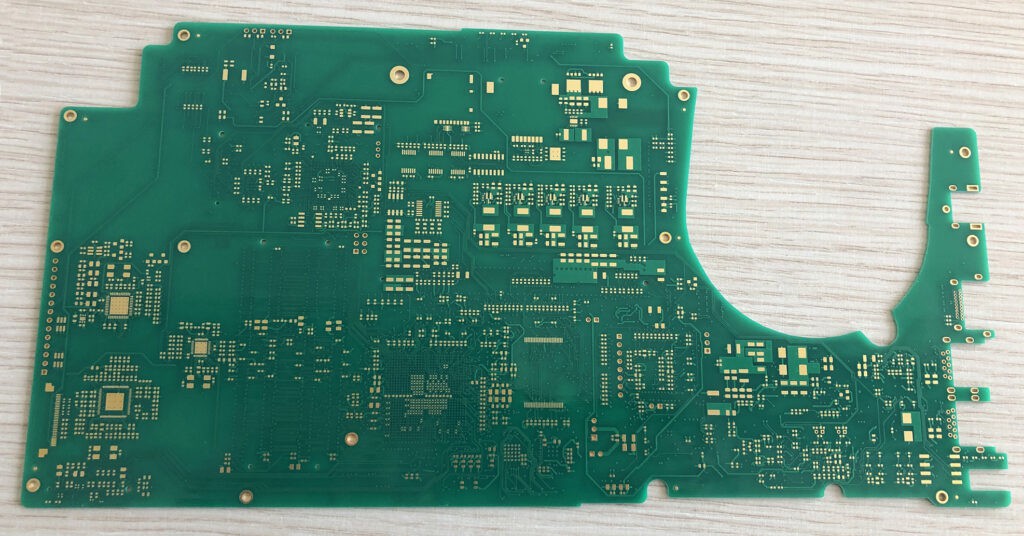

A special campaign: win the historic laptop PCB!

Since the current donation flow is insufficient to cover the design costs and start production, we are exploring new ways to raise funds.

One of the ideas we are considering is a special giveaway: we will raffle off a PCB from our previous prototype (the laptop version) among all donors who contribute from now until we reach the 9,000 euro goal.

![]()

Please note: this is a “dummy” PCB (non-functional), produced solely to verify the physical dimensions of the board. It was never an operational prototype. We hope this piece of our journey’s history can motivate the community to help us cross the finish line!

T-shirts, gadgets, and the “DY Maker” spirit

![]()

We are preparing T-shirts and other gadgets dedicated to the PowerPC Notebook and Desktop projects, also linked to our association DY Maker mindset.

We collaborate with volunteers to create the opportunity to experience hands-on learning, to inspire creativity, critical thinking, and problem-solving by trying to conceive, design, and produce what we need or desire. We encourage this culture from primary schools to University, with no age limit.

Soon we will ask you to vote on different options for T-shirts and gadgets. After that, we will open pre-orders for t-shirts, stickers, and much more!

Our recent events

We have been very active locally:

- March 13 – Bolzano, Italy: We shared our project with electronics students at Free University of Bozen · Bolzano – Faculty of Engineering – Electronics and Information Engineering, just as we did in Milan in May 2025. In agreement with the professors, we discussed possible university theses in collaboration with our association.

- March 14 – Trento, Italy: We were hosted by Hack in Povo in collaboration with LinuxTrent, where we presented the history of our projects.

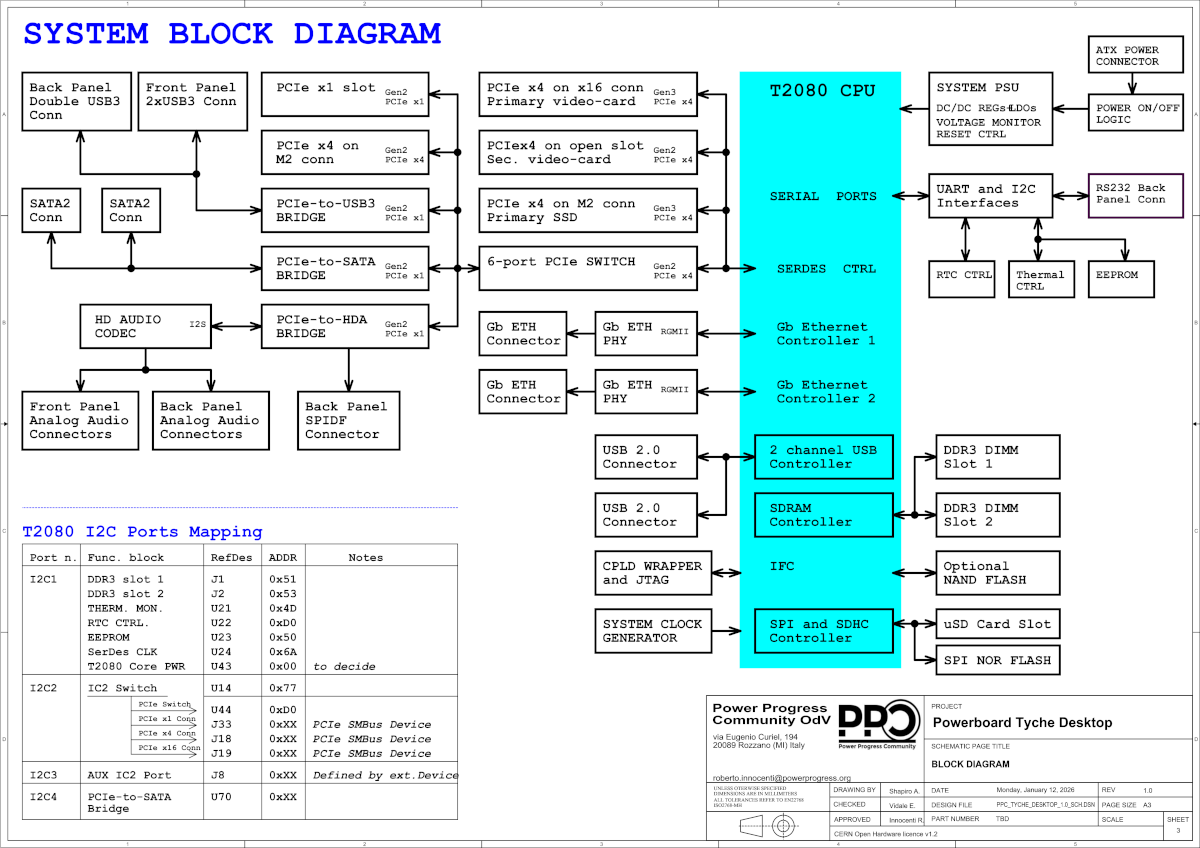

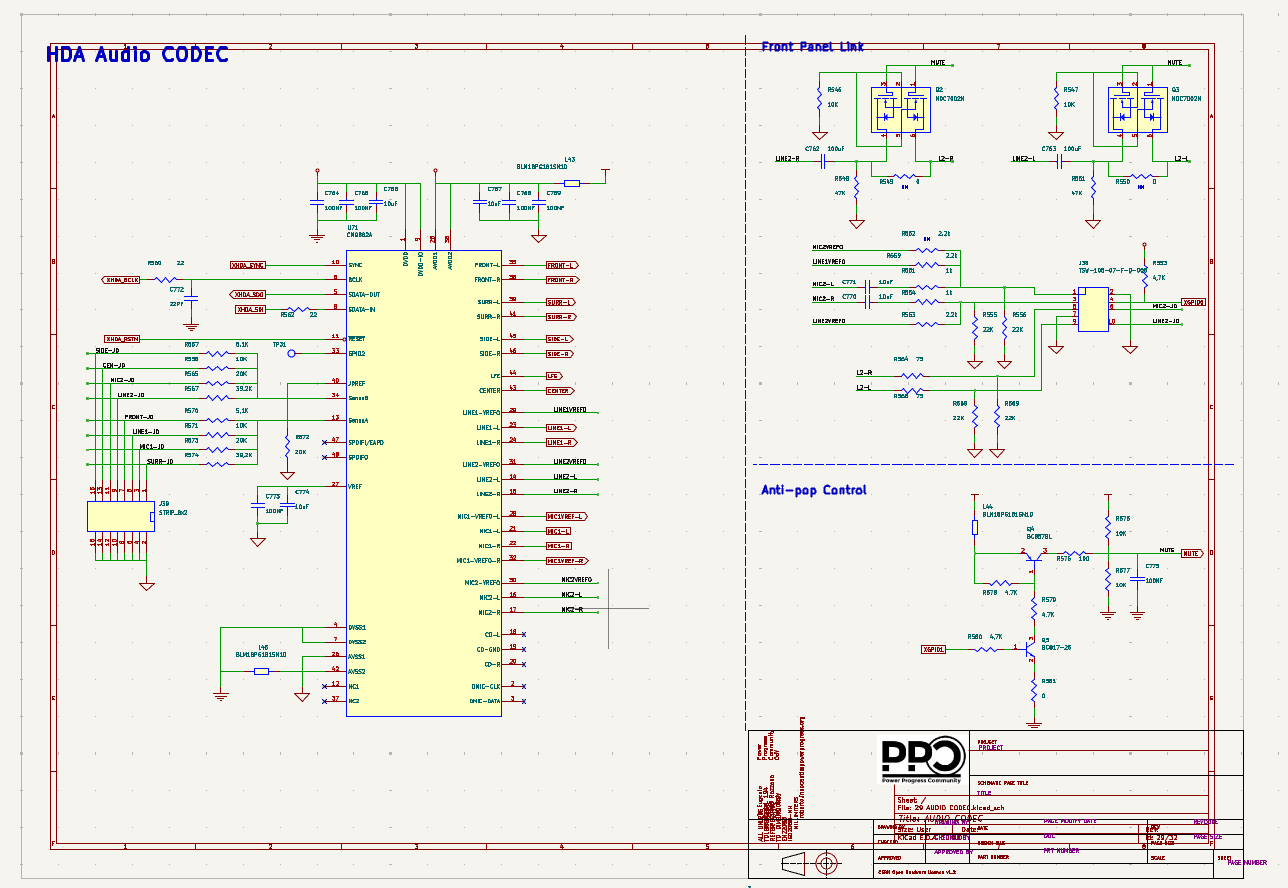

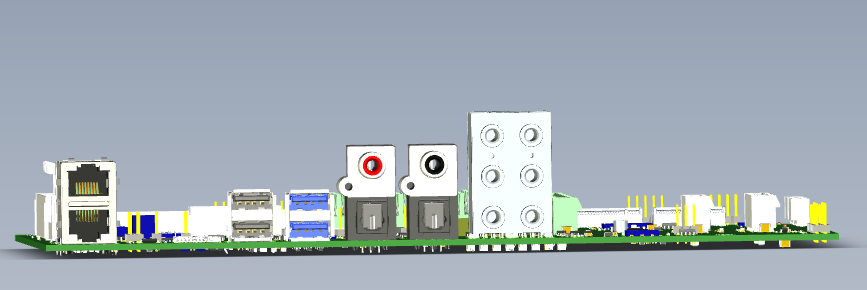

Desktop board specifications

Our Desktop board is a Micro ATX measuring 244 mm in height and 172 mm in width. When it comes to audio, we didn’t hold back: it features optical digital audio inputs and outputs, 6 analog RCA connectors for 7.1 surround sound, and separate ground connections for the analog and digital sections to ensure maximum sound clarity.

![]()

Software and PCB source roadmap

- Stage 1: Soon we will convert the Schematics source files from Cadence to Altium, and then to KiCad. In the meantime, there is a free viewer for Orcad sources at this official Cadence link. We also point out an interesting open project that has started importing Orcad sources directly into KiCad: OpenOrCadParser.

- Stage 2: Thanks to your donations, once we have collected enough funds to balance the design and prototypes, we will merge and import the PCB source files from PADS directly into KiCad. This is now possible thanks to the brand new importers introduced in KiCad 10: learn more on the KiCad blog.

PCB Design of Desktop Powerboard Tyche

Starting from the source of the Electronic Schematics design design the PCB means prepare all physical PCB layers lanes and components disposition and connection to go in production with prototypes. Designer have take from NXP Devkit design ( 2023 version) everything is related to boot process and many parts from our Notebook design, except what is not needed for Dekstop version, like the Battery part.

-

Your name will be printed on our board. If you make the most generous donation by today.

03/03/2026 at 22:10 • 0 commentsWould you like to go down in #openhardware history?

Your name will be printed on our board. If you make the most generous donation by today.

https://www.powerpc-notebook.org/2026/01/schematics-reviewed-and-published/

You can check other donations done on "Powerboard Tyche Desktop Electrical Schematics Design"

https://www.powerpc-notebook.org/list-of-donors/![]() Tyche By lapaowan https://www.deviantart.com/lapaowan/art/Tyche-828692436

Tyche By lapaowan https://www.deviantart.com/lapaowan/art/Tyche-828692436 -

Schematics reviewed and published!

02/04/2026 at 23:55 • 0 commentsWe have known each other for several years now, working together with supporters who have backed us through the long process of creating notebook prototypes. Over the last eight months, we have focused on developing a desktop version largely redesigned to be immediately functional.

As promised, the sources for our desktop board have been reviewed by NXP. They suggested a few changes, which we have implemented. The review process cost us an additional €850, but it was worth it: we have improved our schematics and PCB design just in time for the prototypes.

Great news: NXP confirmed we can publish the schematics with an Open Hardware License! We have already uploaded the PDF version to GitLab. and in our Hackaday.io project file space.

GitLab Repository Powerboard Tyche Desktop Schematics

![]()

However, before publishing the raw source files, we need to convert them from the proprietary OrCAD format to KiCad to ensure everyone can use them. We need collaborators to help us bridge this gap.

If you would like to reserve a production desktop board this summer, we need donations to cover €6,100 for the remaining costs of the PCB design, as well as the expenses associated with prototypes and testing in the coming months. ACube Systems will handle the production because we are a nonprofit organization not allowed to sell physical products.

We are doing what is needed to reach production, despite the obstacles. The difficult part, the uncertainty, is behind us. Now we are missing a very simple ingredient: funds. We need to raise a few thousand euros in a window of 2-3 months. Simple, but not easy.

Join us on this journey!

Donate, tell your friends, and share our project. In order to enjoy the PowerPC motherboard later, we must all work together now by joining the donation campaign in large numbers.

Join us in this great opportunity for hands-on learning, creativity, and problem-solving as we design and produce what we desire.

If you have any suggestions, don’t hesitate to fill out our survey or contact us.

PCB Design of Desktop Powerboard Tyche

Starting from the source of the Electronic Schematics design design the PCB means prepare all physical PCB layers lanes and components disposition and connection to go in production with prototypes. Designer have take from NXP Devkit design ( 2023 version) everything is related to boot process and many parts from our Notebook design, except what is not needed for Dekstop version, like the Battery part.

-

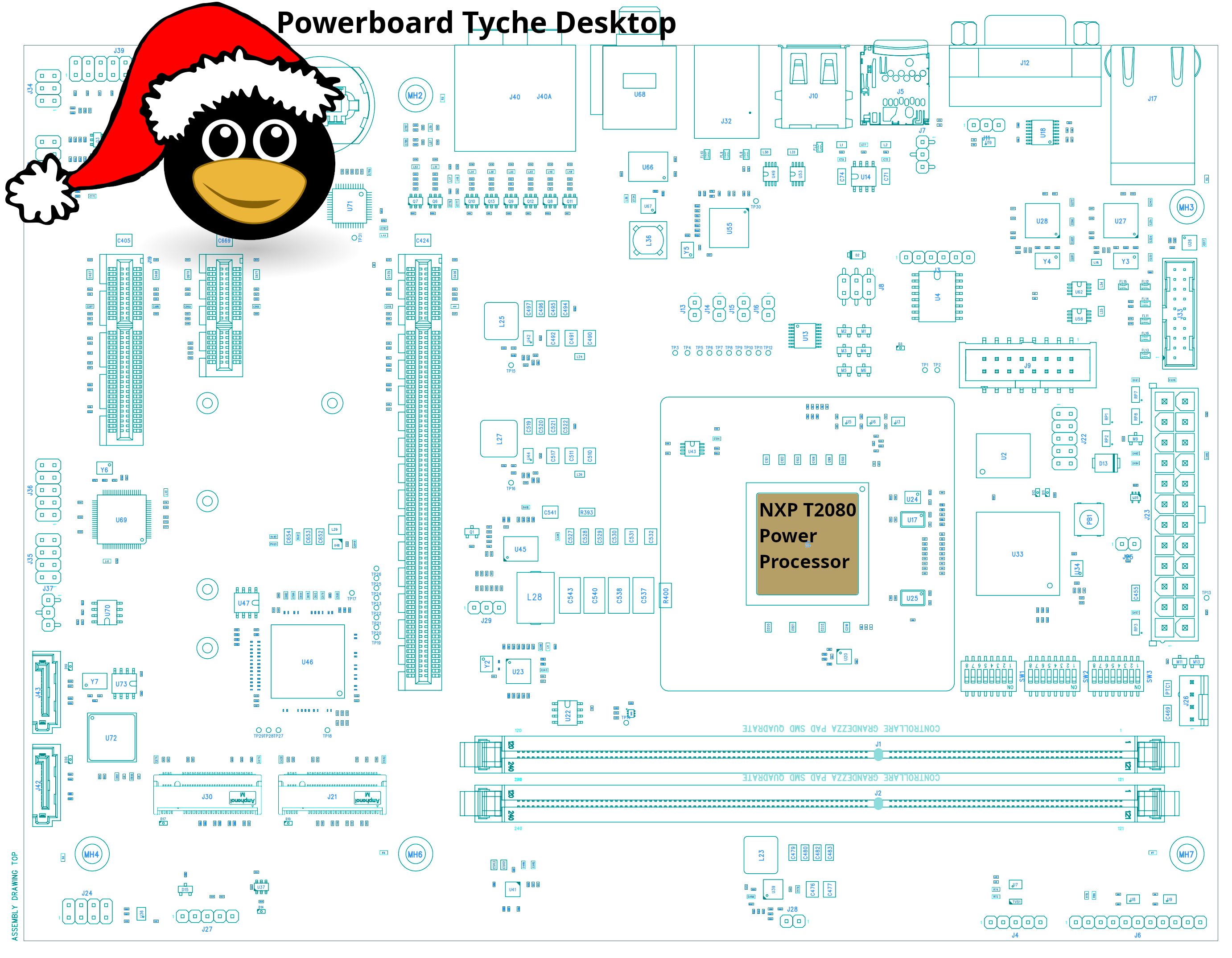

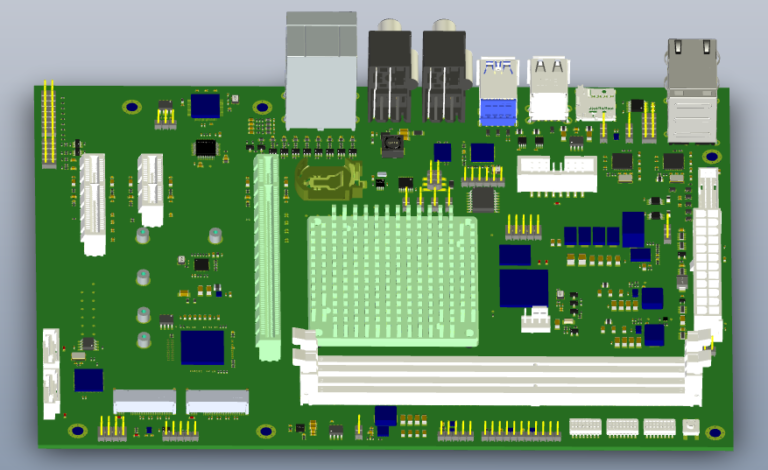

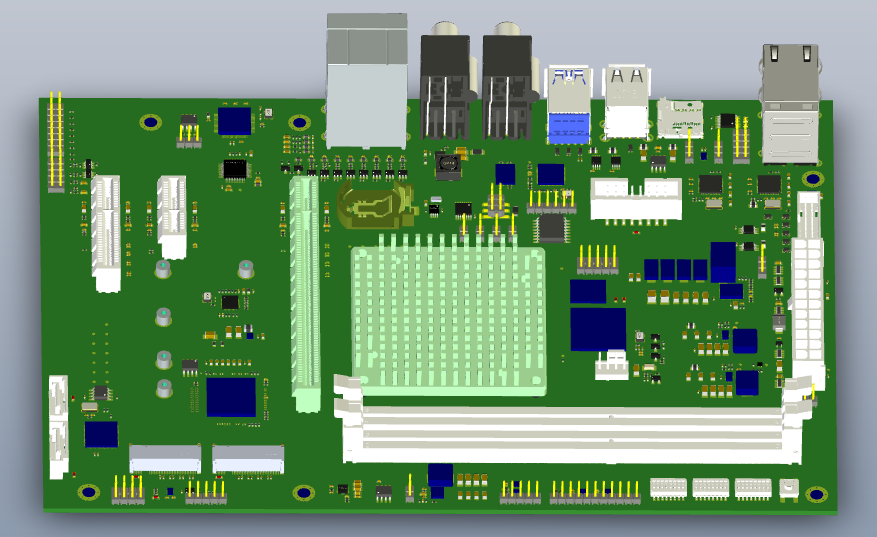

First PCB Desktop Layout!

12/25/2025 at 21:36 • 0 comments![]()

Today we publish here ( above) an export from PCB design of our PowerPC Desktop motherboard (based on processor NXP T2080) , you can see the motherboard top view with components and connectors, it reflect the progress on pcb design, that is going fast. Before the end of January will be completed !! In January should be defined the costs and timing for the production of the prototypes.

- The dispositions of components on the board are not final.

- As requested by our association members there are 4 holes 30-42-60-80 for the left M.2 connector.

- The two Ethernet are one on top of the other.

- There is even a digital audio output.

- There are 3 PCIE connectors: 16x, 4x Open ( with space for 8x and 16x), 1x

In the mean time that is in progress the donation campaign for the schematics design we open now the donation campaign for the PCB design.

Payments we should do next days:

Schematics Design

Before 31 December we should balance the payment for the schematics design plus 850 euro needed to fill the review questionnaire asked by NXP, So we have summed the 850 euro to the running campaign for the Schematics.

PCB Design

We need to pay at beginning of January the 50% of the cost for PCB design that is around 6100 euro, so we have created the PCB design campaign that is 12500 euro ( 10000+VAT+paypal/stripe fees) .

We thanks donors and collaborators that permit us to finance everything realized until now.

We are going faster as promised, to realize a working Open Hardware PowerPC motherboard in few months , that increase rhythms of design and production, costs and ask us to increase even the rhythm of donations…

Donation is a form of collaboration so apart your one shot or recurrent donation that are welcome, we even ask you to spread all over you can our project so more potential collaborators could join our project.

On 12th December NXP confirm us that the review of our source schematics was submitted, they don’t give us any estimation on how much time they take to do the revision and to give us the permission to publish as Open Hardware the schematics source. After we will have the agreement from NXP we will publish the sources as we do usually, as we have done for our Powerboard Tyche Notebook motherboard sources.

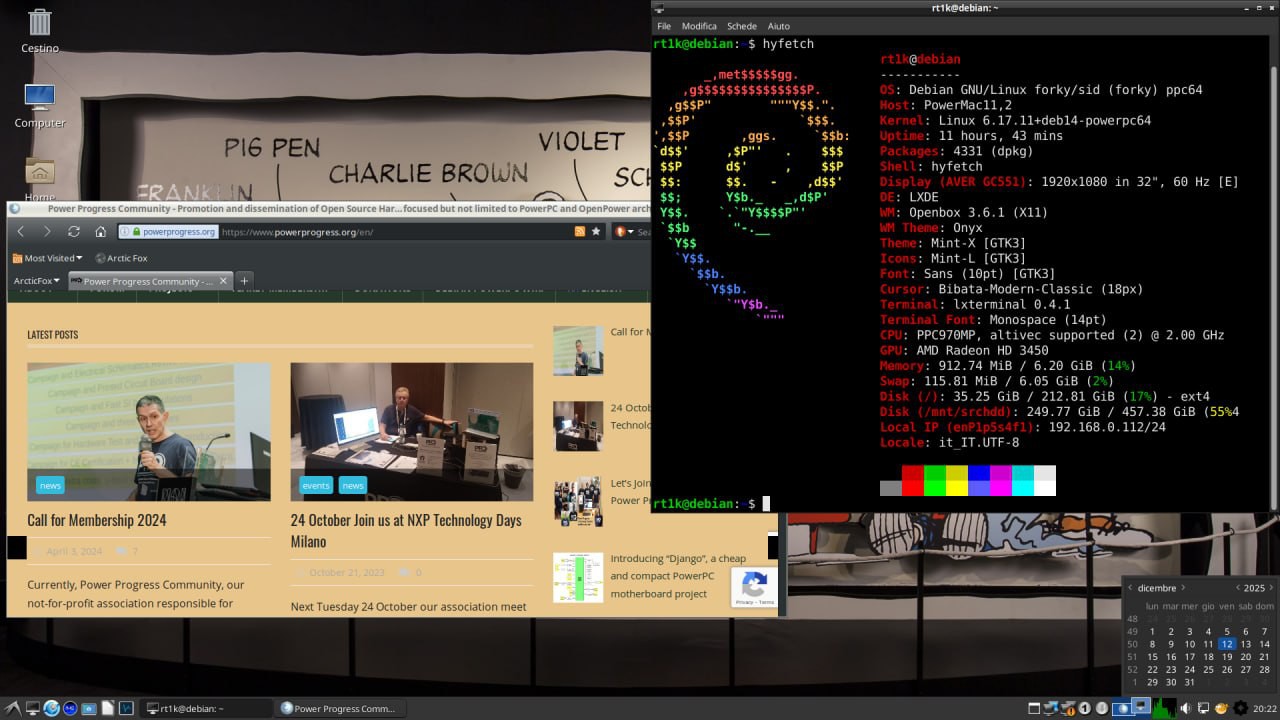

Debian 13 installer for PPC64 and powerpc (32bit)

We are very happy that Debian ports team have published a working Debian 13 installer for PPC64 and powerpc so we have tested on PowerBook G4 and IMac G5. Please join us if you want to help on test Debian PPC64 package or if you want to test even Mint PPC

![]()

![]()

We have published on our forum how to install it.

-

PCB Design Costs and Timing

12/22/2025 at 22:34 • 0 commentsPCB Design Costs and Timing

In our last post we have announced that we were reviewing the schematics of our Powerboard Tyche Desktop; this careful process involved ACube Systems and one hardware engineer from our team from mid-October to mid-November. So on 10th November we sent our schematics to the PCB design company for quote, that resulted to be around 12500 euros (VAT included). In the next ten days ACube Systems, our actual designer and the PCB design Company will meet to refine every detail like the ATX board dimensions, PCB layers, that should be ten layers.

Schematics Sources Publication

Our hardware designer completed to fill the NXP questionnaire to ease NXP review of Powerboard Tyche Desktop source, so we have forwarded to NXP everything they requested us to allow publishing the parts of our board derived from NXP T2080 RDB Revision F. We asked NXP how much time the review will take, but we don’t have an answer so far. Stay tuned!

![]()

After NXP green light we will publish the Powerboard Tyche Desktop schematics on GitLab as usual. Since designer and NXP use Cadence ORCAD, we will convert our motherboard sources to Altium and then KiCad.

Steps before Production

We expect that the PCB design will be completed beginning of February 2026, thus we strongly need donations to pay for the PCB design.

After that, prototypes production could be set up, so signing the manufacturing agreement depends on your donations and on your activity to spread the word about our project and donation campaigns to the world.

If donations keep steady, we then expect to have prototypes in a couple of months (April 2026) so that we can afterward perform hardware tests. If everything goes according to the plan, in June 2026 the hardware test will be successfully completed and we will see booting with Debian PowerPC64 and other GNU/Linux distribution as we are doing with our T2080RDB devkit converted in Desktop from 2016.

![]()

Powerboard Tyche Desktop and Notebook

Therefore, we expect ACube System to start boards pre-orders in July 2026 and, in the mean time, we will go back to work on the next milestone for the notebook version: please join our notebook work group if you want!

Join the Software Workgroup for PPC64BE

We invite anyone to support GNU/Linux PowerPC distribution like Debian to improve support on PPC64 big endian architecture.

Spread the Word

You can take part to the project success by talking about it in the fediverse or in any kind of forum, blog, website, etc… you think it would be relevant on!

Linux Day Milano and SFSCON

As usual our volunteers were ambassadors at Free Software events as we have done in the past on Freeplanet event, FOSDEM 2020, Open Power Summit Open Source Summit, etc…. : this fall we participated at Linux Day Milano on October 25th and SFSCON on 6th-7th November, and as usual we got to involve some more people in our activities!

![]()

Sfscon – Bolzano – 7th November 2025 – speech Open Hardware PowerPC Powerboard Tyche Desktop

We want to underline the meaning of our open hardware projects

![]()

We have vehicles, appliances, phones that cannot be fixed, because their manuals are not available, they are locked behind DRM, or spare parts are either unavailable or prohibitively expensive. Even more worrisomely, perfectly fine connected devices become useless bricks just because the original manufacturer do not find them profitable anymore. This creates unbelievable amounts of unnecessary waste.

Nowadays, we see laptops with soldered RAM and GPU, absolutely closed design and mostly running closed OSs. Our design that started in 2017 has 2 RAM slots and a separated MXM video card.

![]()

Powerboard Tyche Notebook – MXM video card slot and 2 RAM slot Our notebook motherboard design fits in an already produced notebook shell and uses a PowerPC processor that can keep up with modern mid-end boards, even though its production started in 2012: a true testament of a good design.

In 2006 we have seen that market of notebook and desktop switched completely to x86 (Apple had used PowerPC CPUs until then), but not because of a technical reason. Some of us were looking to a new PowerPC CPU, and since 2012 Freescale (now NXP) produced the second, more power efficient generation of their PowerPC processors, the QoriQ T-Series, we thought that the T2080 could be used in a notebook, being a good tradeoff between the T10xx lower power line and the T4xxx higher performance line. We then started this project website. It was only a faint idea inside someone’s head, then it was shared with some others on this website and then became something concrete, with hundreds of donors, a design made, prototypes produced and tested… In 2025 we haven’t got yet a production-ready Open Hardware PowerPC notebook, but we have completed the second schematics design and thanks to YOU TRULY we will make production-ready prototypes real.

Our modern societies need to control and manage the technicalities in order to run: electronics and software is nowadays pervasive to every bit of our life, in our homes, in our workplaces, in our vehicles, in critical infrastructures like roads, bridges (yes!), railways, ports, utilities, healthcare…

![]()

Image by Tomasz Mikołajczyk from Pixabay That’s why it is so important that every country, every community needs to have people capable of designing, producing and validating electronics and software powering every building, vehicle, hospital, medical devices, school, university, aqueduct, sewage treatment, power plant, every piece of the infrastructure we depend on for our lives.

And that’s why is so important that we complete an Open Hardware Desktop designed around free software, involving students, and young, and previously young people, to be able to build the bricks of our society.

Thanks to your support, this Open Hardware Desktop first, and then the Notebook, will demonstrate in practice that a group of common people could create computers that respect our freedom.

-

Schematics of the Powerboard Tyche Desktop version Completed! Soon starting the PCB design

10/30/2025 at 23:17 • 0 comments

We now have the complete electronic source design for our new desktop design in our hands!This week, ACube Systems and some volunteers from our association will review the design. We expect the manufacturer to start setting up the PCB layout for the new Powerboard Tyche Desktop on October 20th. This is part of our strategy to focus on creating a stable, functional desktop version of the core computing platform by the end of 2025.

The PCB design phase (Phase 2) will begin shortly after the schematics and Bill of Materials (BOM) are sent to the manufacturer. We anticipate that this step will allow the manufacturer to provide us with an estimate of the cost and timeline for the PCB layout design. This cost and timing estimate will then be shared with the community “just in time.”

Technical Components and NXP Review

We have verified that the availability of SATA2/3 controllers is poor, and the chip Lattice Silicon Image SiI3132 chip that we selected is no exception. We decided to include it in our desktop board to ensure backward compatibility with SATA devices, such as DVD and HDD.

We do not use the on-chip T2080 SATA2 controller because we prefer to use the T2080’s three x4 PCIe Gen3 configuration to optimize the speed of video cards and storage controllers. This configuration cannot coexist with the on-chip SATA2. In any case, the best performance is possible thanks to our M2 motherboard interfaces.

In our board design, we have an SPI connection for an external LCD, which can be used as a secondary screen or for debugging and diagnostics. It is also useful when setting up u-boot and when no video card is connected to the board.

Our board design includes GPIO connectors that can be used to connect other devices that don’t use USB, SPI, or PCIe buses.

Our desktop design is derived from our old notebook design and the original NXP T2080 RDB (Release F) design. We are integrating many components specified in the reference board, including critical monitoring hardware.

This includes the OnSemi ADT7481ARMZ thermal monitor, which has been upgraded to the OnSemi NCT72. The ADT7481 is used as the thermal monitor or temperature sensor on the original NXP T2080 reference design board. On that board, the ADT7481 (designated U34) is usually connected via the I2C_1 bus with the address 0x40. The T2080 processor itself contains a temperature diode designed to be used with system temperature monitoring devices, such as the Analog Devices ADT7461A. This similar part is mentioned in the documentation for the T1042 chip, which highlights the standard use of such monitoring.

Designers have changed other components from the original T2080 RDB design and our notebook design due to the availability of new compatible models, such as the N25Q512A13 FLASH SPI, which is substituted for the EvKit Micron MT25QL512A due to its limited availability.

Due to the changes in components, we will need to modify the VHDL code of the CPLD chip when we have the prototypes in our hands. Therefore, we must take into account the additional cost of this task.

To ensure full compliance and open-source publication readiness,

- The designer will fill out the NXP review questionnaire [draft post 2025-10-12] simultaneously.

- The questionnaire and the Cadence schematic source will then be sent to NXP.

- The main goal is to receive a full or partial agreement to publish the parts of our design derived from the original NXP T2080 RDB (Release F) as open hardware

We anticipate a robust boot-up because the components and firmware are similar to those of the stable T2080 RDB. The specific CPLD is programmed using the original CPLD source code of the T2080 RDB. Once NXP grants the necessary agreement, we plan to publish the source schematics and evaluate the use of a recent CERN Open Hardware License version.

Upcoming Project Phases

The next anticipated milestones, pending finalization of cost estimation:

- Phase 2: PCB design. (tentatively scheduled two months after the completion of the schematics).

- Phase 3: Prototype production (tentatively scheduled one month after PCB design).

- Phase 4: Prototype testing (tentatively scheduled one month after prototype production).

We continue to rely on the community’s support. Recurring donations are dedicated to the campaign aimed at recovering costs already incurred for notebook testing and CPLD firmware fixin

We are searching volunteers to test Debian PPC64 and fix packages

Finally, we need more volunteers to support the necessary software efforts, including Debian PPC64 testing, as we cannot ask for additional donations for this purpose.

Below is an updated list of specs for the desktop board being designed.

Form Facttor: Micro ATX

CPU: NXP T2080, e6500 64-bit Power Architecture with Altivec technology

4 x e6500 dual-threaded cores, low-latency backside 2MB L2 cache, 16GFLOPS x core

RAM: 2 x DDR3 Slots

VIDEO

PCIE3 x16 VIDEO Card 1

PCIE2 x16 VIDEO Card 2

AUDIO: C-Media 8828 sound chip, audio IN and audio OUT jacks (3x2)

USB: 2 USB 3.0 ports

2 USB 2.0 ports

2 USB 3.0 ports internal for FRONT

STORAGE:

2 NVM Express (NVMe)

2 x SATA2

1 x SDHC card reader

NETWORK:

2 x Gigabit ethernet RJ-45 connecto -

Desktop Electrical Schematics Ready! in August.25

07/16/2025 at 17:24 • 0 commentsWe are very happy to inform you that the Schematics Design of our new Powerboard Tyche Desktop is running fast thanks to the new Designer and to the NXP Devkit source design plus our Powerboard Tyche Notebook design. Designer took from the NXP Devkit design ( 2023 version) everything is related to the boot process and many parts from our Notebook design, except what is not needed for the Desktop version, like the Battery part.

You can check all the details regarding what we took from Devkit design and what we took from our Powerboard Tyche Notebook design.

![]()

At the end of July, we will provide the schematic design and the BOM to the factory, which will then begin the PCB design based on the schematics. Therefore, by the beginning of August (before the factory’s holiday closure), we will know the cost for the PCB design and prototype production. New donation campaigns will then start for PCB design and prototype production.

Today, July 14th, 2025, we’ve officially launched the donation campaign for the schematics. Before the end of July, we’ll make the down payment for the schematics design. We already have funds collected from the previous donation campaign for the CE certification (of the Powerboard Tyche Notebook), so we can advance money from that fund. However, it’s crucial to boost this new campaign and encourage everyone to donate so we can use fresh funds specifically for the schematics design.

SPECS

- Form Facttor: Micro ATX

- CPU: NXP T2080, e6500 64-bit Power Architecture with Altivec technology

- 4 x e6500 dual-threaded cores, low-latency backside 2MB L2 cache, 16GFLOPS x core

- RAM: 2 x DDR3 Slots

- VIDEO

- PCIE3 x16 VIDEO Card 1

- PCIE2 x4 VIDEO Card 2

- AUDIO: C-Media 8828 sound chip, audio IN and audio OUT jacks

- USB: 3.0 and 2.0 ports

- STORAGE:

- NVM Express (NVMe)

- 2 x SATA2

- 1 x SDHC card reader

- NETWORK:

- 2 x Gigabit ethernet RJ-45 connecto

Yes, it’s possible to reach the goal to have a working Powerboard Tyche Desktop before the end of 2025, but is needed an extraordinary effort from donors because we depend on donations to cover all the steps that are coming : Schematics Design, PCB Design, Prototype Production and Tests.

Starting from today (July 14th 2025) you can make your donation, thanks!

Milestones

Phase 1: Actual Campaign Schematics Design : goal 30.07.2025

Phase 2: PCB Design : goal 30.09.2025 [depending on donations collected]

Phase 3: Prototypes Production: goal 30.10.2025 [depending on donations collected]

Phase 4: Prototypes Tests. : goal 30.11.2025 [depending on donations collected]

The milestone phases depend from your donation. Thanks!

We remain absolutely committed to making an Open-Hardware Notebook-based PowerPC machine a reality.

As we have already published on our past post we have changed the tactic, focusing on a desktop board first allows us to concentrate on getting the core computing platform stable and functional, tackling the complexities of a laptop form factor (like power management, screen integration, etc.) in a later stage if needed. This is a pragmatic step to ensure we achieve a tangible outcome by our 2025 target. What’s more the Powerboard Tyche Desktop version will be more cheaper than the Notebook version!

We value the experience of making our Open Hardware Powerboard Tyche based on PowerPC from scratch; this is possible thanks to the support of all donors and supporters, and the time and creativity of the activists who have been involved in this project over the years.

We ask you to share every-ware this call for support a strong flow of donations to cross the finish line of all donation campaigns to arrive by 2025 with produced, tested and functioning prototypes!

-

Strategic Change: By 2025, let’s do whatever It Takes to achieve at Least a desktop version!

05/21/2025 at 21:34 • 0 commentsHello everyone, we know it’s been quite some time since our last update on November 21, 2024.

We really appreciate your patience! Despite the silence on our end, we’ve seen that our incredible community – both old friends and new supporters – have continued to donate continuously. An infinite thanks to all of you, our amazing current, past, and future donors! Your unwavering support truly fuels our efforts and keeps the dream alive.

![]()

Image by Tú Anh from Pixabay Short story

As we shared in our last post, the work with the previous designer hit a significant hurdle: we just couldn’t get the board to reach the crucial boot stage.

This led us on a search for a new designer, someone with specific skills and experience with PowerPC architecture. We were really pleased to find a talented new designer who was available from the beginning of 2025, who can even rely on an additional person who is an expert in firmware programming. Following our plan, we used January and February to make the big move, getting all the equipment transferred over to this new designer’s team.

We held off on publishing updates because, honestly, we were waiting for that breakthrough moment – the good news we could finally share with all of you. As things were showing quite promising (e.g. improved CPU signals outputs), we had high hopes that this new collaboration would quickly move us past the booting issues. In parallel, we also tried improving U-Boot and led an additional T2080RDB, the development board that was kindly provided by NXP, to one of our collaborators, but due to personal health problems, he can no longer contribute to the project.

![]()

Our work with the new designer has been focused on rigorous testing. On April 9th, we saw that the board’s behavior was frustratingly similar to the devkit – it still wasn’t booting. This prompted a dedicated session on April 14th for one last intensive attempt to find the root cause. As part of this deep dive, we de-soldered the Marvell chip, which is the SATA3 controller.

![]()

Removing this component was actually something we had already planned to do for the upcoming prototype version as we streamline the design. To help isolate the issue even further, we also de-soldered the Pericom chip.

The overall outcome? Despite taking these significant steps, the board still did not boot. It exhibited exactly the same behavior. We were, frankly, quite upset and left without words.

It’s incredibly challenging when you put in the effort, try to simplify things, and the core problem persists. So far, we have spent around 6000 Euros with the newly hired hardware designer, and even if things have improved, showing the expected NXP documented behaviors of the NXP reference development board, after two years with the prototype motherboards in our hands, we still are not able to boot it.

So what’s next?

This difficult moment, however, has reinforced our resolve and led to a strategic adjustment, as the title suggests. We remain absolutely committed to making an Open-Hardware Notebook-based PowerPC machine a reality.

By the end of 2025, we are determined to do whatever it takes to have at least a stripped-down functional desktop version of our Powerboard Tyche up and running.

We change tactics

Focusing on a desktop board first allows us to concentrate on getting the core computing platform stable and functional, tackling the complexities of a laptop form factor (like power management, screen integration, etc.) in a later stage if needed. We even plan to revert to the NXP original CPLD used in their development board, not the version we previously selected for the notebook prototypes. This is a pragmatic step to ensure we achieve a tangible outcome by our 2025 target.

The path forward still has its challenges. We need to understand precisely why the notebook prototype board isn’t booting and what electronic redesign might be required, and for this, we are in contact with experts directly at NXP. Once we reached the point of a fully working desktop version, we will still have to design the heat pipes, work on the chassis and most probably adjusting the board mechanical design, and finally, test the MXM video card, but for this we hope that the desktop version will provide a suitable testing bed.

With the expertise of our new designer and the continued incredible support from our community, we are pushing ahead with the hope of providing a fertile environment supporting the growth of the PowerPC as a viable alternative architecture. In this respect, we extend our sincere congratulations to Dave ‘Skateman’ Koelman and Harald ‘Geennaam’ Kanning for successfully bringing their PowerPC NXP T1042/T2081 CPU-based micro-ATX desktop board, ‘Mirari’, to a working state.

Open Hardware, your time, your commitment and spreading hardware knowledge is what matters most

Let’s go all the way in realizing our Open Hardware PowerPC board from the bottom up, together as hobbyists, enthusiasts, and volunteers; it makes sense for us to have designed it as a community effort to spread hardware knowledge. We value the experience of making our Open Hardware Powerboard Tyche based on PowerPC from scratch; this is possible thanks to the support of all donors and supporters, and the time and creativity of the activists who have been involved in this project over the years.

For us, it is of fundamental importance that our board is Open Hardware ,( we will certificate as Open Hardware with OSWHA when it will be completely functional) and the prototypes are realized thanks to your support and donations. Designing a notebook motherboard is a challenging objective, and while we like challenging goals, we knew from the start that experimenting at this level of complexity would not always go as initially planned. But we persist; we must finish to reward all the effort we have made.

Be an Association Member to improve ourself

To enhance our collective knowledge, the best way is to join the association NOW (link to join our association). By becoming a member, you can participate in the next meeting, which will be held before May 9th. In these meetings, we delve deeper into the next steps. Association members have a voice in the decision-making process and in solving complex situations together. The more members we have, the stronger we are and the wiser the decisions we can make.

You could be the protagonist of the crucial 2025 milestones

Thank you again for being with us on this journey, as we work towards making our Open Hardware Powerboard Tyche based on PowerPC a reality.

Your support is invaluable, whether through generous donations, contributing your skills as volunteers, or helping us spread the word. This collective effort allows us to continue making progress. We are committed to keeping you informed with the utmost transparency as we strive towards the crucial 2025 milestones. Stay tuned for more updates!

The Long Story

Until November 2024 : The problem was precisely the different behaviour of the two boards; on the motherboard I only managed to run a little test program from SRAM and that writes cyclically to serial, but the output was with unrecognisable characters, because the baud-rate was wrong (while on the devkit the little program runs perfectly), so I think the problem is precisely in the management of the various signals of the CPLD that do not respect what is written in the datasheet of the CPU

History of the activities carried out by the new designer’s team

You can see here the report produced by the new hardware designer team.

The Long Story

Until November 2024 : The problem was precisely the different behaviour of the two boards; on the motherboard I only managed to run a little test program from SRAM and that writes cyclically to serial, but the output was with unrecognisable characters, because the baud-rate was wrong (while on the devkit the little program runs perfectly), so I think the problem is precisely in the management of the various signals of the CPLD that do not respect what is written in the datasheet of the CPU

History of the activities carried out by the new designer’s team

You can see here the report produced by the new hardware designer team.

Acube Portable MB Technical Report EN – Rev 1.0 – NRDownload

They managed to collect some sequences on our prototype, then the complete screen print of the evk was found to solder the threads in the right places.

They managed to get a mirror-image behaviour between the two systems (devkit and our prototype) as little as possible: route SYSCLK to CLK_OUT via uSD (via pbi)

![]()

![]()

Platform clock is 400MHz (SYSCLK * 6 from hardcoded rcw)

Also rcw is read fine from sd (or rather, the pll configuration works, I expect it to pull up all 512 bits correctly)

Performance of reset signals between the two systems,

PORESET_B (channel 1 yellow), under OVdd = 1.8V, is driven by 3.3V

![]()

HRESET is open-drain while PORESET_B is still push-pull

only HRESET is open-drain, PORESET was also put in open-drain, to see if anything changes

![]()

Other inconsistency… JTAG_TRST_N shoots 3v3 on a 1v8 port

![]()

Powerboard Tyche ![]()

devkit T2080RDB ![]()

Zoom Reset RDB Devkit The output type of PORESET has been fixed but nothing has changed.. In the traces above you can see a clear difference between channel 1 (PORESET) and channel 2 (HRESET). The RDB does a much more limited reset sequence (see zoom) and waits about 400ms before raising HRESET, while our prototype, in addition to the more relaxed toggle sequence, only waits ~150ms before raising HRESET. A quick test was made by increasing the time between PORESET and HRESET, but nothing changed.

The hw modification (HRESET and PORESET in open-drain) did not bring the expected benefits, there are still 3 resistors (R375, R377, R379) that should not be mounted, since the documentation clearly states that these pins (PROG_MTR, PROG_SFP and FA_VL) must be grounded (as on the devkit) there was a small increase in current consumption from 12V after this modification now pulls just over 1A from 12V

A few doubts remained, one is as follows: why is it that if the CPU is running at the right frequency, the output on the serial port is with an incorrect baud rate much lower than the set one? what could this depend on?

The frequencies fed to the various plls and peripherals are controlled by the RCWs. of the two hardcoded RCWs, only 0b01001110x is good for us (partially) because it provides a SYS_REFCLK of 66.7MHz. Partially because it predicts a DDR_REFCLK of 66.7MHz, while the prototype has 133MHz. I don’t think it’s a problem in this case though. when you connect with codewarrior there is a possibility to change the rcw.

Removing the resistors that didn’t need to be fitted didn’t change anything.

Tests done in the past with the fw in sdram was done both on our prototype and on T2080RDB

![]()

This was the trace on our prototype serial output, as you can see the frequency was not 115200 baud

Summary as of 8/4/2025

- We have confirmation that at least RCW and PBI are read and applied by the PBL

- Several errors were found and fixed in the assembly plan

The changes on CPLD are divided into 2:

- Fix of PORESET drive type (push-pull -> open-drain)

- Alignment with NXP schematic For the second point, there were no improvements, so not necessarily useful

u-boot developments there are none, since it does not start yet, which is why the debugger attachment fails in our opinion

14/04/2025 Sata3 and Pericom desoldering activity

![]()

setup for testing Board preparation ![]()

our prototype ready to enter the steam oven ![]()

our board during vaporization process ![]()

our prototype during cooling ![]()

![]()

![]() Donation Campaign

Donation Campaign -

Major improvements for Powerboard Tyche despite adversity, but there is still work to be done

11/28/2024 at 13:59 • 0 comments![]()

Photo by mohamed_hassan from PxHere The hardware designer who created our Powerboard Tyche worked between April and July on one of the three prototypes, focusing on fixing the board firmware. These fixes required a series of checks to determine if any additional adjustments were needed for the board itself, and a complete analysis of electronic signals was performed. This analysis was provided later in September. The same fixes were applied to the second prototype (we have three prototypes).

u-boot 2018.11 enabled AMD video cards

Additionally, Max Tretene from ACube Systems was hard at work on our NXP T2080-based DevKit and completed a newer version of U-Boot in May, which finally enabled graphical output on AMD Radeon video cards during booting. You can find the updated source code on our GitLab. Below you can see the new U-Boot in action booting up the NXP T2080-based DevKit.

![]()

![]()

Below is a photo showing the Powerboard Tyche during an electronic test session conducted last August.

![]()

In August, the hardware designer sent back two prototypes to our firmware engineer. ACube Systems purchased an oscilloscope to continue analyzing signals on the prototypes, since the oscilloscope previously used by the firmware engineer was on loan.

In September, signal analysis using the oscilloscopes began, comparing the NXP T2080-based DevKit and our Powerboard Tyche to identify differences. Many differences were found in the power-up sequences, so we asked the hardware designer to fix the CPLD program responsible for governing the signals.

Below is a picture of the expected power-up signals as explained in the T2080 Manual.

![]()

Below is picture showing the signals from the Powerboard Tyche last August, a picture extracted from the Test Report provided by the hardware designer.

![]()

As you can see above there is some difference of PORESET_B and HRESET_B between what was found during the hardware tests on pur board and what is expected in the NXP manuals.

In September, a new series of tests were performed. Below are two pictures from the oscilloscope showing the output of different attempts while reprogramming the CPLD of the Powerboard Tyche.

![]()

![]()

As we can see on the screenshot even the tension of 2,51 volt was wrong, as it should be not more than 2 volt.

During September and October, there were many reprogramming cycles of the CPLD. Each time, the hardware designer recompiled the HDL of our CPLD and sent it to our firmware engineer, who had two prototypes in hand. Reprogramming the prototypes was quite slow, as neither the hardware designer nor the firmware engineer were working full-time in our project. We sent one prototype back to the hardware designer, and by the end of October, he had completed the CPLD updates. At the end of this hard work the CPLD finally generates the expected power-up signals, reproducing the same signals generated during power-up of the NXP T2080-based DevKit.

The final version of the CPLD firmware (published on GitLab) modifies the behavior of the two signals PORESET (yellow) and HRESET. Indeed, the oscilloscope shows that the two signals now behave differently compared to previous versions.

By the end of October, the signals on the Powerboard Tyche finally looked correct (picture below)

![]()

As you can see the now the tension is correct, around 1,95v, in August was 2,51v

Unfortunately, the changes to the CPLD did not resolve the boot-up process of the entire board.

Strangely enough, during tests we found differences in the power-up behavior between two of the prototype boards: one in the hands of the firmware engineer (FE) and the other in the hands of the hardware designer (HE). Here are the three differences we found:

- On the HE board, the ASLEEP LED stays off if the SD card with U-Boot is inserted and lights up if it is not inserted.

- On the FE board, the ASLEEP LED always stays on, regardless of whether an SD card is inserted or not.

- On the HE board, the oscilloscope shows activity on the SD signals, while on the FE borrowed, there is no activity at all.

We are investigating the possible causes of this different behaviors, such as a potentially different patches. We have sent the third prototype, which was in the hands of Roberto Innocenti during the presentation in October-November 2023, back to the hardware designer to verify its behavior.

Differences were also found while performing the usual test with our JTAG debugger, where we encountered some unusual and strange characters in the output.

New Partners to reach the goal

Due to the significant latency and unreliability of the original hardware designer, we are now forced to find other partners to reach our goal of having the motherboard ready for production in 2025. We started the process of searching for a new company in August, and finally, in November, we found a new highly skilled Italian company for prototype production. This company has decades of experience and a new hardware designer with experience in PowerPC design, which is a great accomplishment for us since such expertise is becoming increasingly rare.

In the transition from one company to another, we are now facing some additional work because the current PCB design is based on Mentor Expedition software (a software now acquired by Siemens), while the new hardware designer uses the Orcad software. Fortunately, we have previously worked on such a task and have already attempted the conversion to Altium software. However, we will need to perform the conversion with greater care to ensure that all components are completely and correctly exported.

The past work on the mechanical aspects of the PCB to fit it into the Slimbook chassis was performed by a previous company that unfortunately generated some dimensioning errors in our existing prototypes therefore the new company has to fix also these problems.

Even if this new company was already known as it successfully worked with ACube System in the past, it was not previously selected for working on the laptop because of its somewhat higher cost. So at this point we are left with no choice but to entrust the job to them if we really want to find out what’s wrong with the board.

Required changes to the motherboard

We have already had the opportunity to explain the history of the board to the new company and to the new hardware designer and requested their investigation into the possible causes preventing the board from booting up. We agreed on a complete and in-depth analysis of the entire pre-boot process of the board. Based on their checks, we may need to implement further patches or introduce additional changes to the electronic design as a worst-case scenario.

The new hardware designer , obviously had other projects running before starting ours and will be able to start working on our board by January 2025.

In addition to potential electronic fixes, we have already planned some hardware changes as stated in a previous post (link). The goal is to make new prototypes with changes that will lower the overall cost and to do so, we will drop the SATA3 chipset, which is quite costly and considered obsolete due to the presence of three M.2 connectors. We will also drop the SIM card reader and one of the two EPROMs, as we only need one.

![]()

Due to the unknown amount of work required, the cost of the activities to be carried out by the new company cannot be estimated. On top of that we plan to make new, hopefully final, prototypes that should cost around 1500 euros each plus around 2000 euros for setting up the prototype production plant.

Campaign Change and Upgrade.

We particularly thank to all recurring donors that keep a constant contribution allowing us to keep the project ongoing.

We have updated the current donation campaign, postponing the heat pipe redesign for a later stage, and refocused on supporting the required work to make the Powerboard Tyche function correctly.

To reach the new goal, we need to pay a new hardware designer that will help us understand what is wrong with the current motherboard prototypes, potentially leading to a partial electronic redesign. We need to produce a new prototype with mechanical fixes, ensuring the correct placement of the board inside the chassis and some connector placement adjustments. Additionally, we plan to drop the SATA3 chipset, the SIM card reader, and the unnecessary additional EPROM.

In addition, we still have to pay the firmware engineer, who was fundamental in making progress in 2024. Without his strong work in fixing and comparing signals between the NXP T2080-based DevKit and our motherboard prototypes, and his continuous feedback to the hardware designer, the needed fixes on the CPLD (Lattice LCMXO640C-3TN100C FPGA) would not be possible.

Donation Campaing for OSHW PowerPC Notebook

Call for a Scientific & Technical Committee

We are setting up in our not-for-profit association a Scientific & Technical Committee that, for example, will provide solutions for our Open Hardware project, examine other Open Hardware projects, adopt other OpenISA CPU, and develop additional Open Hardware Notebook design. Anyone of the associated member of the Power Progress Community will be able to join this committee.

By establishing this committee, we intend to make our association and our PPC Community a suitable place allowing the personal and social development, sharing the motto “Knowledge in solidarity and to be in service of liberation from conditions of constraint and oppression and for freedom of choice”.

Call for developers

We ask any capable developer to increase the number of software supporting PowerPC 64 bit platform (aka PPC64) as the target architecture. In particular, we welcome anyone willing to introduce support for the big-endian variant of the PPC64 architecture, the only one supported by the NXP T2080 CPU that we selected for out PowerPC notebook.

We are currently revising our GitLab based repositories that we setup during the last years while trying to add support to the PPC64 platform. We invite existing and new collaborators to identify potential libraries and GNU/Linux applications to which they are willing to work on, even adding support to a small piece of software may allow bigger application to start working on PPC64 architecture, do not underestimate what even a small contribution may achieve in a bigger picture.

More software working on PPC64, means a better chance for our Powerboard Tyche notebook to become a useful piece of hardware for a bigger number of people, making it an appealing alternative for a broader community.

In case you want to help out on any kind of software stack, please contact us or fill our collaboration survey. In case you are already a contributing volunteer to any existing open source software development, adding support for the big endian PPC64 platform is more than welcome.

If you do not have direct access to a physical PPC64 hardware platform, we can provide you access to our IBM Power9 based environment that is kindly provided by OSU Open Source Lab that we thanks so much for their support.

OSHW GNU/Linux PowerPC Notebook

Open Source Hardware GNU/Linux PowerPC Notebook project

Roberto Innocenti

Roberto Innocenti

Tyche By lapaowan

Tyche By lapaowan