The ALU needs a new decoder because I changed the logic of the ROP2 unit... With a working decoder, I can re-implement the fault checker and validate all the opcodes.

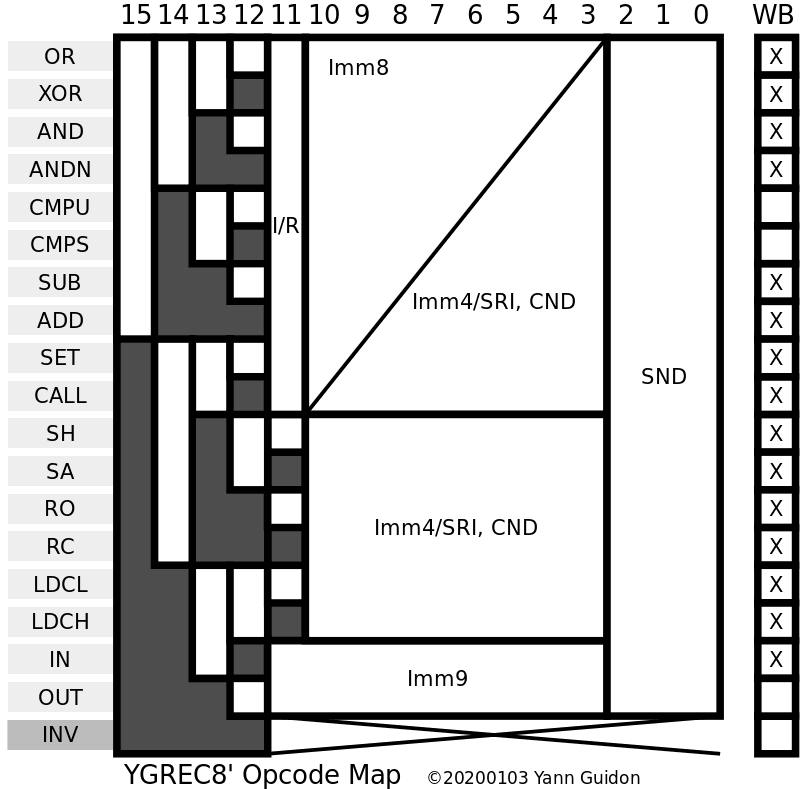

20200103 : I updated files here and there, as well as the main page that contains the "official definitions", because I have changed the order of the boolean opcodes.

I must make a new lookup table that is more thorough than the one at Bubble-pushing the ROP2 as well as the previous versions. There is a big difference, this time I use OR instead of MUX2 to combine the data so there are fewer degenerate cases.

Func NEG PASS_en AND_en XOR_en OrXor_en CLA_en CMPS WB CryWr

OR 0000 0 0 0 0 1 0 x 1 0

XOR 0001 0 0 1 1 1 0 x 1 0

AND 0010 0 0 0 1 0 0 x 1 0

ANDN 0011 1 0 0 1 0 0 x 1 0

CMPU 0100 1 0 1 x 0 1 0 0 1

CMPS 0101 1 0 1 x 0 1 1 0 1

SUB 0110 1 0 1 x 0 1 0 1 1

ADD 0111 0 0 1 x 0 1 0 1 1

SET 1000 x 1 1 x 0 pass 0 x 1 0

CALL 1001 x 1 1 x 0 pass 0 x 1 0

SH/SA 1010 x 0 0 0 0 clear 0 x 1 0

RO/RC 1011 x 0 0 0 0 clear 0 x 1 b11 (RC)

LDCL/H 1100 x 1 1 x 0 pass 0 x 1 0

IN 1101 x 0 0 0 0 clear 0 x 1 0

OUT 1110 x 0 0 0 0 clear 0 x 0 0

INV 1111 x 0 0 0 0 clear 0 x 0 0

Some equations :

CLA_en = F2 & /F3 ROP2 = /F3 & /F2 F0F1 = F0 | F1 /F1F0 = /F1 & F0 /F1F3 = F3 & /F1 CMPS = CLA_en & /F1F0 CarryWrite = CLA_en | opcode=RC RegisterWriteback = /F2 | /F1F3 | (/F3 & F1) OrXor_en = NOR3( F1, F2, F3) XOR_en = F0F1 & ROP2 NEG = ( ROP2 & F1 & F0) | (CLA_en & F1F0) Cin = NEG (more or less but also need to decode ADD 0 cond) PASS_en = /F1F3 & /(F2 & F0) AND_en = PASS_en | (/F3 & /F1F0) | CLA_en

Maybe a 16×9 bits ROM would be better...

Yann Guidon / YGDES

Yann Guidon / YGDES

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.