-

Project Gracefully Terminated

04/18/2019 at 06:34 • 0 commentsI am officially ending this project and beginning a new one called the Ternary Computing Menagerie.

The purpose of this project was to educate myself while making proof of concept balanced ternary combinational and sequential logic gates. Mission accomplished!

Furthermore, other projects running parallel to mine, such as the Homebrew Ternary Computer and Shared Silicon have also demonstrated proof of concept circuits at the board level and in silicon.

At this point I have shifted my attention to higher level applications of ternary logic and math to start filling in the gap of knowledge about how having three states will affect algorithms, tritwise operations, primitive data types, instruction set architectures, etc. The ternary computing menagerie is my collection point for all such research.

The Tern project will remain here for anyone interested. My recommendation is to read the logs in sequence.

-

Sum Gate Solved

07/05/2016 at 17:27 • 0 commentsThe crazy behavior of the Sum gate's power draw is officially solved. By building up the circuit piece by piece and keeping my eye on the current draw continually, I was able to narrow the problem down quite a bit. It only occurred with the inputs in particular positions, and only when power was first applied to the circuit. This sounded an awful lot like latchup so I figured I must be applying too much current to one or more input pins. Playing around with resistor positions and values didn't solve the problem, but with some [insert preferred search engine here]ing around I ran across a great little document here from Analog Devices. It is entitled "Winning the Battle Against Latchup in CMOS Analog Switches" and it clued me in to another way you can get latchup.

As we all know, one should not exceed any of the absolute maximum values listed in a devices datasheet. As far as I could tell, I was not exceeding any maximums, but I hadn't taken time or relative maximums into account. Some values in the datasheet are dependent on others, and the one tripping me up was the maximum allowable voltage on an analog input. The highest voltage on an input is equal to the supply voltage. But on initial power up, which one gets power first? In my case, apparently it was the analog input, thus making that voltage higher than the supply voltage which hadn't quite gotten up to speed yet. Therefor I was exceeding maximums and the device latched up causing a low impedance connection between the input and the power rail. Voila!

The solution? This is covered quite nicely in the document as well and consists of nothing more than placing a schottky diode in line with the power pin of the analog switch. I don't quite follow why this works (magic probably) but it does the trick.

Along the way I also tweaked a lot of resistor values to bring the overall current draw to between 14 and 18 mA depending on what the two inputs are set to. I want to fiddle around with this a bit more to see if I can reduce that further and then I will post a revised schematic.

-

Final Ternary Monadic Gates Using MOSFET's

07/04/2016 at 04:57 • 0 commentsHere are the gates from K through X using only MOSFET's.

-

More Ternary MOSFET gates

07/03/2016 at 09:32 • 0 comments -

Another Rabbit Hole

07/02/2016 at 08:02 • 0 comments<Sigh>. I got sidetracked again by accidentally discovering how to do everything I've already done in a totally new way. I have recreated and tested every ternary monadic gate using only discrete transistors and accompanying passives. I don't even need the +1V and -1V references for these. Now I know for a fact that there is no technical reason why ternary gates cannot be miniaturized and implemented in silicon. It would be an old non-CMOS process, but it would work. I worked up the first eight gates so here they are. I'll post the remaining gates when I get a chance to document them. Then back to rebuilding a Sum gate that doesn't shoot itself in the foot.

On a related note, I also took a second look at a project called the Trimux that I had previously disregard as being pseudo-ternary. I had misunderstood that it accepted binary inputs and had ternary outputs. Now that I look at it more carefully, I find that it really is ternary and more elegant than any of my existing techniques in many ways. It is based on pass-transistor logic (which I've already implemented slightly in my Flip-Flap-Flop and ill-fated Sum gate) and quite simple. I'm looking forward to plagiarizing shamelessly ;)

-

Keeping Current

06/23/2016 at 08:54 • 0 commentsI've been engaged in a detailed analysis of current consumption by various ternary gates in different configurations so as to better understand why the Sum gate was drawing so much current. I've concluded that by drawing more current than the wall wart could supply it became damaged which resulted in the crazy measurements I was getting right before it died permanently.

Since then I've been studying how much current is drawn by different configurations of the ternary gates such as with different pull-up, or pull-middle resistors, different resistors on the input pins, terminating or not terminating unused comparators on an IC and so forth. Over 160 individual measurements so far. The conclusion I'm coming to so far is that I should have been using larger resistors for my pull-ups and pull-middles, and that I should not have been neglecting resistors on the comparator inputs. The LM393 comparators and discrete transistors don't have any difference in current draw by adding input resistors, but the LM319's have a significant difference. This doesn't fully explain how I was drawing over 200 mA with just six components and no short circuits, but I'll just have to build up the Sum gate again, keeping track of current consumption as I power and connect each device.

-

Request For Help

06/15/2016 at 07:02 • 2 commentsOkay, now that I've killed a power supply, its time to get a professional opinion. I've been trying to track down why my sum gate (rev 2) consumes so much power. While poking around and checking how much power different components consume I saw ridiculous numbers like a 393 comparator pulling over 400 mA, then suddenly changing to around 130 mA, then jumping up to 200 mA. That's just one example. I even tried swapping out IC's to make sure it wasn't a bad component. While checking this all out I detected a faint burning smell (uh oh) and quickly confirmed that every component on the board and my DC/DC converter were cool to the touch. No dice; it was the wall wart giving up the ghost.

My components are as seen in the SumRev2.pdf file and my DC/DC converter is this little module. My +5v, GND, and -5v lines come directly from its outputs. I've also got two simple resistor dividers providing the -1v and +1v references, but I'm sure that isn't the problem because they are only used for high impedance comparator inputs. Does anybody see anything in my schematic that would explain the crazy power consumption? Thanks much if you can help!

Oh yeah. I tried adding all the appropriate bypass caps (not shown in the schematic) out of a primitive urge to perform a magic ritual where knowledge was lacking. As expected, it didn't work.

-

Updated Sum Gate

06/13/2016 at 03:59 • 0 commentsI finished testing more possible ways to use transistors rather than comparators to build up monadic ternary gates and did find a few more than I had before but none of them were of use in simplifying the Sum gate. I did however find an error (a transistor source attached to ground instead of +5V), make the diagram a bit more clear, and add the truth table.

So here it is.

-

Thoughts On Premature Optimization

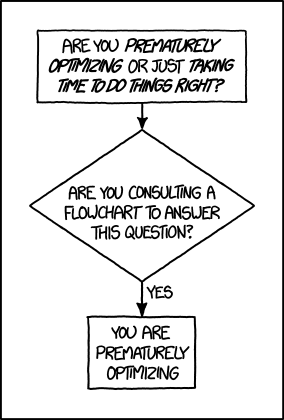

06/10/2016 at 01:30 • 0 commentsAn XKCD comic got me thinking recently... that may be the nerdiest thing I've ever written.

![]()

My general plan has been to create working versions of the ternary gates necessary to eventually build something that actually performs a real function. Specifically, I wanted to build a device that would compute the Fibonacci sequence to three trits. I have now proved the functionality of every component that would be needed to do exactly that.

At the same time, I have been testing various types of transistors as replacements for the simplest of the ternary monadic gates; those ones which have only two possible outputs. I already posted one schematic that simplifies some of the monadic gates, but have realized that there are more possible simplifications to be made in that area. I've just received a delivery of more depletion mode transistors to test.

Finally, I've also been checking out current draw in these circuits and was surprised to see over 200mA being used by the Sum gate. I need to go through the different circuits I've already built and tweak the resistor values to bring that down to something more reasonable and while I'm at it, I might as well add bypass caps to all the schematics in the appropriate locations.

So basically I'm looking at a considerable amount of testing, iterating existing circuits and verifying the improvements, and documenting the improved circuits. All this before I've actually built anything beyond solderless breadboard prototypes. In other words, premature optimization.

Instead, I think I'll finish testing the transistors, use that data to improve the Sum gate if possible, document it, and then build a three-trit adder with three position switch inputs and LED outputs. This is a much more modest first-build than the Fibonacci idea, and as such, is a lot more likely to get done. And I hope to do it on a real board through Oshpark. If it all works out it will be my first PCB design.

-

Face Palm

06/05/2016 at 05:59 • 0 commentsAfter going through the trouble of drawing up the schematic for the new improved Sum gate you'd think I would actually post it.

Here it is!

Tern - Ternary Logic Circuits

A series of ternary logic gates and higher level components implemented in the real world.