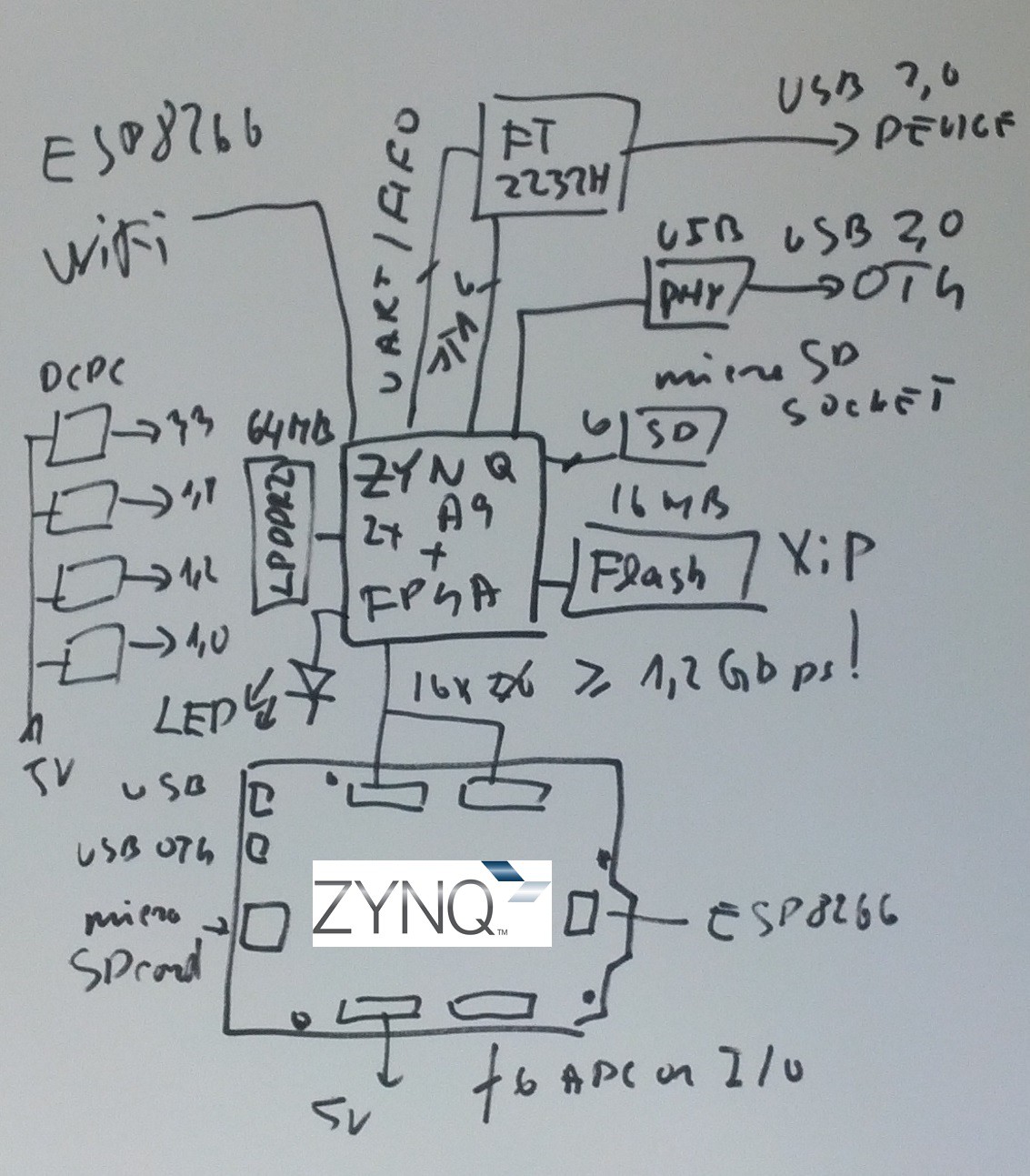

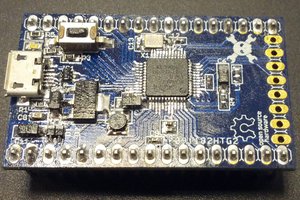

This was my first Zynq Design with LPDDR2 memory, and served as test for the DIPFORTy2 #Soft Propeller upgrade to include USB, HDMI and LDDR2 memory.

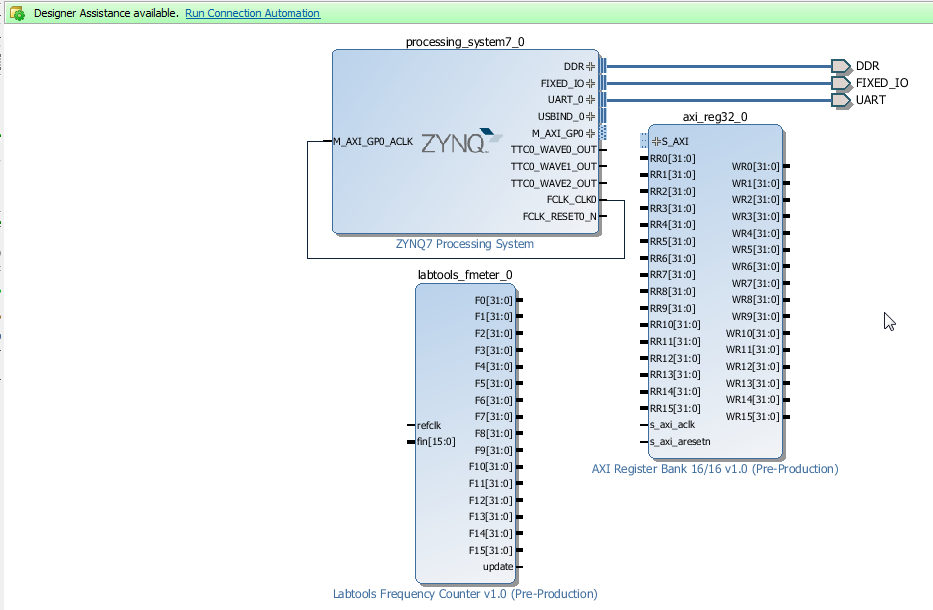

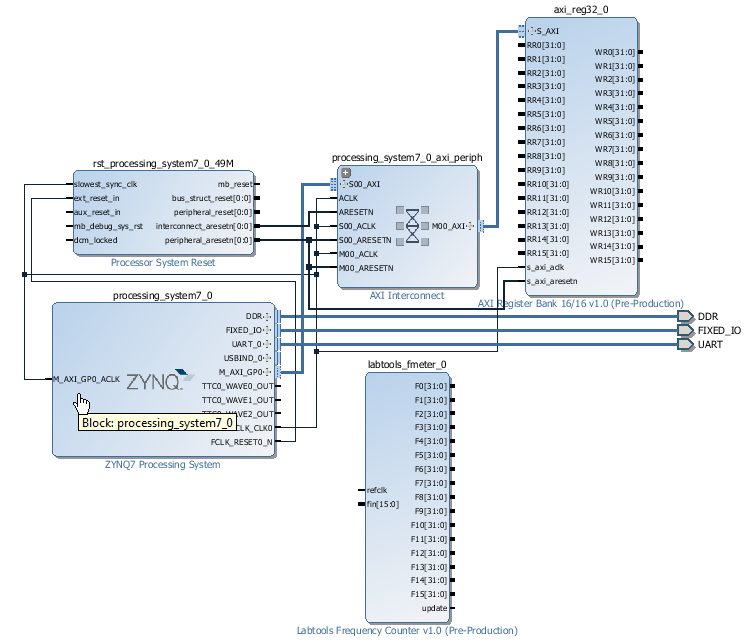

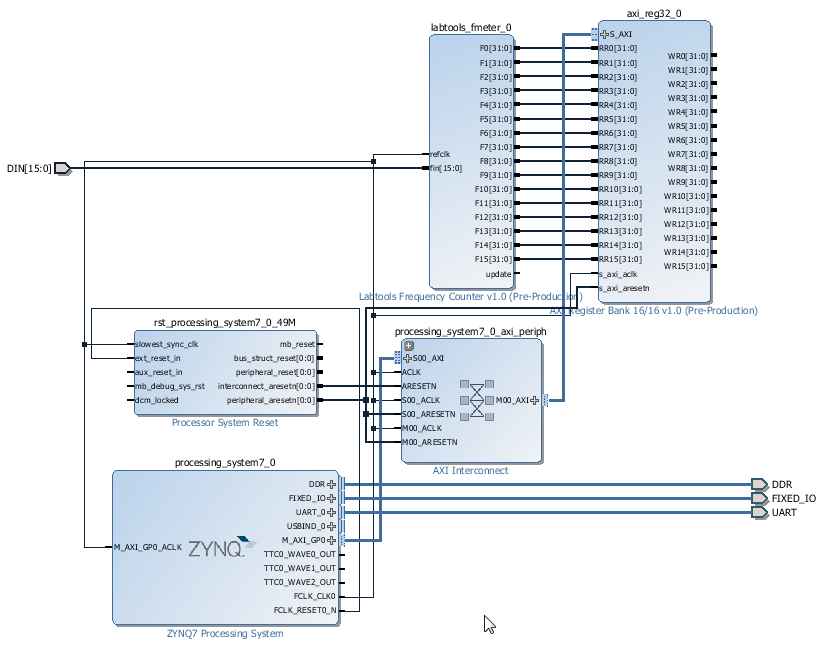

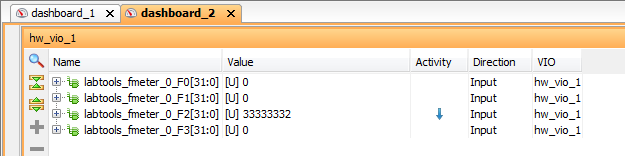

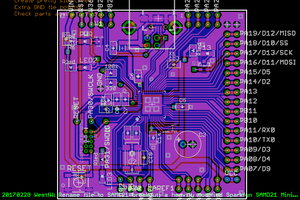

System Design

PCB tech: 8 layers no buried or stacked vias. Micron 64MByte LPDDR2 memory, this memory type needs no special termination and is housed in nice small package as well and should save some power as well.

Licenses

- CERN OHL

- Hardware design

- GPL

- Zynq FSBL

Antti Lukats

Antti Lukats

Michele Perla

Michele Perla

Lithium ION

Lithium ION

WestfW

WestfW

ajlitt

ajlitt

you designed your own computer!

very impressive

the system design diagram isnt funny though..

how much does it cost for 1 or 2 units

even if i want to modify and get someone to fabricate + populate PCB?