-

Baseboard is being designed too

09/29/2015 at 19:38 • 0 commentsWhile Soft-Propeller can be used on solderless breadboard, it is still good to have some base where it can be used and tested so that is now launched as separate project #HackBerry Pi

It converts the Soft-Propeller into RPi form-factor and allows to use RPi hats

-

IT runs propeller code too :)

09/14/2015 at 14:02 • 0 commentsWhile it was advertised as SOFT-PROPELLER, it was not until today it actually works as a Propeller.

Testing on Parallax Development Board, flashed the SPIN code into EEPROM on Parallax board, and well Soft-Propeller configures itself from SPI flash as propeller and then loads prop code from EEPROM.

Soft-Propeller has no on-board EEPROM, but this can be emulated in FPGA there are enough block rams free.

Utilzation:

FF: 15%

LUT: 50%

BRAM; 33%

-

MULTIBOOT Flash Image ready

09/13/2015 at 19:37 • 1 commentThis may sound like small thing, but we have ready to ship Flash image that can either boot ARM Code from SD Card, or then execute multiboot process and configure every thing from second (application) Image in Flash.

The second image could be Soft-Propeller or any thing else.

Of course the code that would be loaded from SD Card can also configure the FPGA and load more software code from the SD card or the Code loaded from SD Card can update the Application image in Flash, so with next reset without the SD Card the new application would be loaded from SPI Flash.

-

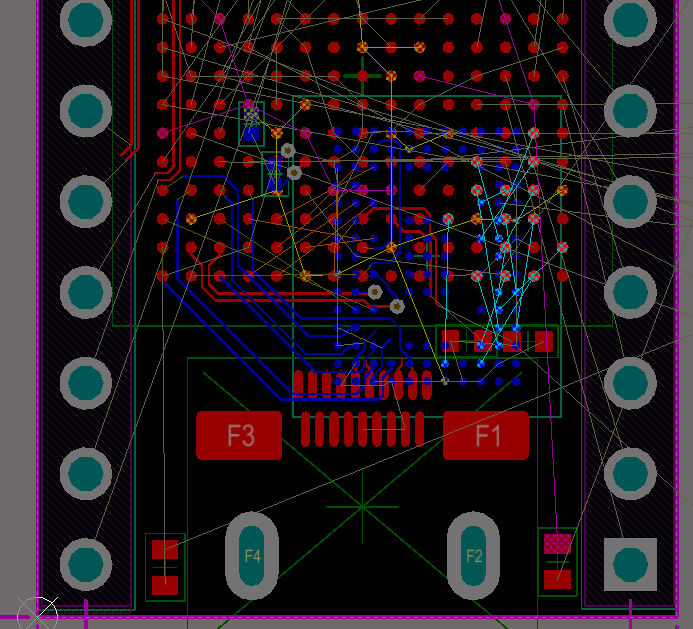

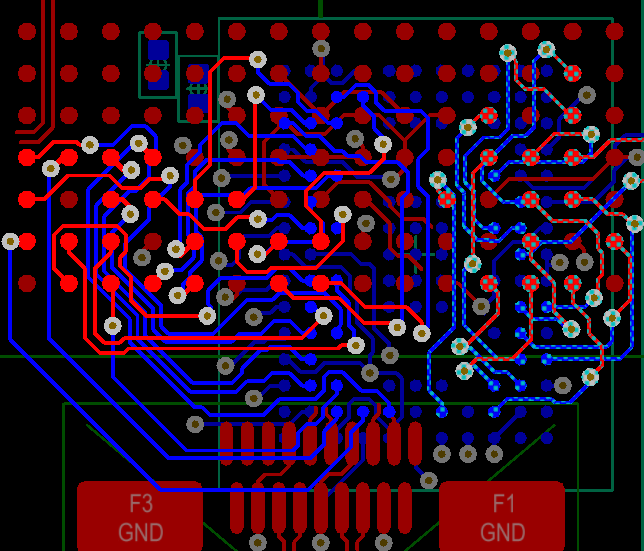

Prop gets more memory

09/11/2015 at 09:51 • 1 commentDIPFORTy2 - a version with external memory and usb and hdmi seems to possible also.

After doing 90 degrees turn the RAM routing looks doable, this is the most dense ZYNQ+DDR routing I have done so far:

This may not be so impressive, but LPDDR2 with 0.65 mm pitch is directly under Zynq BGA with 0.8 mm pitch, and HDMI signals have be routed through the memory routing area, all this on PCB with no HDI technology, no buried no blind vias.

It so often looks impossible until you just do it. LPDDR2 is directly below ZYNQ BGA, all signals routed in top bottom only, not internal signal layers used.

-

Propellers to Finland

09/10/2015 at 14:12 • 0 comments -

SD Card Bootloader working

09/09/2015 at 14:58 • 0 commentsThis may sound like a minor thing, but loading from SD card in the system with no external RAM and no bootrom bootable SD card is really tricky. Well its working now. Later the bootloader will possible use XiP, right it is like this:

FSBL is loaded from Flash

FSBL loads FPGA BITSTREAM from SPI Flash

FPGA "adds" 128K RAM accessible to the CPU0

FSBL loads SSBL from SPI Flash into RAM in FPGA

SSBL Loads S-Records from file on the SD card into OCM RAM

Your code from SD Card is running.

At this point the RAM in FPGA is no longer used and we can re-program the FPGA from file on SD card, or update the SPI flash from SD card..

-

WS2812 IP Core Testing

09/07/2015 at 21:29 • 0 commentsVivado IP Catalog, click click.

Vivado IP Integrator, click click.

Xilinx SDK (Eclipse):

void SetWS28xx(u8 RED, u8 GREEN, u8 BLUE) { putfsl(RED << 16 | GREEN << 8 | BLUE, 1); } while (1) { SetWS28xx(r, g, b); // r++; g++; b++; MB_Sleep(10); };Solder iron, first convert WS2812 to SIPSIK(tm) compliant device, that easy just solder some header!Get 3 wires

Connect the wires

FAIL

Get Oscilloscope, power it on

Can not wait? Look at the wires again, SWAP ground and signal and

you will see

That WS2812 does work, and is controlled by software.

This is first time I ever used WS2812.

As soon as fixed the problem with the wiring, it just worked, namely:

- CPU0 Bootrom did load FSBL into OCM ram

- FSBL did load FPGA code that is the "HARDWARE" from an partition in the SPI Flash

- This BITSTREAM was DMA'd into ZYNQ PL - Programmable logic

- PLL in Processor part of ZYNQ was set to deliver clock to fabric side

- In the Programmable Fabric an 32 Bit Soft core MicroBlaze is booting from Block RAM that was loaded together with the bitstream during the FSBL boot proccesses

- Microblaze exectutes the main.c - code above

- The c code uses special processor instruction that directly writes the data to streaming hardware port

- This data is latched in WS2812 IP core

- The IP core generates the timing

- WS2812 is controlled by the software :)

You think this can not be true?

That this all just works first time tested?

Well then you would not believe I can do #HAD-9000 in 2016 either?

Without your help, I can not. With your help WE can.

Would you like to work on HAD-9000 ? You can.

You can start now with Soft-Propeller, its gives the boost you need to be ready for HAD-9000 in 2016.

-

SDSoC first tests

09/07/2015 at 20:20 • 0 commentsThis is exciting, I think in the next year it will mature, Xilinx SDSoC

http://www.xilinx.com/products/design-tools/software-zone/sdsoc.html

To cut the bla, its really simple: You select platform, say Soft-Propeller, in Eclipse, write some C code, and you get ready to run image that works on the ARM Cores and is partially compiled directly into FPGA hardware.

This works now. It does! SDSoC 2015.2 is first public release so expect some issues, but the basic flow really works.

-

59 EUR - Lowest cost ZYNQ mod ever!

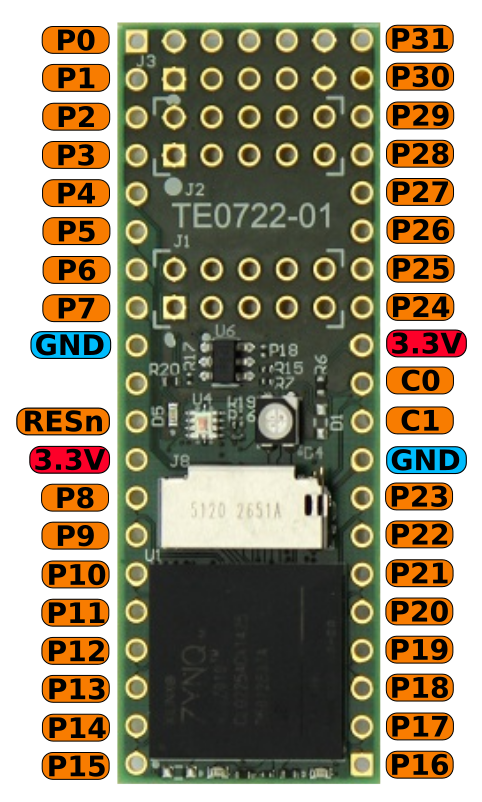

09/07/2015 at 09:57 • 0 commentsDIPFORTy1 "Soft-Propeller" is

- Lowest Cost ZYNQ based Module ever made

- First ZYNQ module that can use existing bases and project boards (Parallax Propeller chip compatibility)

- First ZYNQ based product ever in Hackaday Prize semifinals

- First Xilinx 7 Series based product ever in Hackaday Prize semifinals

Note: TE0722 - warehouse software assigned number :)

Note 2: the Hardware Design files are on github...

-

Prelimary pricing, docu-wiki!

09/03/2015 at 10:50 • 3 comments

Soft Propeller

DIPFORTy1 "Soft-Propeller" Zynq-7, Dual CortexA9+ FPGA DIP40 Parallax Propeller I compatibles footprint

Antti Lukats

Antti Lukats