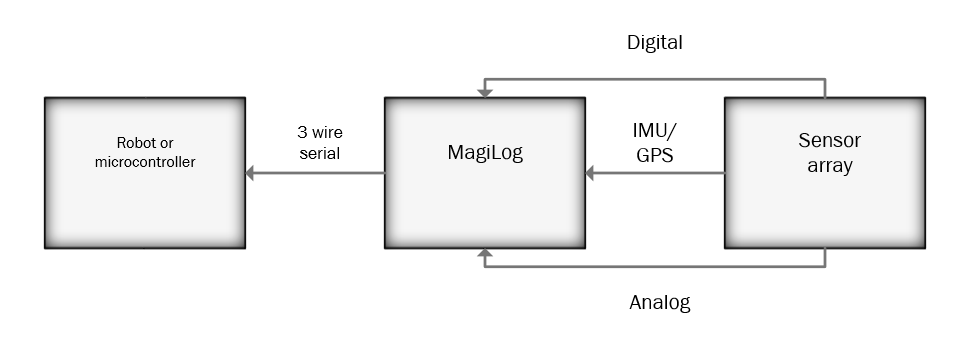

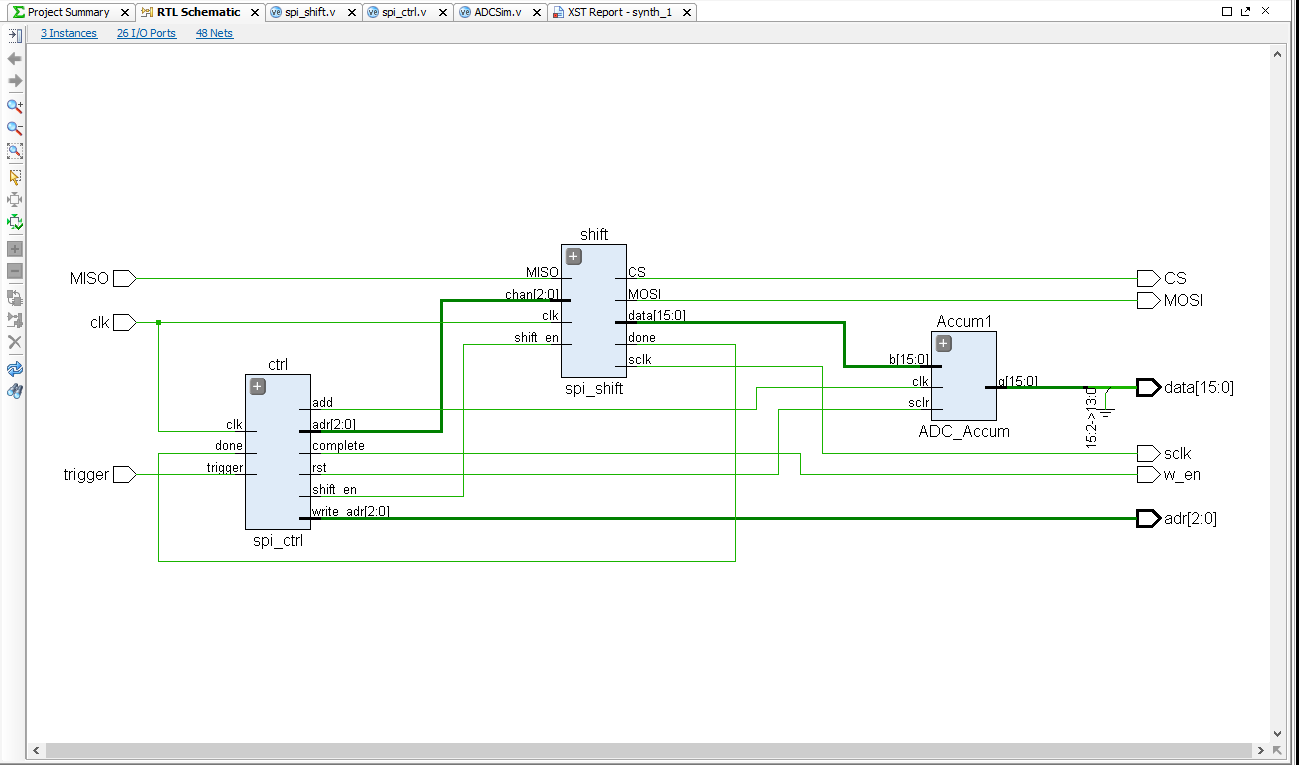

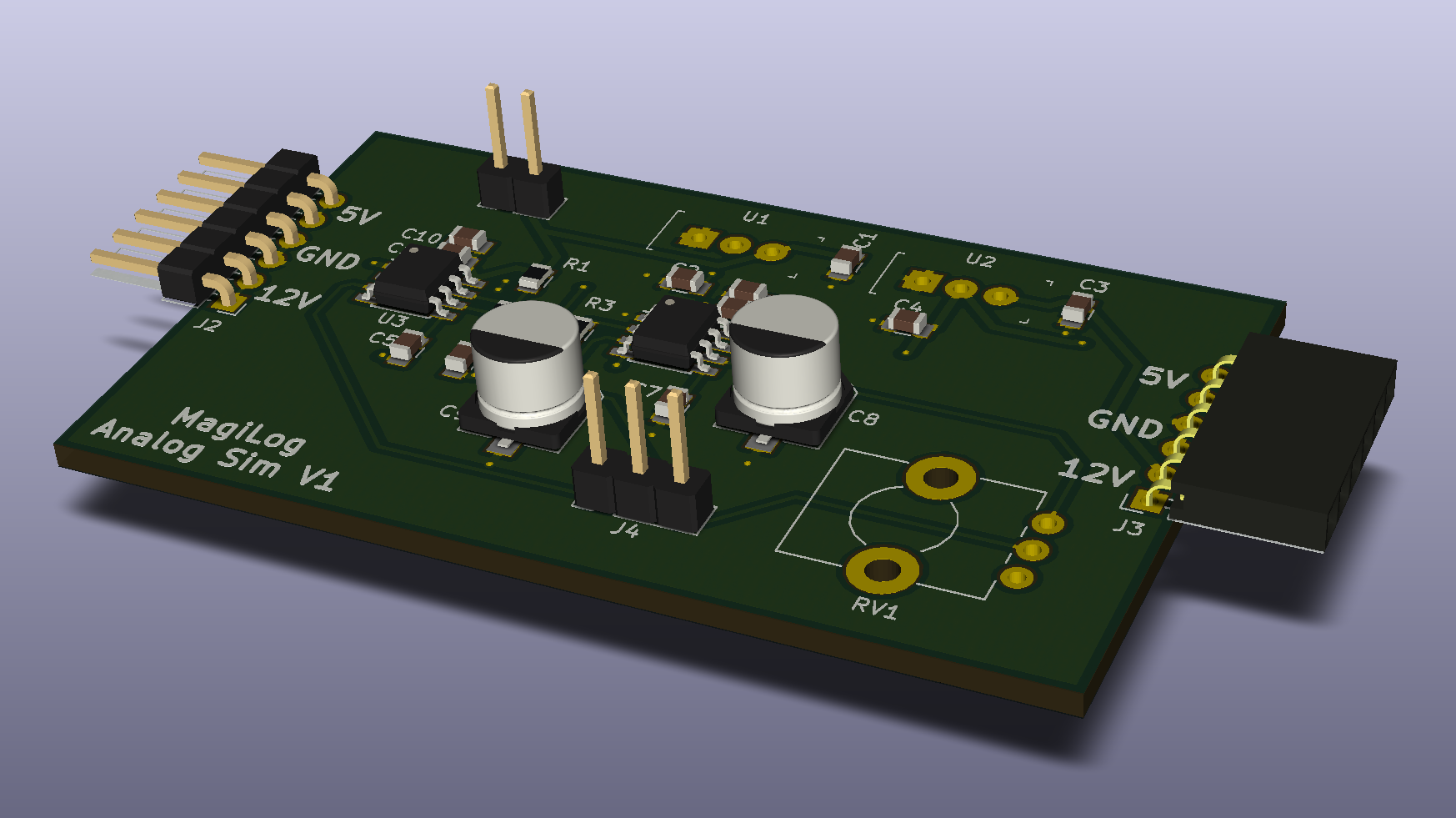

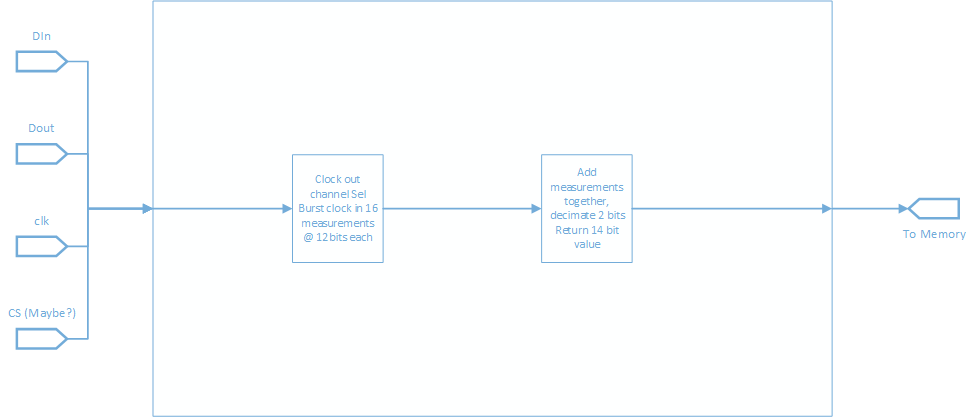

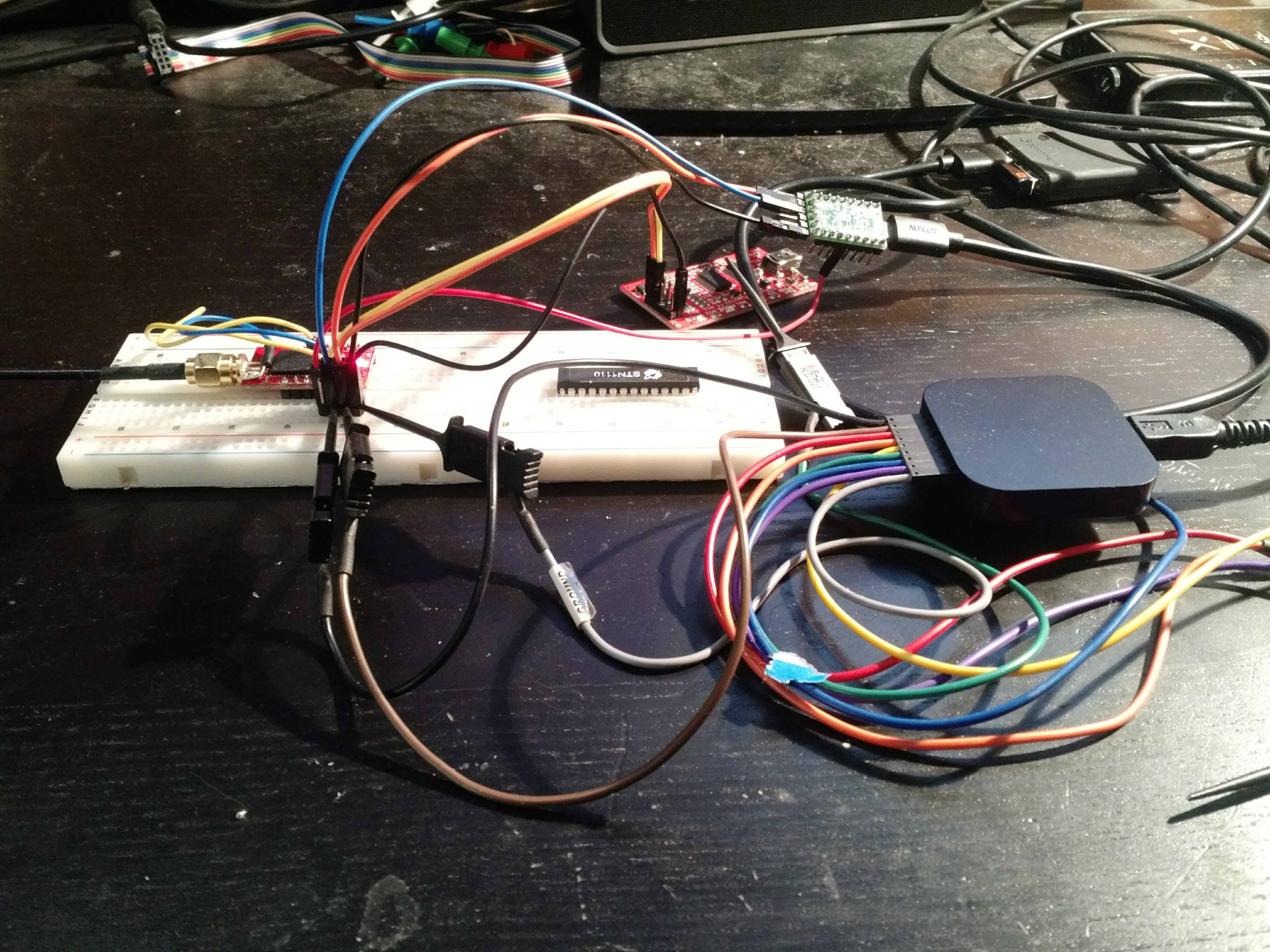

MagiLog is an automotive focused datalogger that is based on an XMega/FPGA coprocessing configuration. The XMega and the FPGA communicate with each other through dual-port RAM. This will allow me to access the FPGA as an extension of the XMega’s memory space through the External Bus Interface (EBI) and then use the DMA controller to send the data to the various communication methods with little overhead. I think this arrangement will allow me the greatest flexibility when it comes to scaling up the design and allowing me to exceed my initial target of 100Hz datalogging.

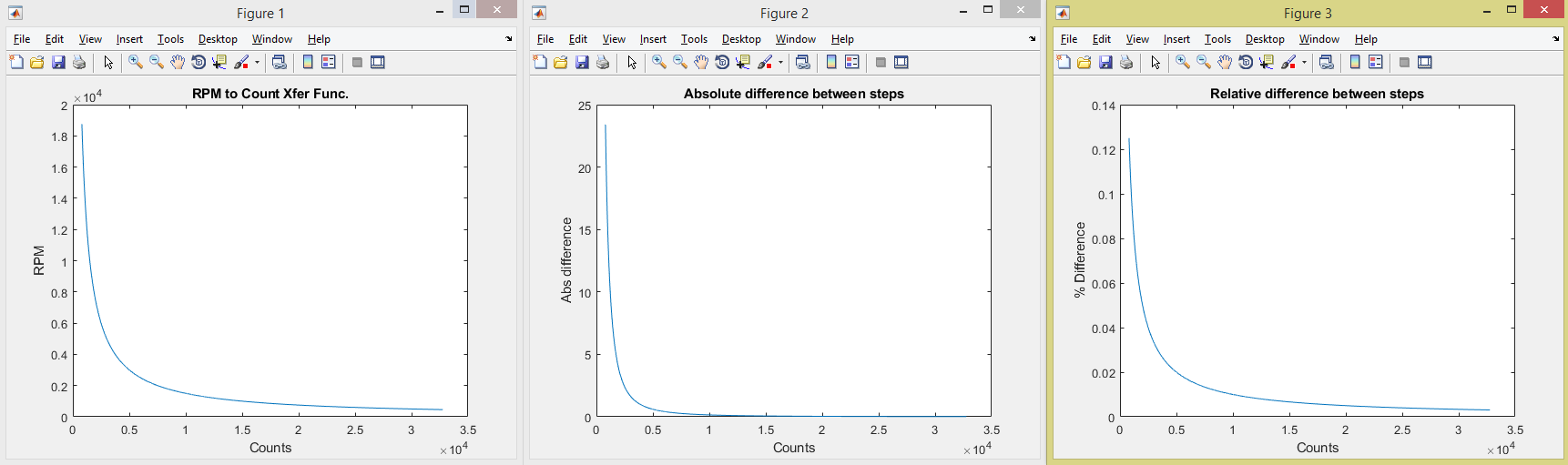

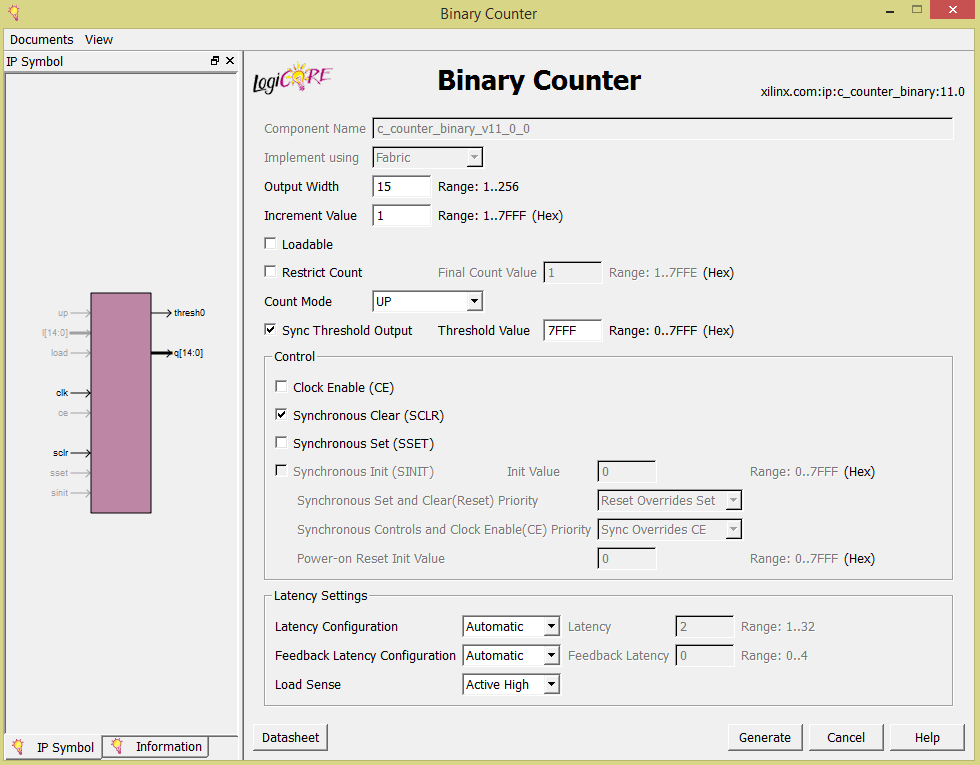

My initial target specs and capabilities are as follows: MagiLog will have 16 analog inputs to interface with various sensors directly. It will have 12 inputs for digital inputs, these inputs can be used to track engine RPM or any toggleable parameters. MagiLog will also have an integrated 9 axis IMU with GPS combined with a Kalman filter or some other sensor fusion algorithm for accurate kinematic tracking. In addition to the direct sensor interfaces, MagiLog will also be able to acquire data from an engine control unit (ECU) through either serial or CAN/OBD protocols.

The logged data can be saved to an SD Card or streamed to another device/computer over Bluetooth and USB.

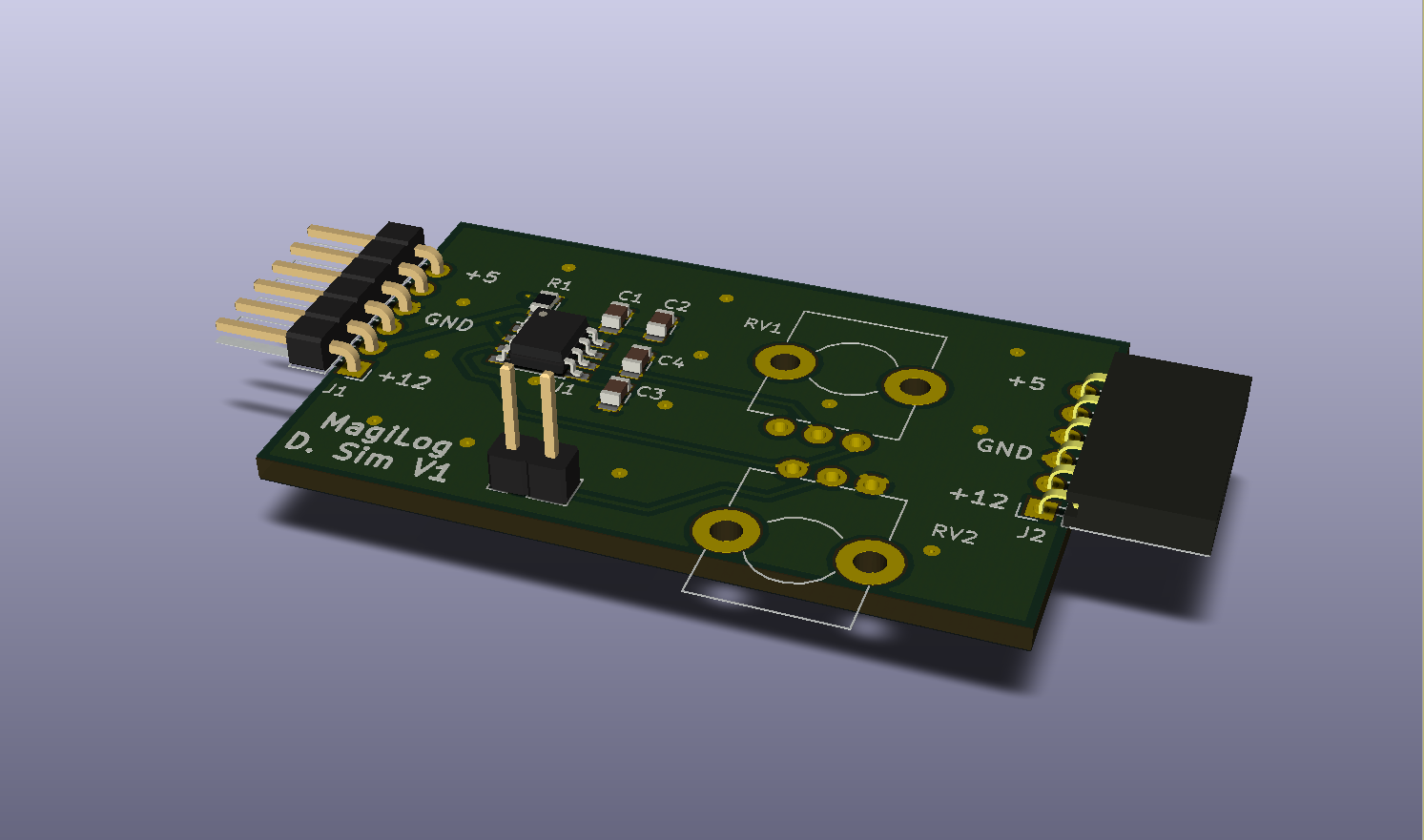

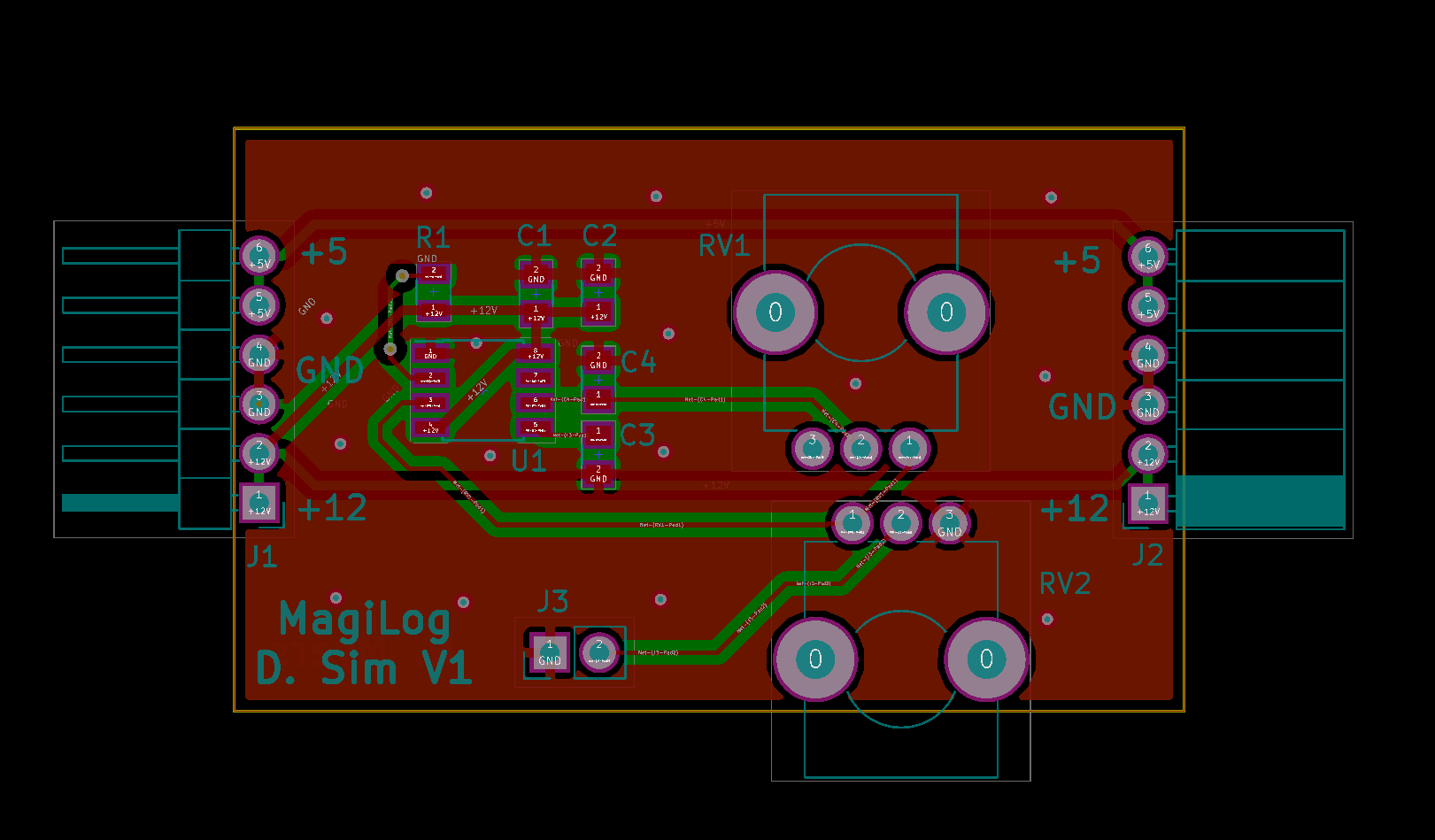

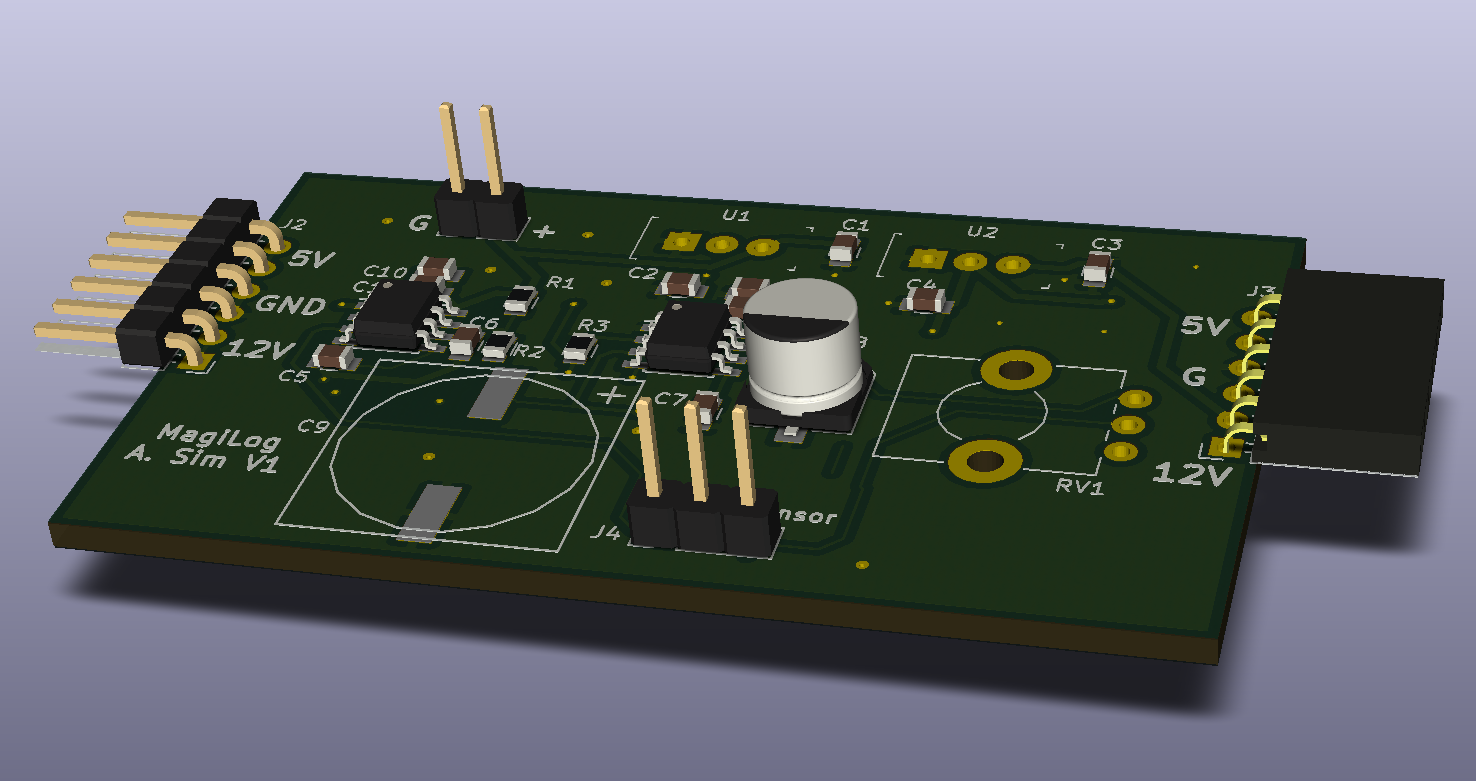

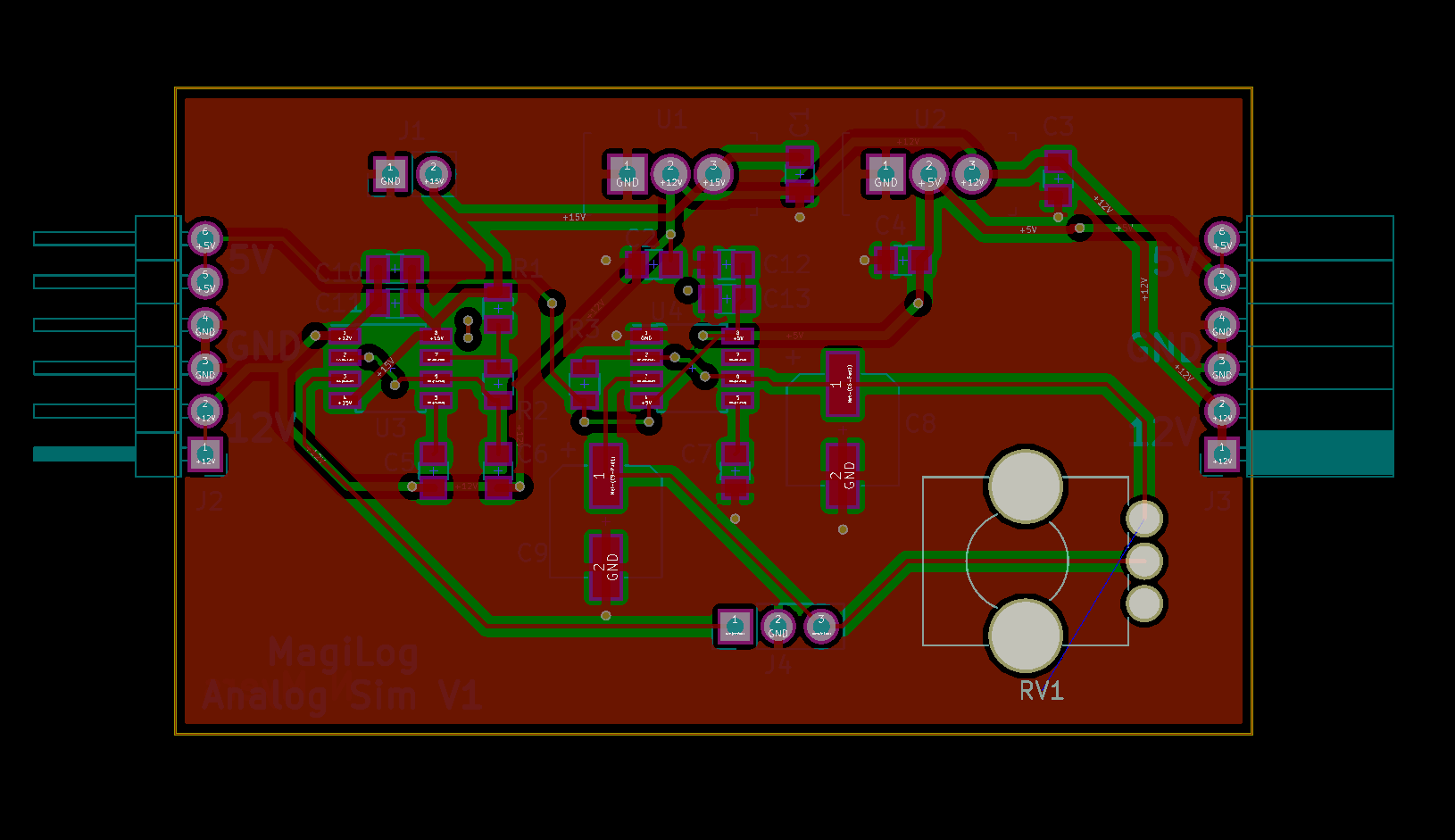

I have all the components specced or respecced and am now getting into the HDL/programming side of things to integrate all the components together. Once that’s done it’ll be time to roll a PCB to get everything on a single board.

For long term expandability it will also have an auxiliary serial port to allow you to eventually add displays or interface with MagiLog with a robot or any other application that can accept a serial data stream.

I’m hoping through the creation of this project page I’ll improve the way I document projects and maybe as a bonus I can teach people how to use the tools I am using to complete this project.

Banner photo from Wikimedia

Nigel

Nigel

Getting the

Getting the

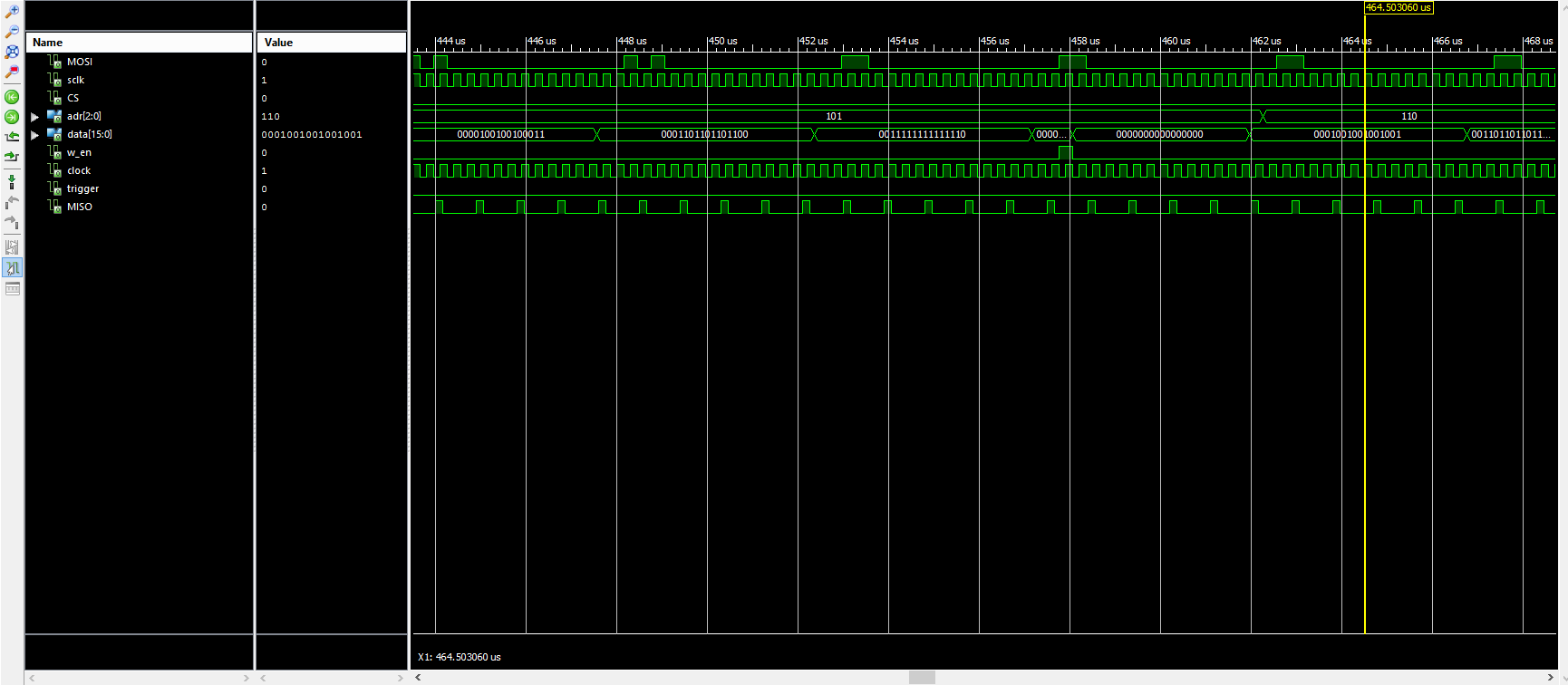

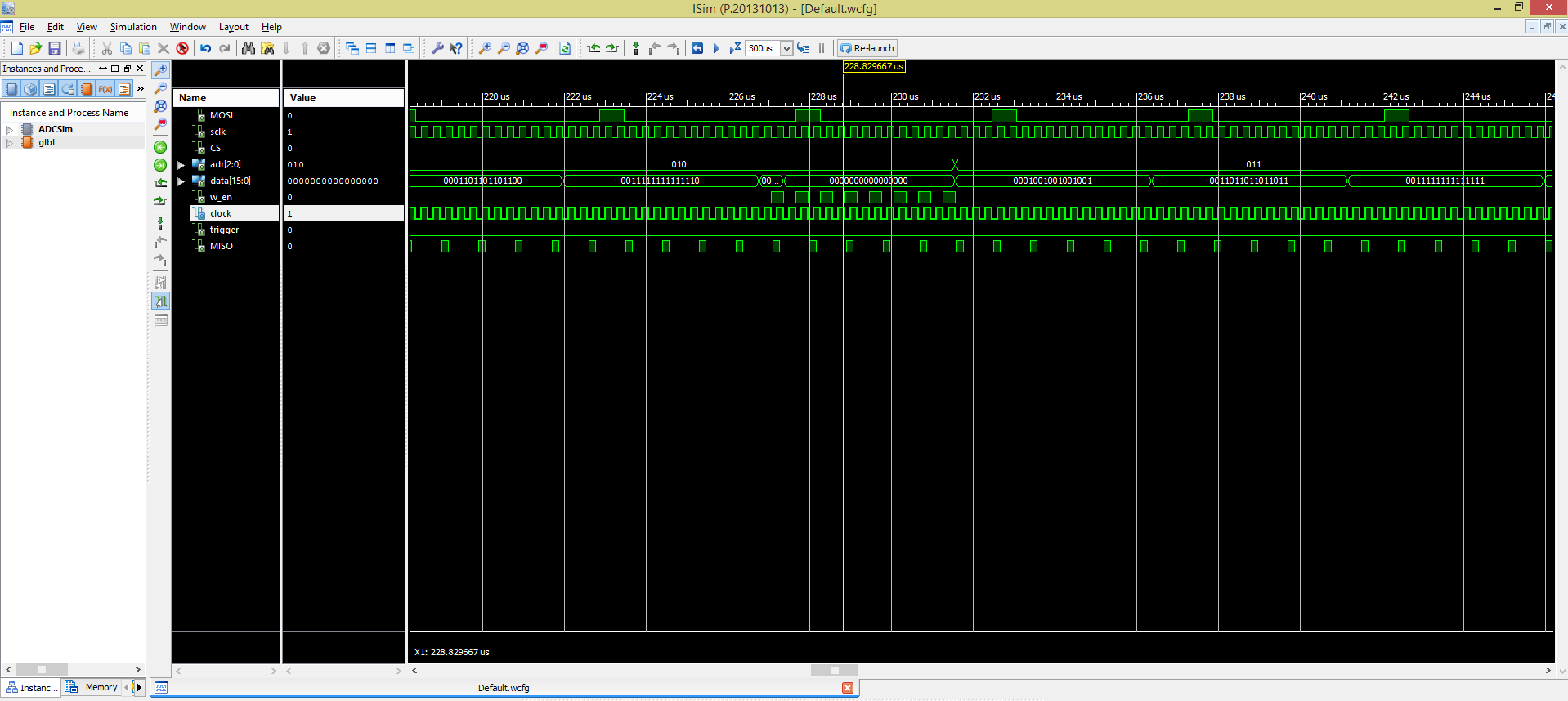

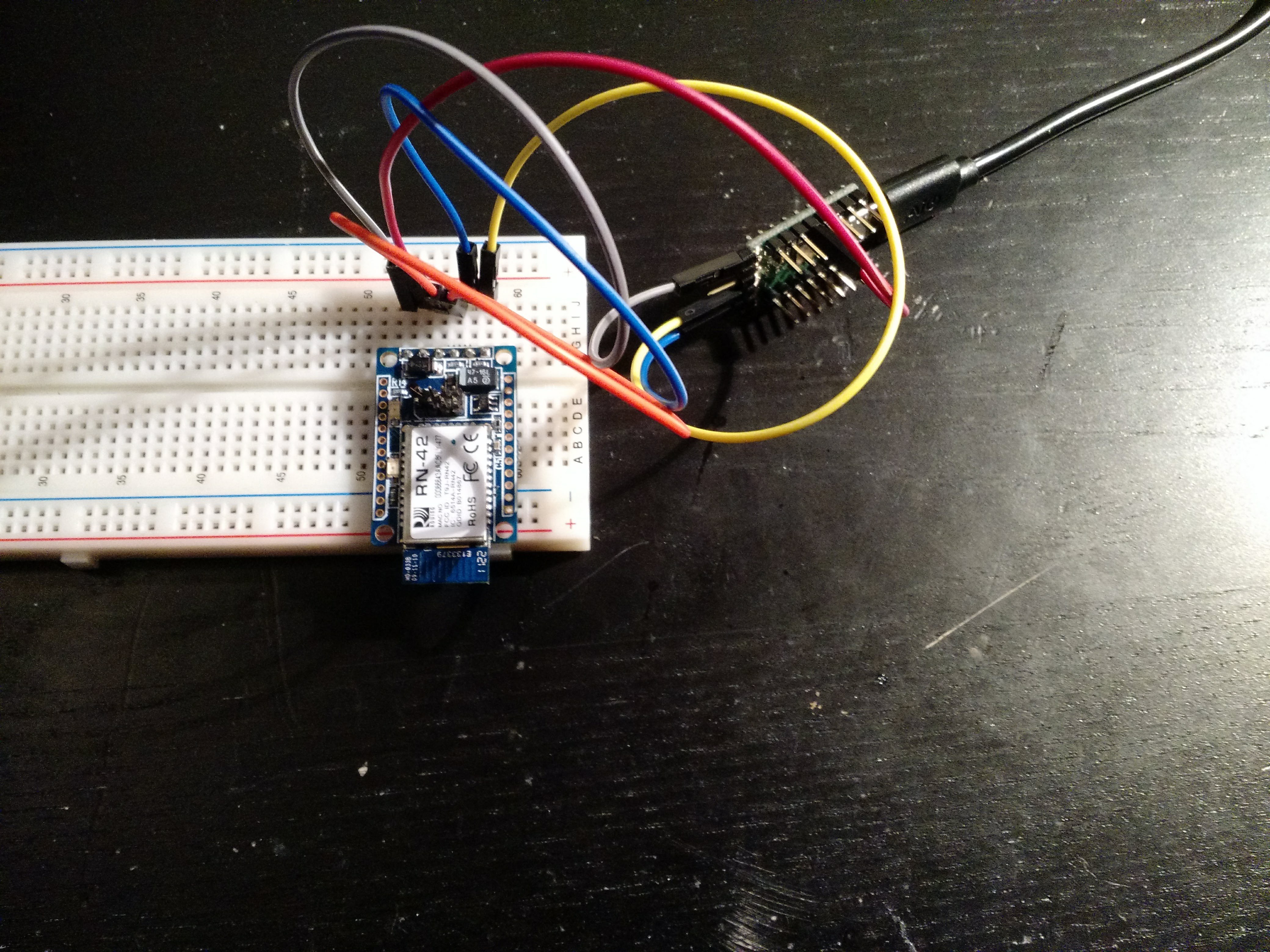

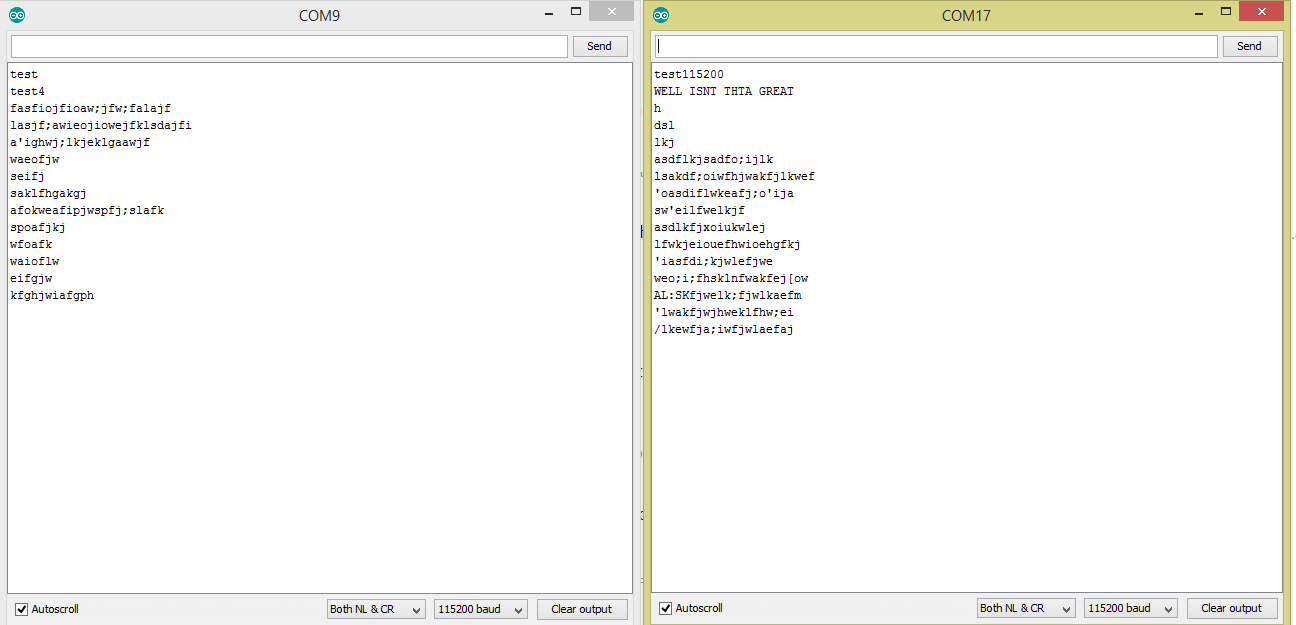

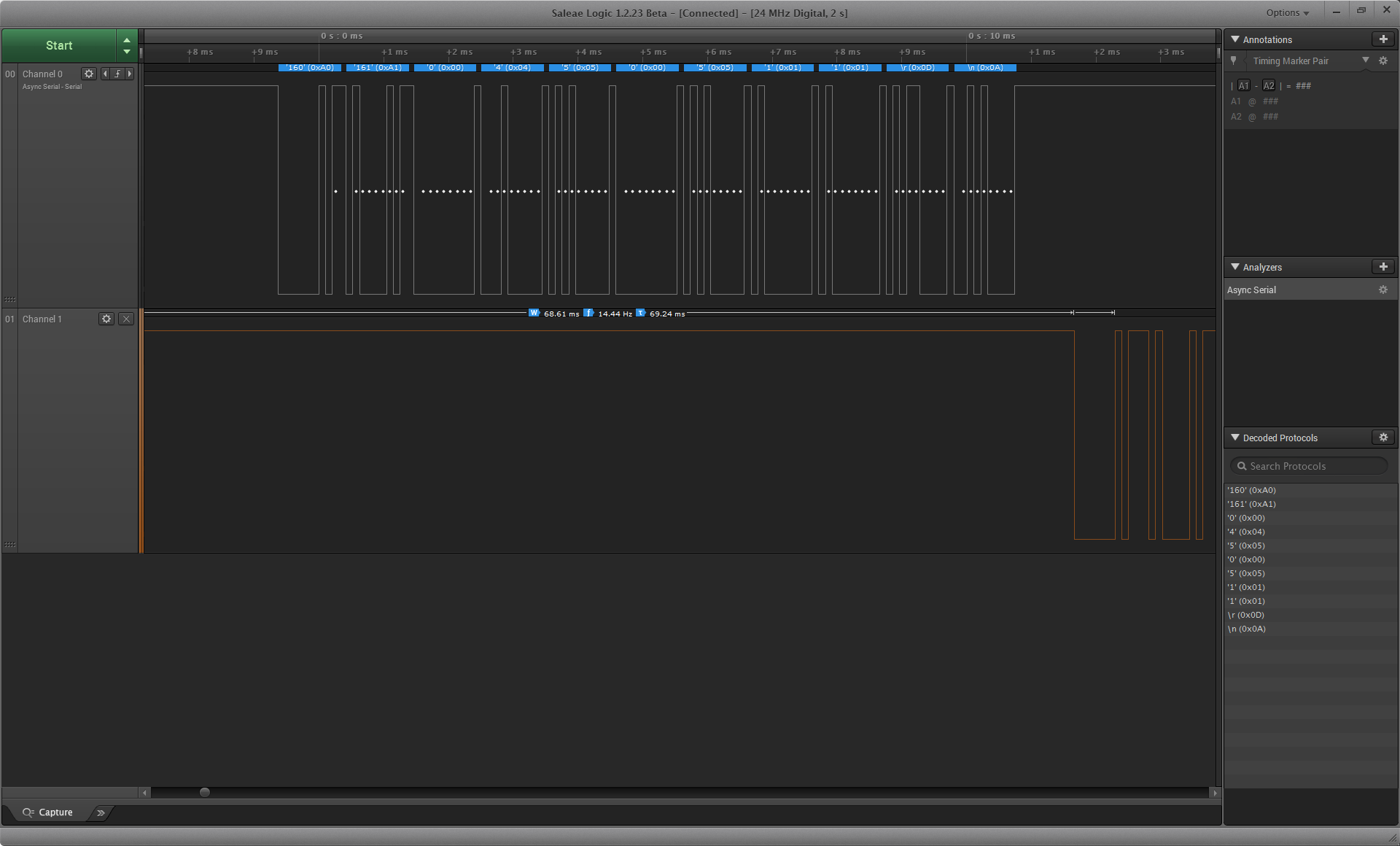

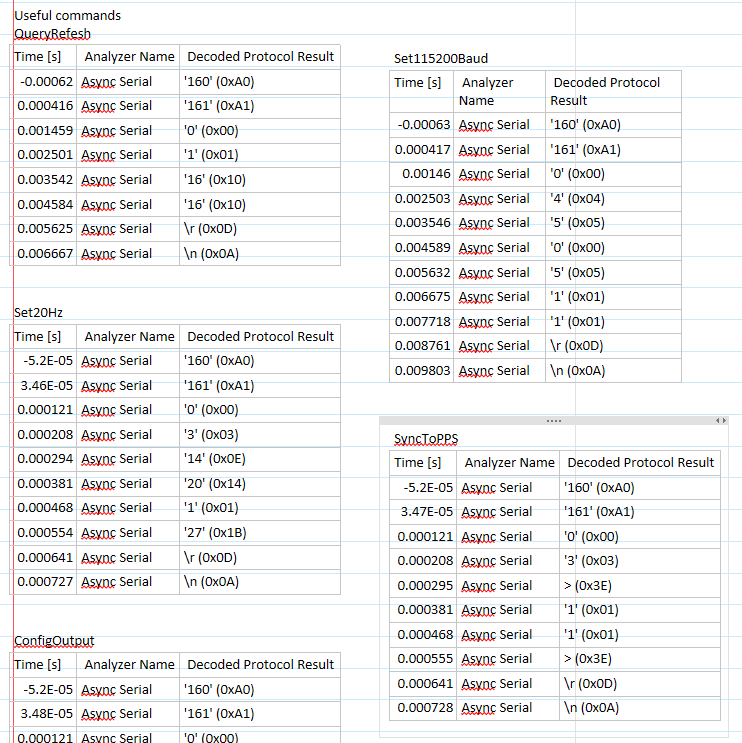

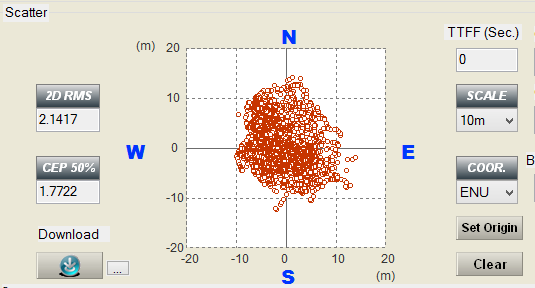

I’m still not sure what the issue was but everything seems to

be working now. I’m able to send configuration messages and have them change

parameters. Now that the problem is behind me I can start digging into the

workings of the module.

I’m still not sure what the issue was but everything seems to

be working now. I’m able to send configuration messages and have them change

parameters. Now that the problem is behind me I can start digging into the

workings of the module.

Simon

Simon

David

David

Saabman

Saabman

Hey, interesting project. See you might be using air pressure sensor for it. Been playing around with some for prototyping and have a project about then if you interested.

https://hackaday.io/project/108157-pneumatic-tech-for-prototyping