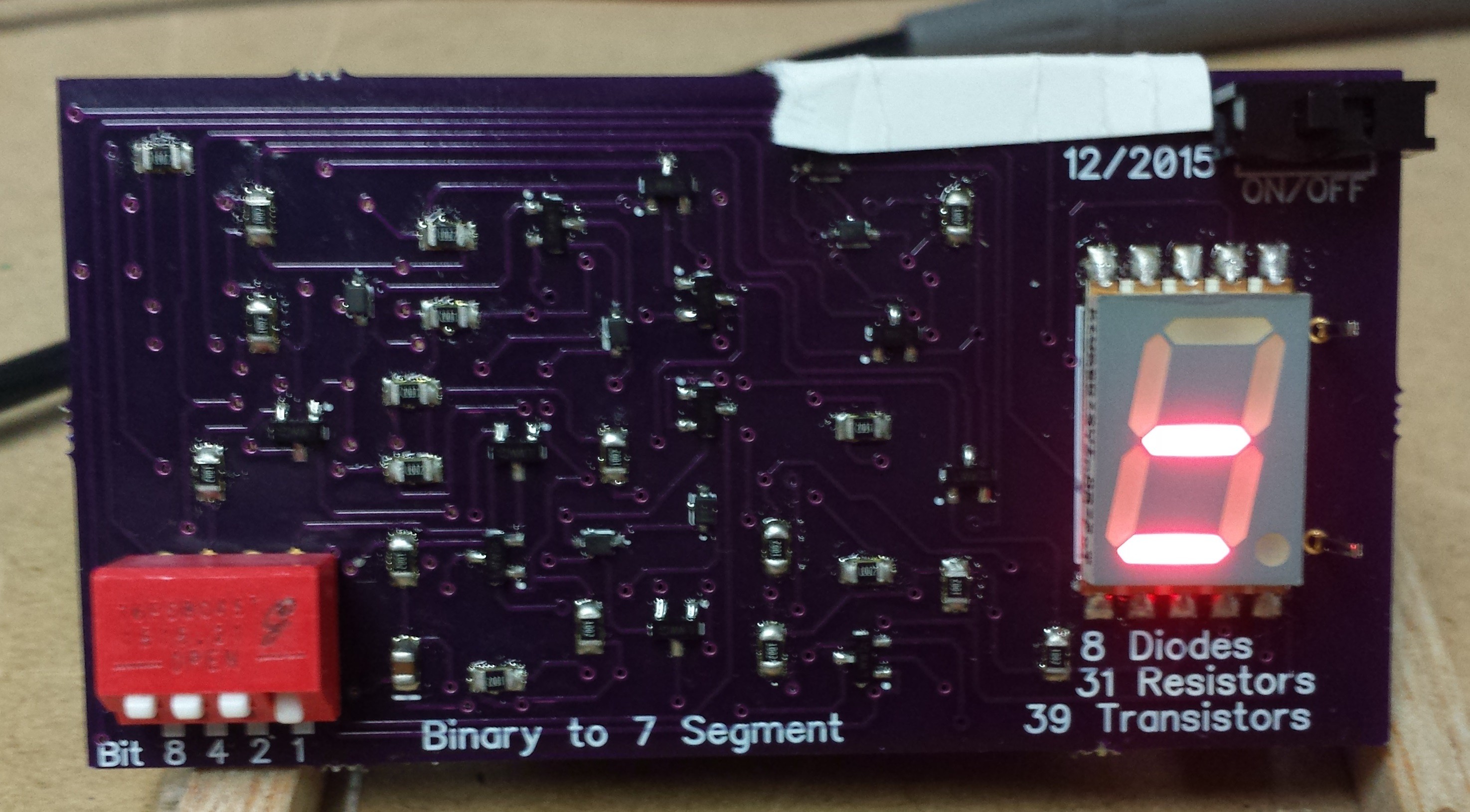

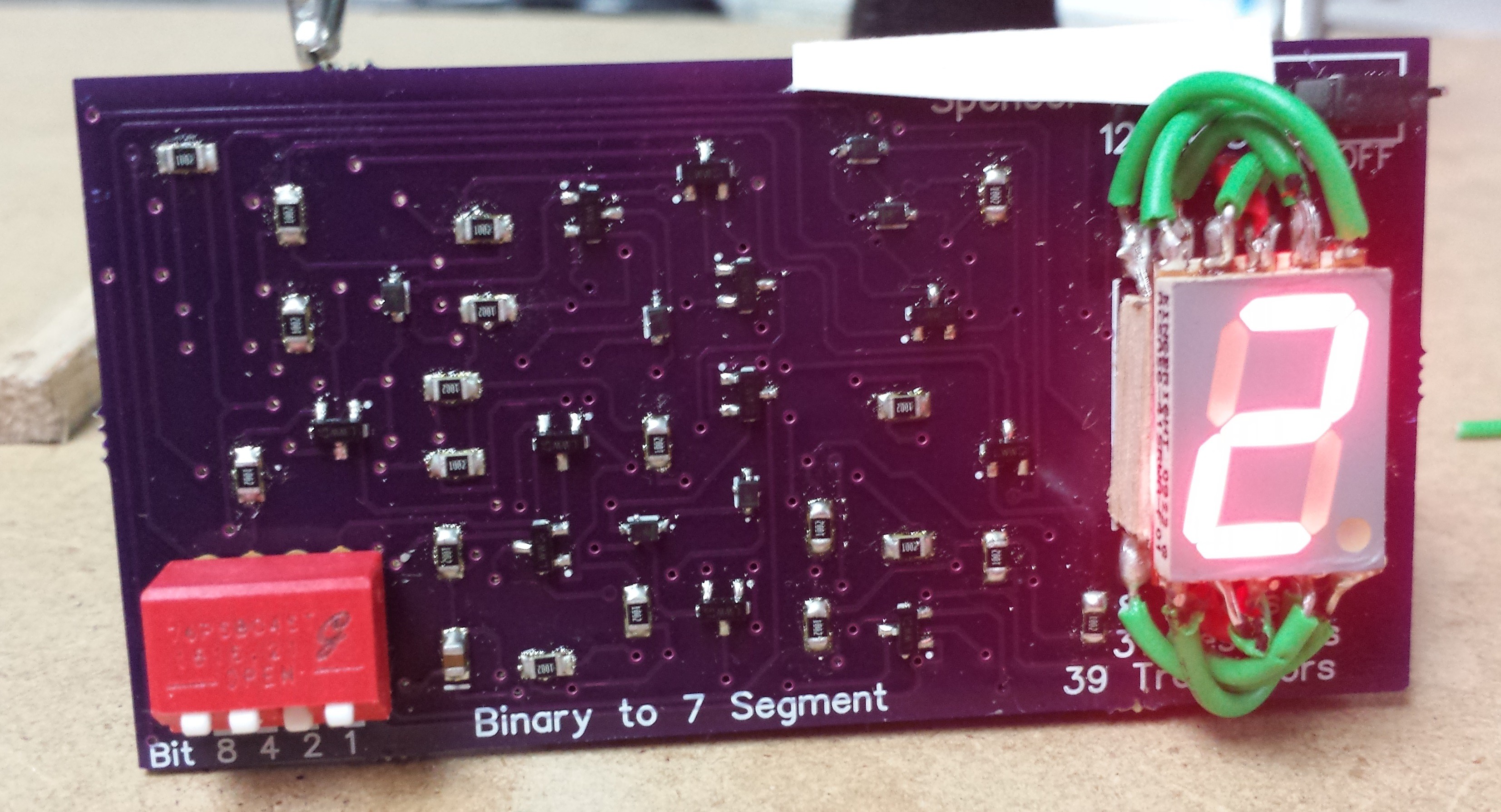

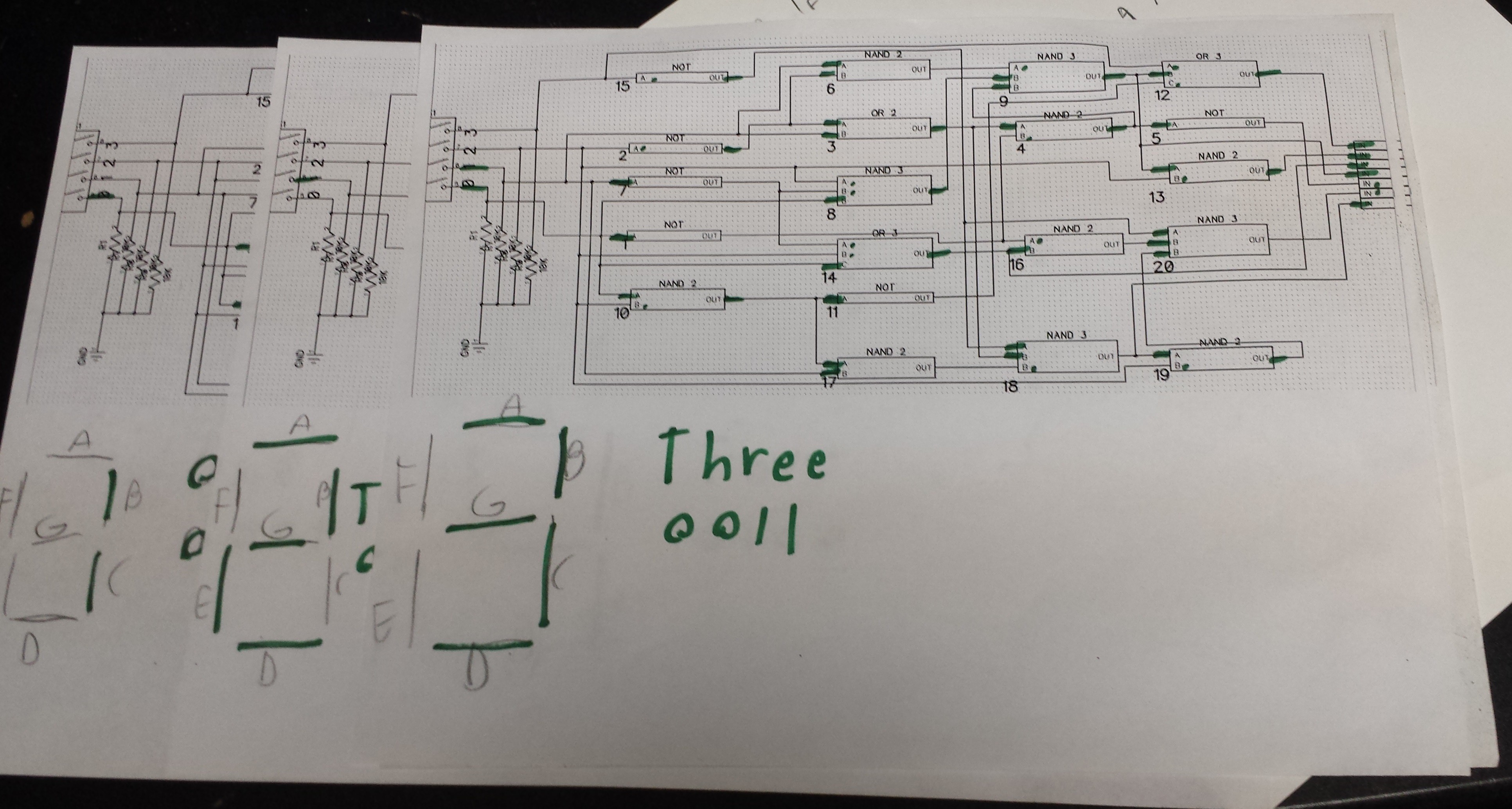

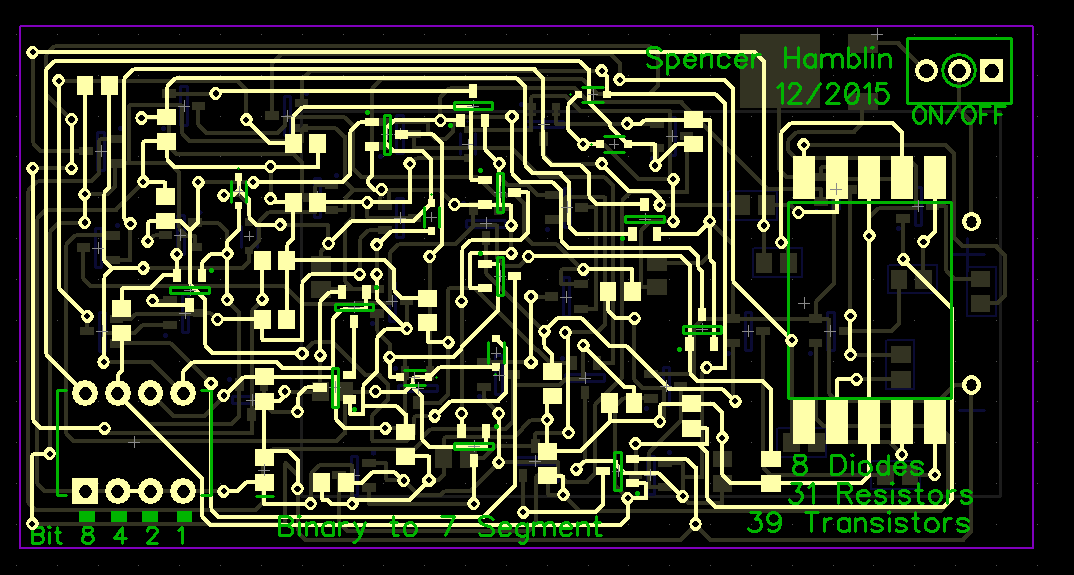

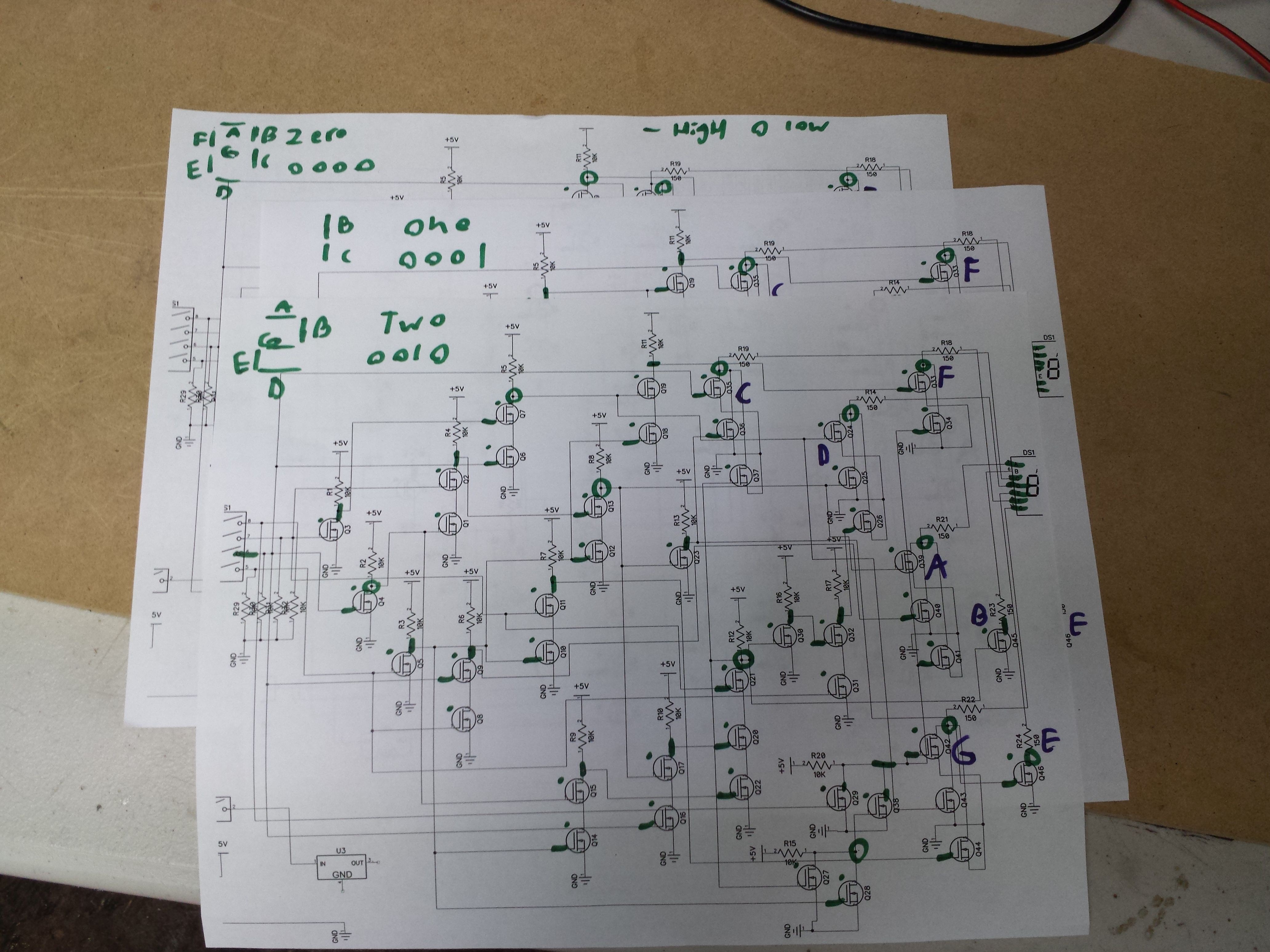

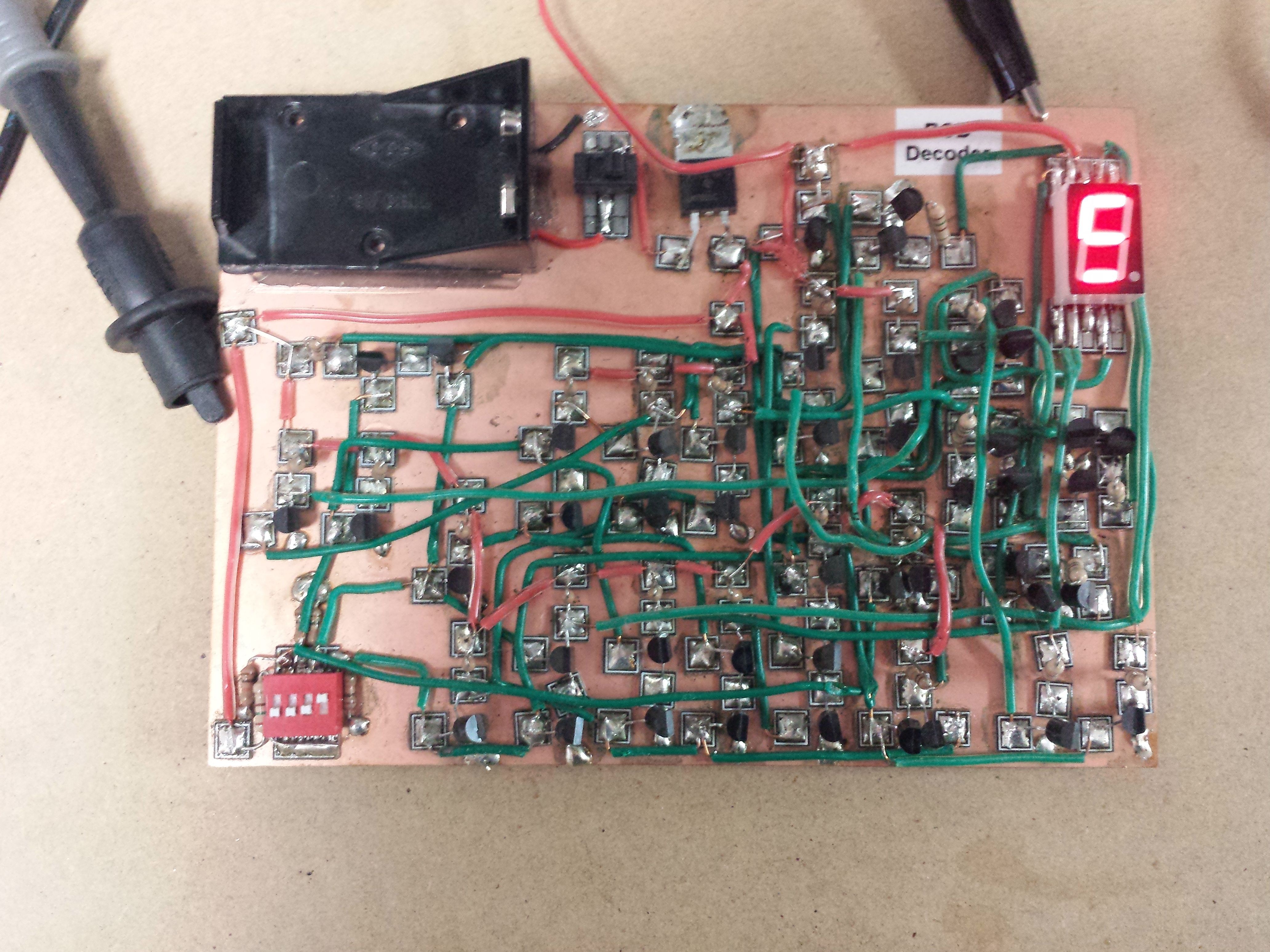

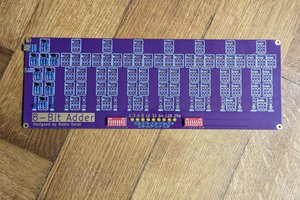

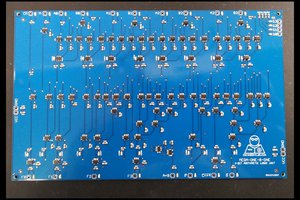

Building this was a real treat. I had long since reached the point where nearly every kit was far to simple and it was fun to get back into the action so to speak. V1 never worked and V2 worked with some modifications. I eneded up using 8 diodes, 31 resistors, and 39 Transistors.

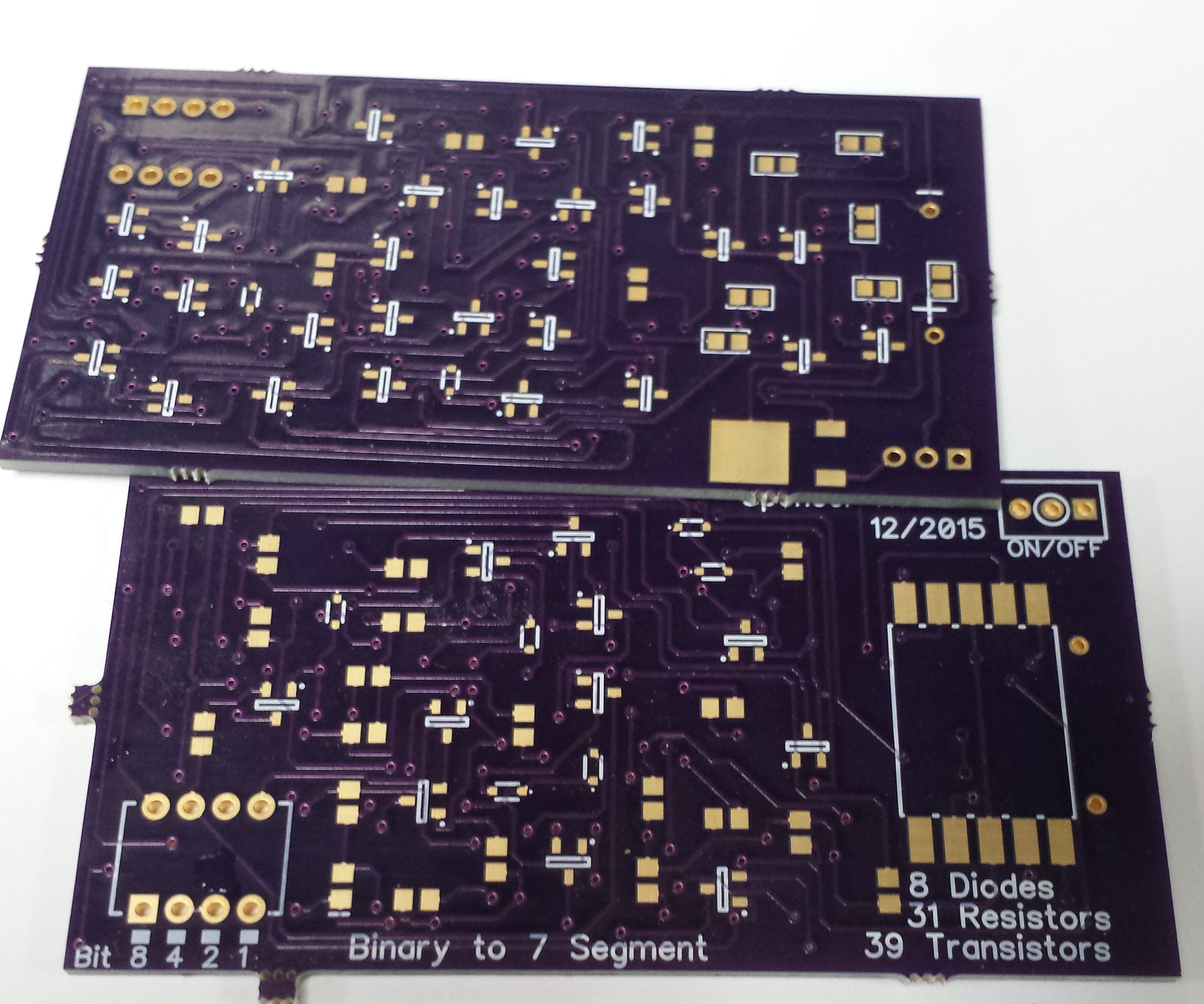

All the relevant files are on git hub including an excel file listing part quantity with a digikey link. The PCB is about 5 square inches and they have been corrected and will now work with out modification. I bought mine from OSH park and it was about 30$ with shiping.

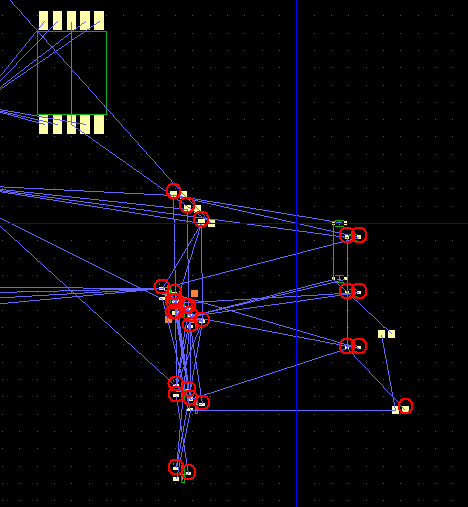

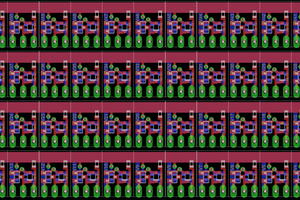

I used Diptrace for design however I proved a bit map image of the PCB for those who don't want to install it. The design comes in under 300 pins meaning it will work with the free version.

Spencer

Spencer

Robin Dorst

Robin Dorst

Dave's Dev Lab

Dave's Dev Lab

Yann Guidon / YGDES

Yann Guidon / YGDES

Tim

Tim

It's funny how often this subject pops up. I'm not sure why you chose the logic way instead of the diode matrix way but I'm glad you tried :-)