-

Smarter Digital Troubleshooting and Analysis

07/16/2018 at 21:54 • 1 commentAs you read digital logic diagrams to try to understand them or if you ever find yourself probing an actual piece of hardware (hard to do on an FPGA, although with built-in logic analyzers and simulators, it is possible), here's a time saving tip.

Suppose you have a 9 input AND gate. If you probe the inputs you can stop as soon as you find a zero. Any one zero on the input means the output is zero. There's no other way it can be. Or, in the case of a NAND gate, it is a one, of course. The same goes for an OR or NOR gate. If you find a single one input, you can stop looking at the rest of the inputs. You know what the output has to be.

During design, we (or the FPGA compiler) can often take advantage of "don't care" states which are usually represented as an X. For example, you might see a truth table like this:

Enable Input Output 1 0 1 1 1 0 0 X 0 You can interpret this as "when enable is 0, the output is 0 and the input doesn't factor into anything."

-

More on Negative Logic

07/16/2018 at 21:33 • 0 commentsIn the main portion of the bootcamp, I mentioned that taking the OR of two active low signals was the same as performing an AND on them. In other words, if you have two door sensors that go low when the corresponding door is open, and you want to know when door 1 AND door 2 is open, you can do one of two things:

- Invert the signals and take the AND. This is potentially inefficient.

- Use a NOR gate.

Of course, if you wanted the output to be also negative (that is low means true), you could use a NAND or OR gate, as well.

Just like you often see little circles on flip flop inputs to indicate negation, you sometimes see the same thing on logic symbols, as well.

![]()

For example, as in the image above, a NAND gate is sometimes drawn as an OR gate with two circles on the inputs. The gate is still a NAND gate. It is simply communicating that the inputs coming in are active low. You might even see a OR gate with two circles on the input and one on the output (which is really an AND gate).

With the advent of computer drawing tools, you don't see this as much as you used to, but you will see it on occasion. It really does help if you are trying to understand what's going on while reading a logic schematic.

-

Acknowledgment

07/16/2018 at 21:04 • 0 commentsThis bootcamp relies heavily on the excellent Falstad simulator. Many -- but not all -- of the examples are straight from the simulator's circuits menu or modified from that source.

You should know that the simulator doesn't do just digital electronics. In fact, that's probably the least of its capabilities. It also can model DC, AC, and even RF circuits.

While it won't help you in the FPGA world, if you wondered how things like NAND, OR, and XOR gates are actually built from devices, it is worth checking out the Falstad Circuits menu under logic families. TTL and CMOS are the most useful to look at and you'll see how fundamental gates are made from basic devices. You don't need to do this to progress through this bootcamp, but if you are interested and have a good grounding in transistors (no pun intended), it is a fun detour.

-

Logic Minimization

07/16/2018 at 20:59 • 0 commentsIf you are here for a refresher on digital logic, you might have had a traditional class sometime in the past. It might surprise you that we haven't talked about Karnough maps (K-maps) or Quine McCluskey diagrams. It turns out that since we are preparing for FPGAs, these things aren't so important. To understand why, you have to look back at the history of digital electronics.

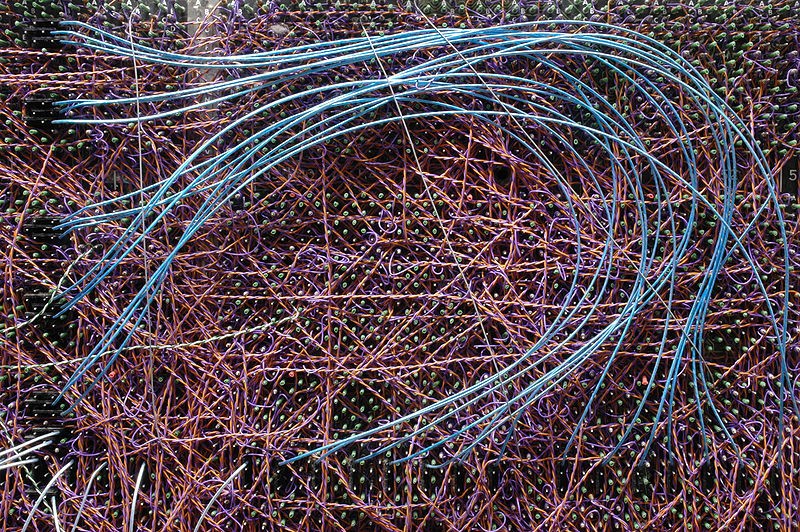

Early logic circuits used relays, tubes, and transistors to build logic circuits. It is true that you could custom build anything you wanted, but smart designers realized that wasn't efficient so instead they would make a card with a few gates on it. For example, I might make a card with 6 two-input NOR gates on it. Then I would have a backplane full of cards. My goal, then, was to figure out how to make everything out of two-input NOR gates. That led to things like this Digital Equipment Corporation backplane:

![]()

(Photo credit: Dave Fisher Creative Commons Attribution-Share Alike 3.0)

Later, you could get ICs that had different kind of gates to them. Now optimizing to one kind of gate wasn't as important as minimizing down to the least number of packages. With FPGA design, you actually have gone back to the old days. There's generally just a few types of circuits available on the FPGA. There's just lots of them. But instead of a backplane, the connections are made with some sort of configuration memory. The circuits, though, are usually much more complex than just a NOR gate.

Luckily, the HDL compilers will handle all of that for us. We can describe what we want and -- mostly -- you don't have to be very concise or efficient. Well, at least until you do have to. There are certain "bad practices" we'll talk about in future bootcamps that can lead to bad FPGA designs. But for the most part you can describe what you want even in a very high-level way and the compiler will figure out how to make the virtual spaghetti backplane you need.

-

Glossary

07/13/2018 at 22:31 • 0 comments- AND Gate - A gate who's output is 1 only when all inputs are 1.

- Combinatorial Logic - Logic that does not rely on the previous state of the system to set the current output state.

- Exclusive OR Gate - See XOR Gate.

- Flip Flop - A circuit element that can take one of two states (1 or 0) and remember it until changed. Somewhat like a one-bit memory device.

- Inverter - See NOT Gate.

- Logic Diagram - See Schematic.

- NOT Gate - A gate that takes a single input and inverts it. That is, a 1 becomes a 0 and a 0 becomes a 1.

- OR Gate - A gate who's output is a 1 if any inputs are 1.

- Schematic - A diagram of a logic circuit made up, usually, of logic symbols for fundamental gates.

- Sequential Logic - Logic that typically uses flip flops and the current output state influences future output states.

- Truth Table - A table showing a logic circuit's possible inputs and the outputs that will result.

- XOR Gate - Exclusive OR gate. A two-input gate that sets its output to 1 if either input is a 1, but not when both inputs are a 1.

Logic Truth Tables for Two-Input Gates

A B AND OR XOR 0 0 0 0 0 0 1 0 1 1 1 0 0 1 1 1 1 1 1 0

FPGA Bootcamp #0

If you need a refresher for digital logic before tackling FPGAs, this is the bootcamp for you!

Al Williams

Al Williams