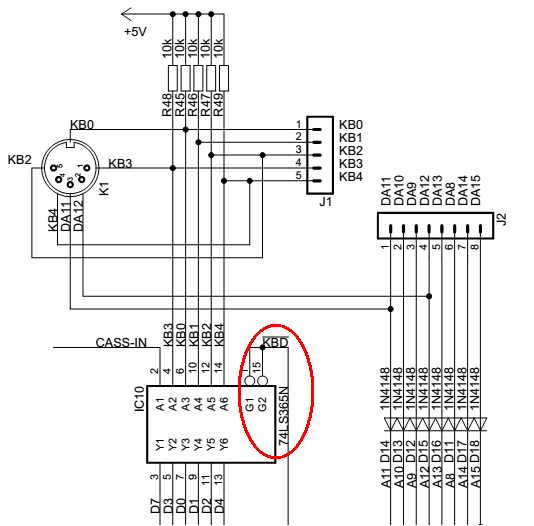

The ZX machines read the matrix keyboard by lowering 1 out of 8 upper address lines (A8..A15) and then read 5 bits of data in lines D0..D4 (as D5..D7 serve for other purposes).

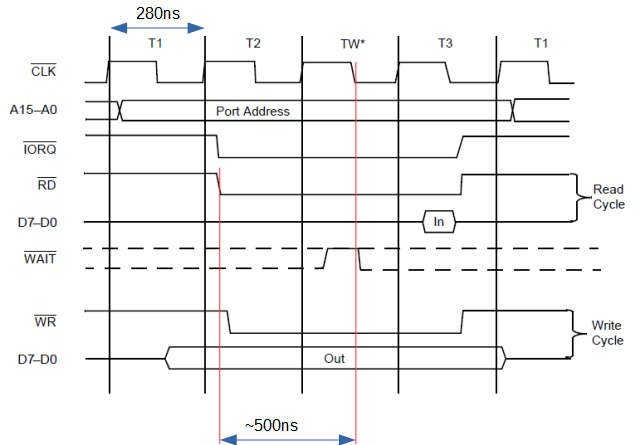

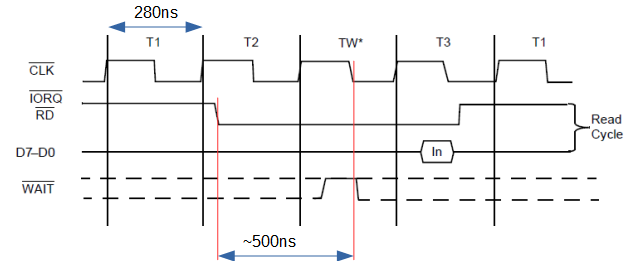

According to the Z80 manual during an I/O read cycle the time spent from the fall of /IORQ to the middle of T3 state (when the CPU effectively samples the signal) is a bit less than 2.5 CPU cycles or something close to 680ns (for 3.579MHz clock) which is a challenge for the AVR to respond.

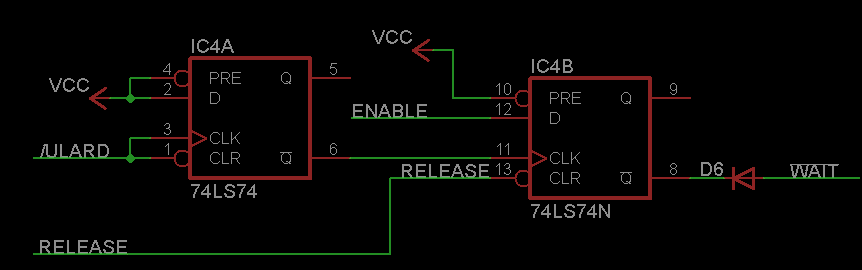

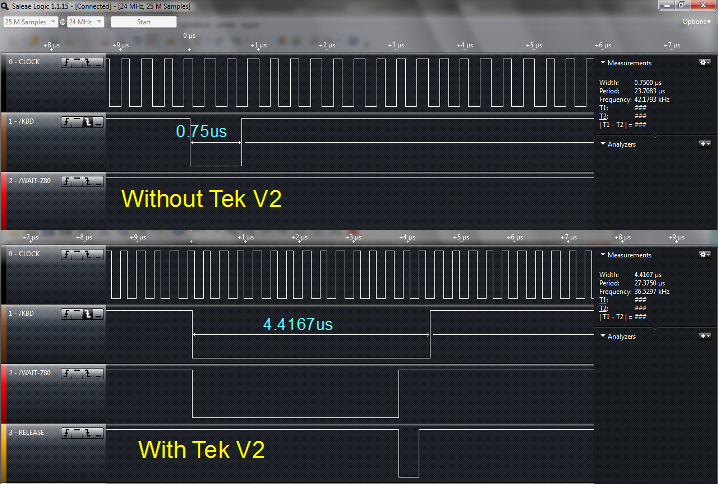

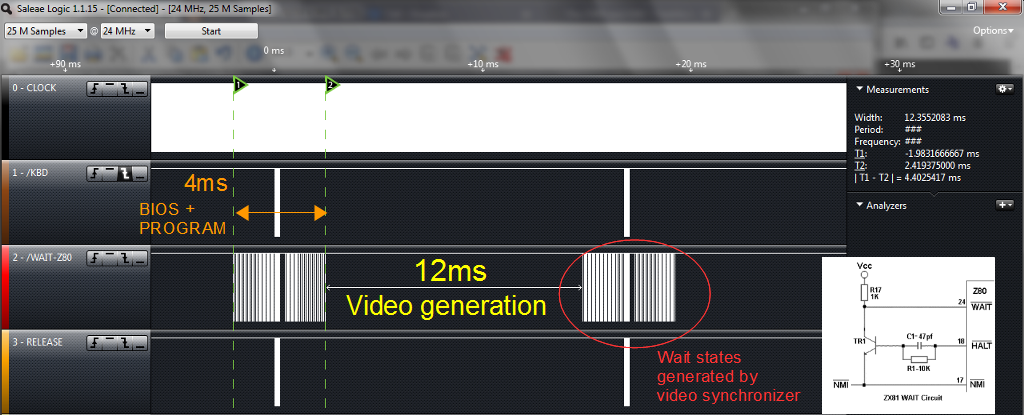

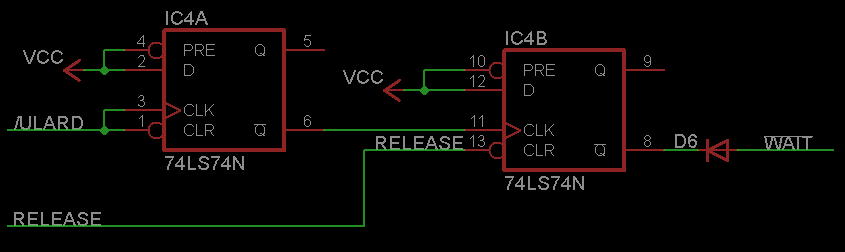

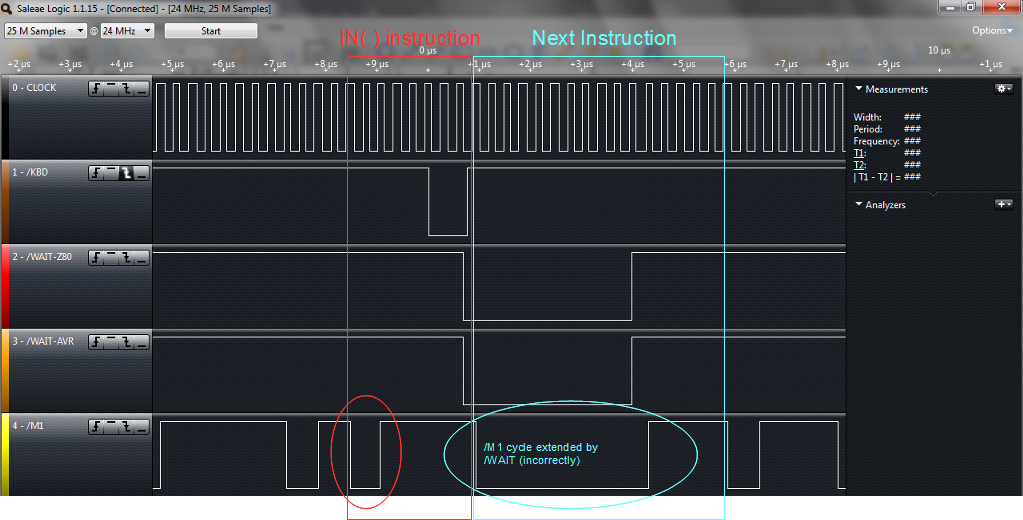

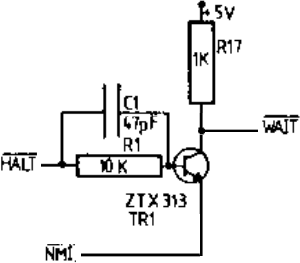

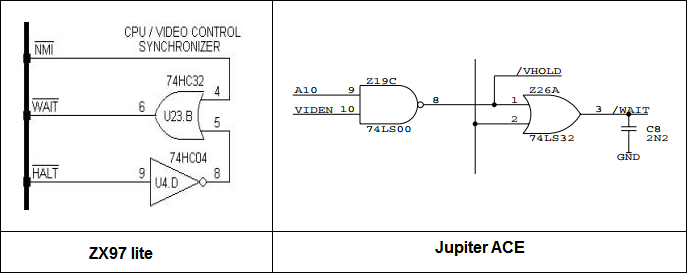

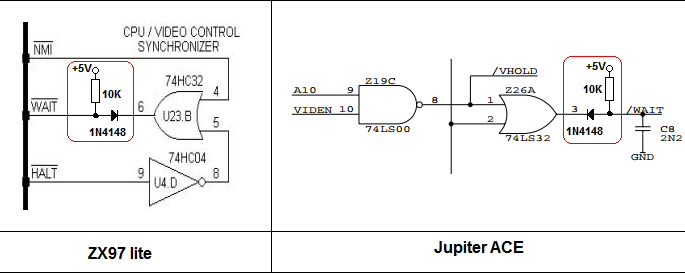

At the time the Z80 was created the designers knew that peripherals might take too much time to respond and provided a signal to pause the CPU while waiting for the external peripheral to respond. Such signal, named WAIT (really?!) is sampled between an internal WAIT state generated by the CPU between cycles T2 and T3, which occurs at around 500ns after the /IORQ signal go down.

Well, 680ns might not be enough for an AVR to enter and IRQ, sample the Z80 and respond with data, but 500ns is more than adequate to activate the WAIT line and then do wherever necessary and then release the Z80 from its idleness.

danjovic

danjovic

deʃhipu

deʃhipu

Dan Julio

Dan Julio

Rue Mohr

Rue Mohr