This is a joke, right?

Not at all. 1 bit processors have existed for a long time.

But with 1 bit you get two instructions, what can you do with that?

The data path is 1 bit, but the instruction width is wider. With 4 bits you get 16 instructions. When combined with an address operand, the program store width can be 4, 8, or other numbers. As you will see the design is very flexible.

But then you can only operate on 1 bit of data, surely that's not very useful?

With addressing you can have multiple locations for the data, including multiple input and output ports, and scratchpad locations.

What is it good for?

It's typically used for control applications. It reads 1 bit inputs, uses boolean operators to make decisions based on those in conjunction with stored state, and writes 1 bit outputs. An example might be a traffic light controller for an intersection.

Why not use a microcontroller?

Indeed one would use one these days. However back in its day, this offered a design paradigm based on Ladder Logic. Another advantage was the wide range of supply voltage possible in the CMOS implementation which gave large noise immunity.

So you designed this?

I seldom do anything original. This is based on the Motorola MC14500B Industrial Controller Unit chip. The best reference for this controller is the 1977 handbook among several locations at archive.org

On Hackaday @agp.cooper has already done projects on 1 bit CPUs including an examination of the MC14500B, and there is a WDR 1 bit computer project based on this chip so I'm treading a well-worn path.

In the links section you will find pointers to resources. Naturally there are assemblers, simulators, and even replicas implemented in FPGAs. There was a reimplementation as recent as 2019.

If you find any more resources of interest do tell me and I'll add a link if it's worthy.

You can still buy MC14500B chips on eBay but I don't see the point of getting something you could emulate in a 10¢ MCU, unless one is a collector, or you must have an exact workalike for existing equipment.

At this point I revert to standard exposition mode.

Goal

To understand this unique architecture. Steps:

- Simulate a MC14500B system in software

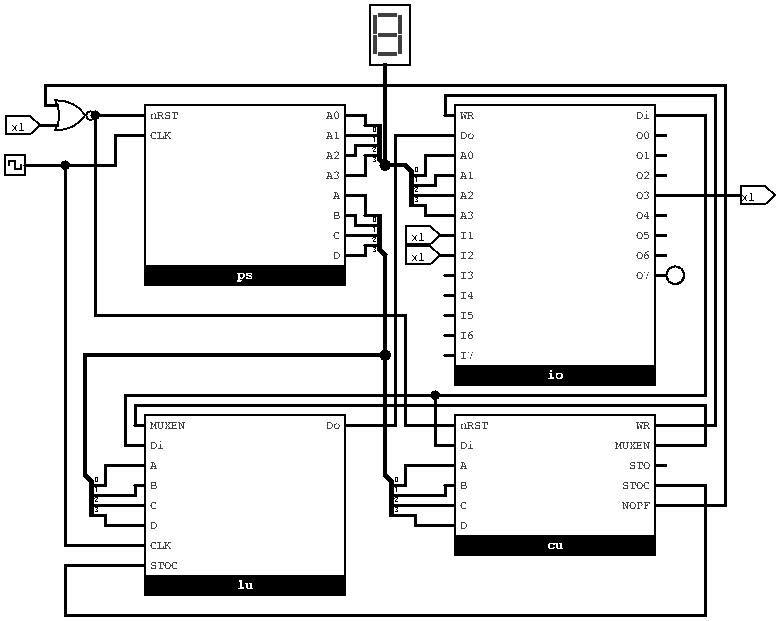

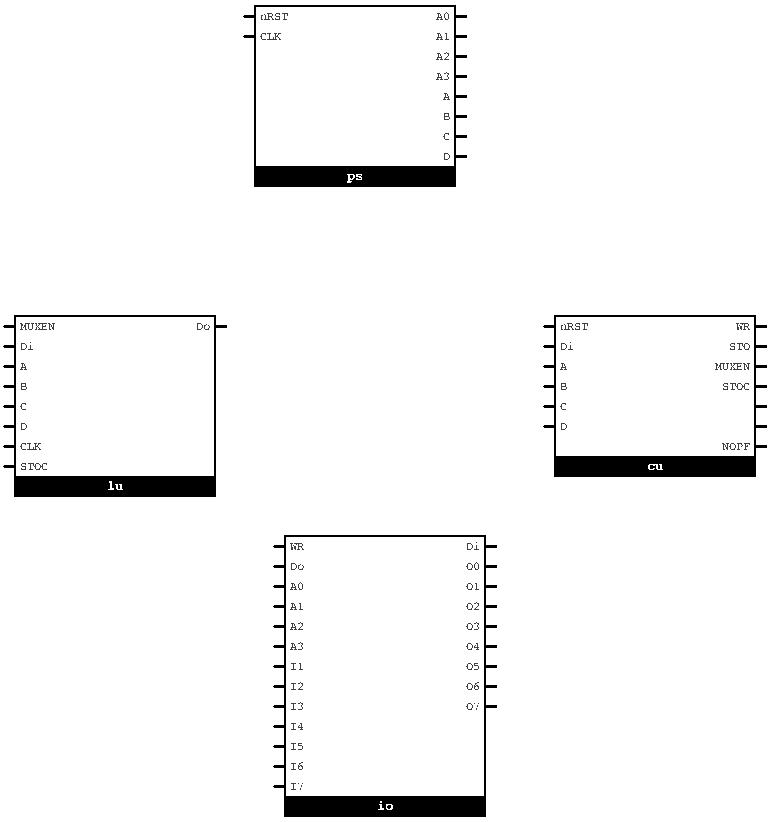

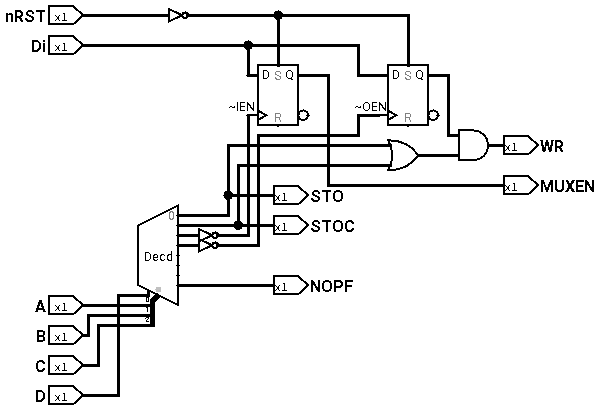

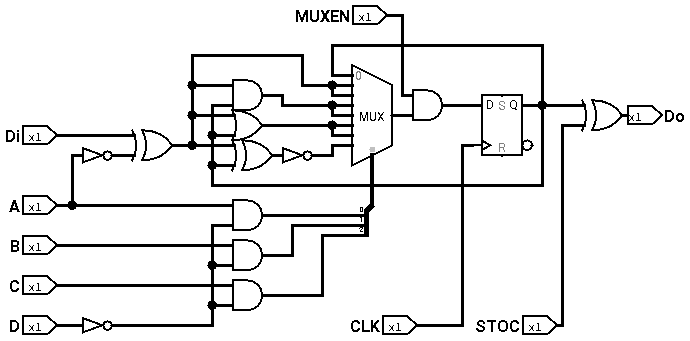

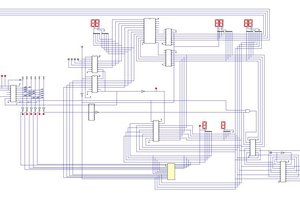

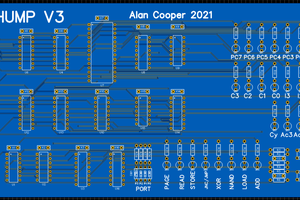

- Design a discrete workalike in Logisim

- If feasible and I still feel like it, implement with TTL chips from my junk box

Note that there may be cycles of this for version 1, 2, etc.

Architecture

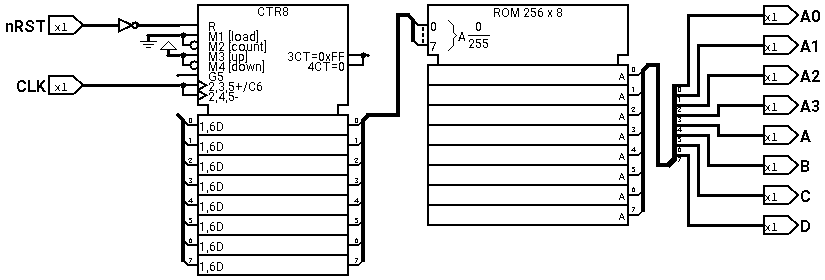

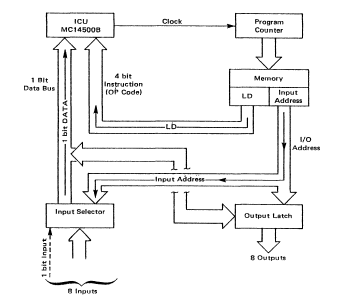

Unlike microcontrollers, the MC14500B is not a complete controller. It doesn't even have a program counter on-chip, that has to be implemented externally. Think of it as the nucleus of a controller. That's why it's labelled an ICU, which stands for Industrial Control Unit, not the ICU in a hospital which I hope you never have to visit. It runs relatively slowly, at up to 1MHz but this is sufficient for the uses it's put to.

Note that my goal is to simulate a system, not the chip. By not making a workalike for the MC14500B, but a typical system, the design can be less constrained because some design choices have been set. Some less used instructions such as JMP, RTN and SKPZ could be omitted in the design.

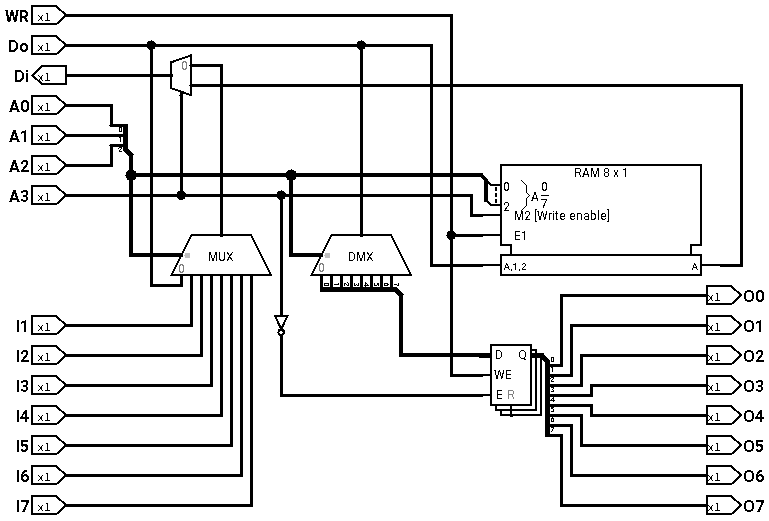

One design choice is the program store (PS). The handbook talks about different design choices for the PS width. You can have 4 bit interleaved instructions and operands (with the clever use of the 2 phase clock for the LSB). Since most memory widths are multiples of 8 bits these days, a 8 bit PS width would be more natural. However this limits the operands to 4 bits with which you can address only 16 input and 16 output ports. Some of those ports are given over to scratchpad locations so typically 8 ports input and output, and 8 scratchpad locations. An expansion would use another byte to expand the space to 4096 locations. That's not hard to do in software, but I'm not sure I want to build hardware implementations, we'll see.

Version 1 simulation results

The logs detail the process and results of simulating a candidate implementation...

Read more » Ken Yap

Ken Yap

Yann Guidon / YGDES

Yann Guidon / YGDES

agp.cooper

agp.cooper

Hi Ken,

Which version of LogiSim are you using? I has just started using LogiSim for my CPUs.

I have looked at the LogiSim 2.7.1, LogiSim 2.7.10 and LogiSim Evolution.

Regards Alan X