For now, updates are only being made to the github repository.

https://github.com/edson-acordi/4bit-microcomputer

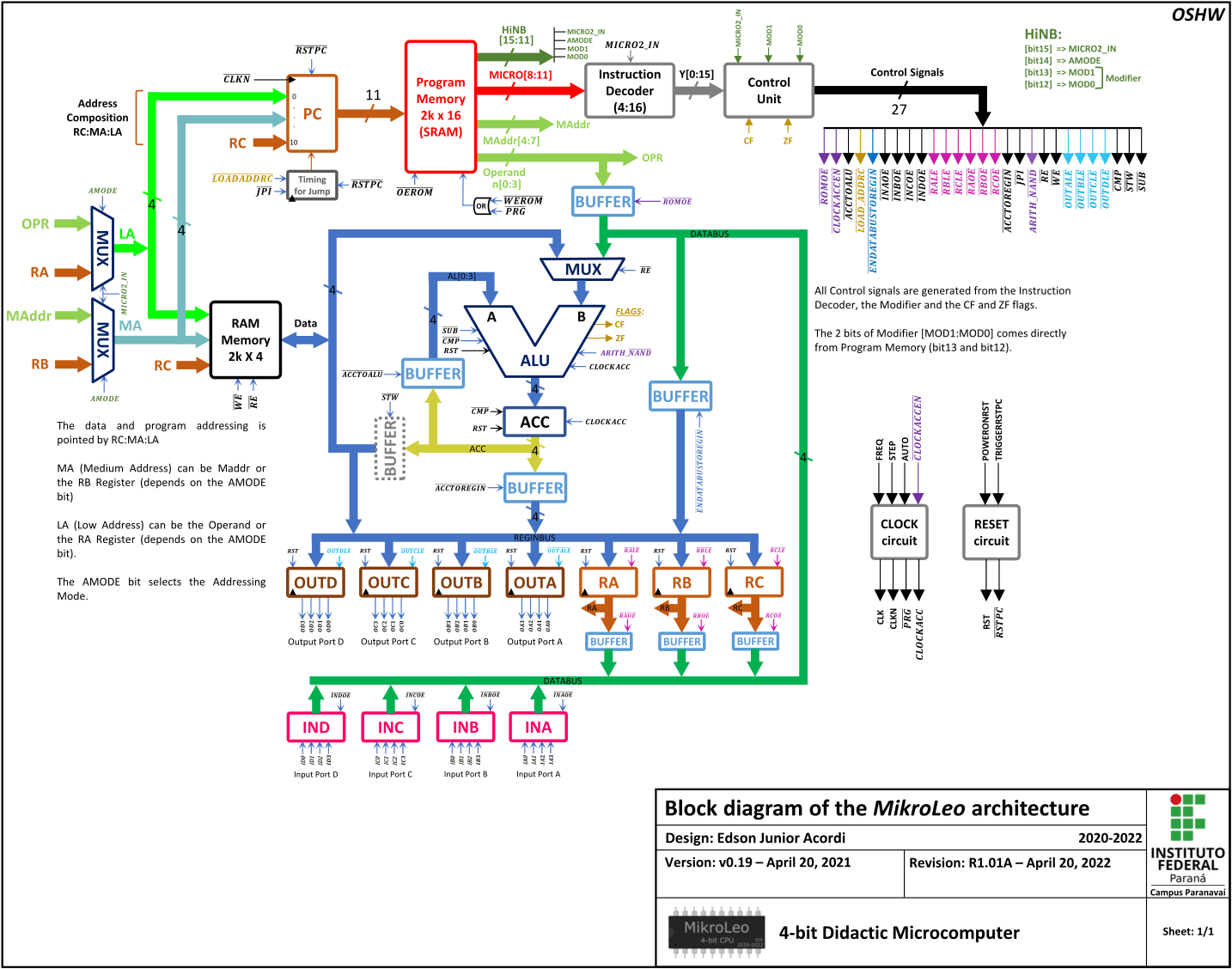

Main Features:

- Implements a 4 bit CPU

- 2k x 16 Program Memory (up to 4k)

- 2k x 4 RAM (up to 4k)

- 4 Output Ports (16 outputs)

- 4 Input Ports (16 inputs)

- Single Cycle Instruction/RISC

- Harvard Architecture

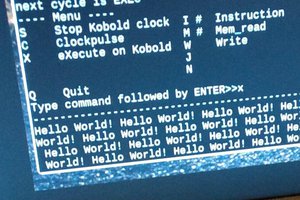

- 3 execution modes:

- step by step

- 3MHz (precise time base)

- adjustable clock speed ( ≈ 1 Hz - 200 Hz)

- No MPU/MCU or complex chips

- No microcode

- Indirect addressing to facilitate the implementation of subroutines

- Program memory implemented with RAM to easy programming

- It accepts 300 and 600 mils memories (for those with old DIP versions)

- Supercapacitor or battery to keep the program in RAM (for low power version)

- It can be manually programmed by switches or via Arduino/Esp32

- Built with 74HCTxxx integrated circuits for low power consumption and compatibility with TTL circuits

- All parts are through-hole for easy assembly

- All control signals, registers and the program counter are available through the pin header connectors

- Dual layer Single board with 295.9mm x 196.9mm

MikroLeo Architecture

Note that some buffers are used to allow viewing the contents of registers at any time, since this project is mainly intended for educational purposes.

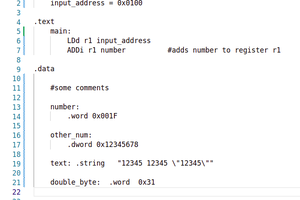

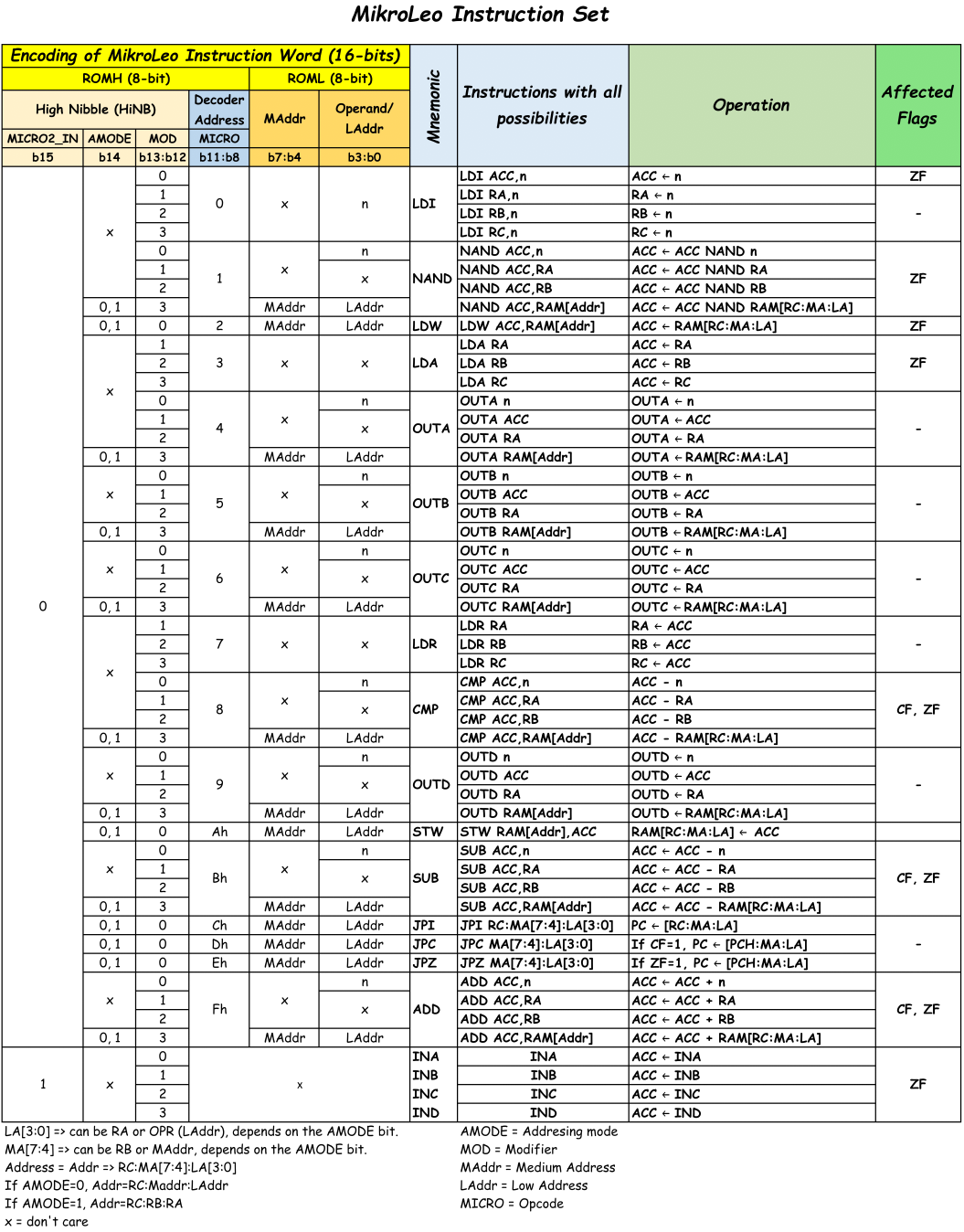

The MikroLeo Instruction Set

Although MikroLeo has only 20 instructions, using the AMODE bit (b14) and the modifier bits (b13:b12), it is possible to encode 64 combinations of instructions, as can be seen below.

Instruction Set explanation and examples

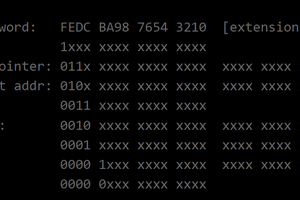

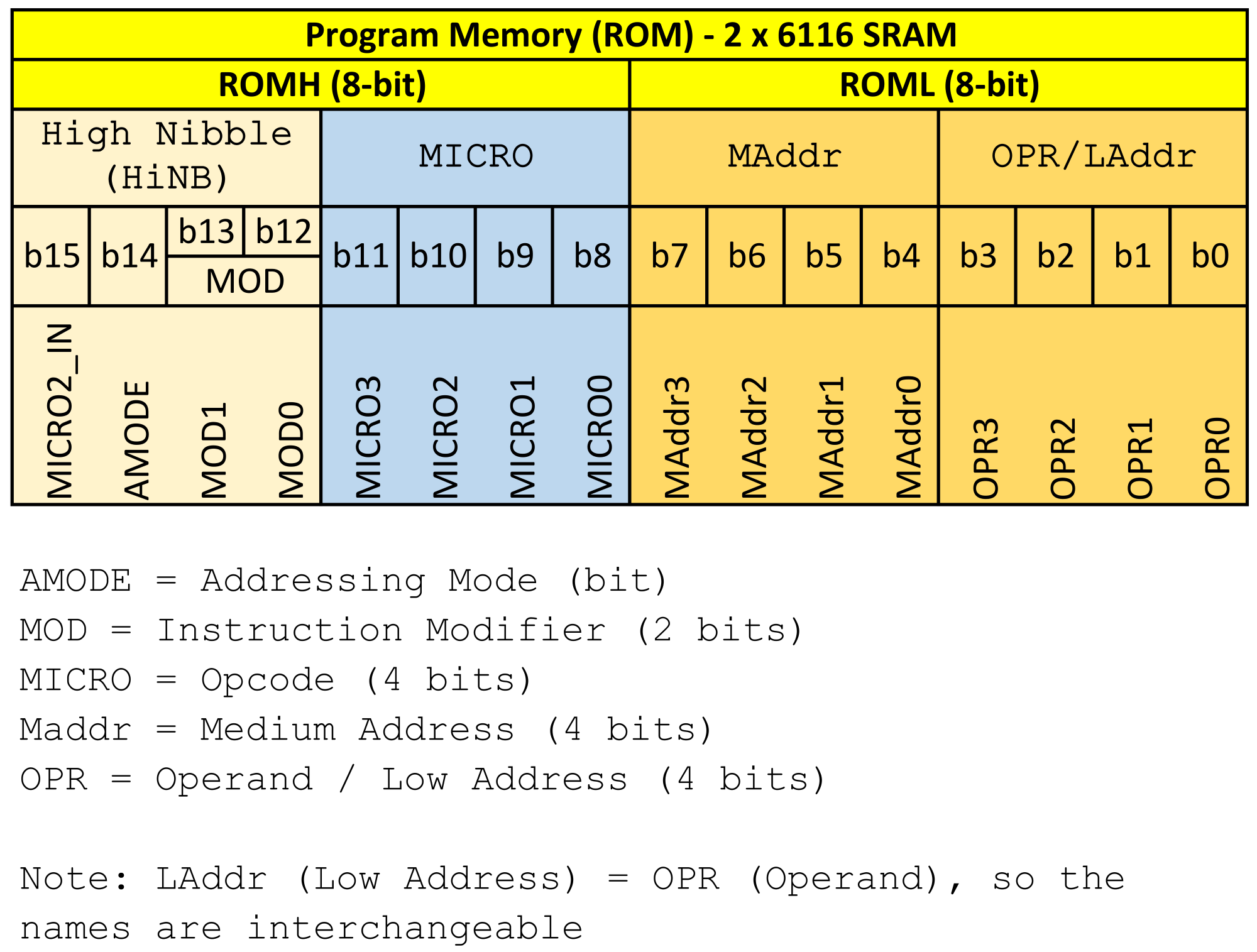

In binary, the Instruction Word is coded as,

ROMH (Most significant byte of program memory)

| b15 | b14 | b13 | b12 | b11 | b10 | b9 | b8 |

|---|---|---|---|---|---|---|---|

| MICRO2_IN | AMODE | MOD1 | MOD0 | MICRO3 | MICRO2 | MICRO1 | MICRO0 |

ROML (Least significant byte of program memory)

| b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 |

|---|---|---|---|---|---|---|---|

| MAddr3 | MAddr2 | MAddr1 | MAddr0 | Operand3 | Operand2 | Operand1 | Operand0 |

- Note: b15 = bit15 ... b0 = bit0

LDI - Load with Immediate

Description: Loads the operand value into a register.

Registers: ACC, RA, RB or RC

Operation: Register <─ Operand

| Instruction Word | ROMH | Instruction | Affected Flags |

| 0x00xn | 0x00 | LDI ACC,n | ZF |

| 0x10xn | 0x10 | LDI RA,n | - |

| 0x20xn | 0x20 | LDI RB,n | - |

| 0x30xn | 0x30 | LDI RC,n | - |

Examples,

| Instruction Word | Instruction | Comment |

| 0x0005 | LDI ACC,5 | Load ACC with operand |

| 0x1006 | LDI RA,6 | Load RA with operand |

| 0x2007 | LDI RB,7 | Load RB with operand |

| 0x300a | LDI RC,10 | Load ACC with operand |

The Instruction Word, for example, for LDI RA,6 is coded as,

0x1006 ┆┆┆└──> Least significant Nibble => Operand[b3:b0] = 6 ┆┆└───> Second Nibble => MAddr[b7:b4] = 0 ┆└────> Third Nibble => MICRO[b11:b8] = 0 └─────> Most significant Nibble => HiNB[b15:b12] = 1

Also, the instruction word (in binary) to be manually programmed into MikroLeo using physical switches is,

0001 0000 0000 0110 ┆ ┆ ┆ └─> Operand = 6 ┆ ┆ └──────> MAddr = 0 (For this instruction, it doesn't matter) ┆ └───────────> MICRO = 0 (OPCode) └────────────────> HiNB = 1 (MICRO2_IN = 0, AMODE = 0, MOD = 1)

NAND - bitwise Nand

Description: Performs the bitwise Nand operation between ACC with (Operand n, RA, RB or RAM).

The result is stored in ACC.

Operations:

ACC <─ ACC NAND Operand

ACC <─ ACC NAND Register

ACC <─ ACC NAND RAM

| Instruction Word | ROMH | Instruction | Affected Flags |

|---|---|---|---|

| 0x01xn | 0x01 | NAND ACC,n | ZF |

| 0x11x0 | 0x11 | NAND ACC,RA | ZF |

| 0x21xn | 0x21 | NAND ACC,RB | ZF |

| 0x31mn | 0x31 | NAND ACC,@RAM | ZF |

| 0x71xx | 0x71 | NAND ACC,@R | ZF |

Note:

The RAM address for @RAM is pointed by RC:MAddr:LAddr.

The RAM address for @R is pointed by RC:RB:RA.

The MAddr is represented by the letter "m".

Examples:

| Instruction Word | Instruction | Comment |

|---|---|---|

| 0x0105 | NAND ACC,5 | NAND operation between the accumulator and the operand and stores it in ACC |

| 0x1106 | NAND ACC,RA | NAND operation between the accumulator and register RA and stores it in ACC |

| 0x2107 | NAND ACC,RB | NAND operation between the accumulator and register RB and stores it in ACC |

| 0x310a | NAND ACC,@0x0a | NAND the contents of the RAM address with ACC and stores it in ACC. In this case, the RAM address = RC:0:a |

| 0x7100 | NAND ACC,@R | NAND the contents of the RAM address with ACC and stores it in... |

Pavel

Pavel