Features & Specifications

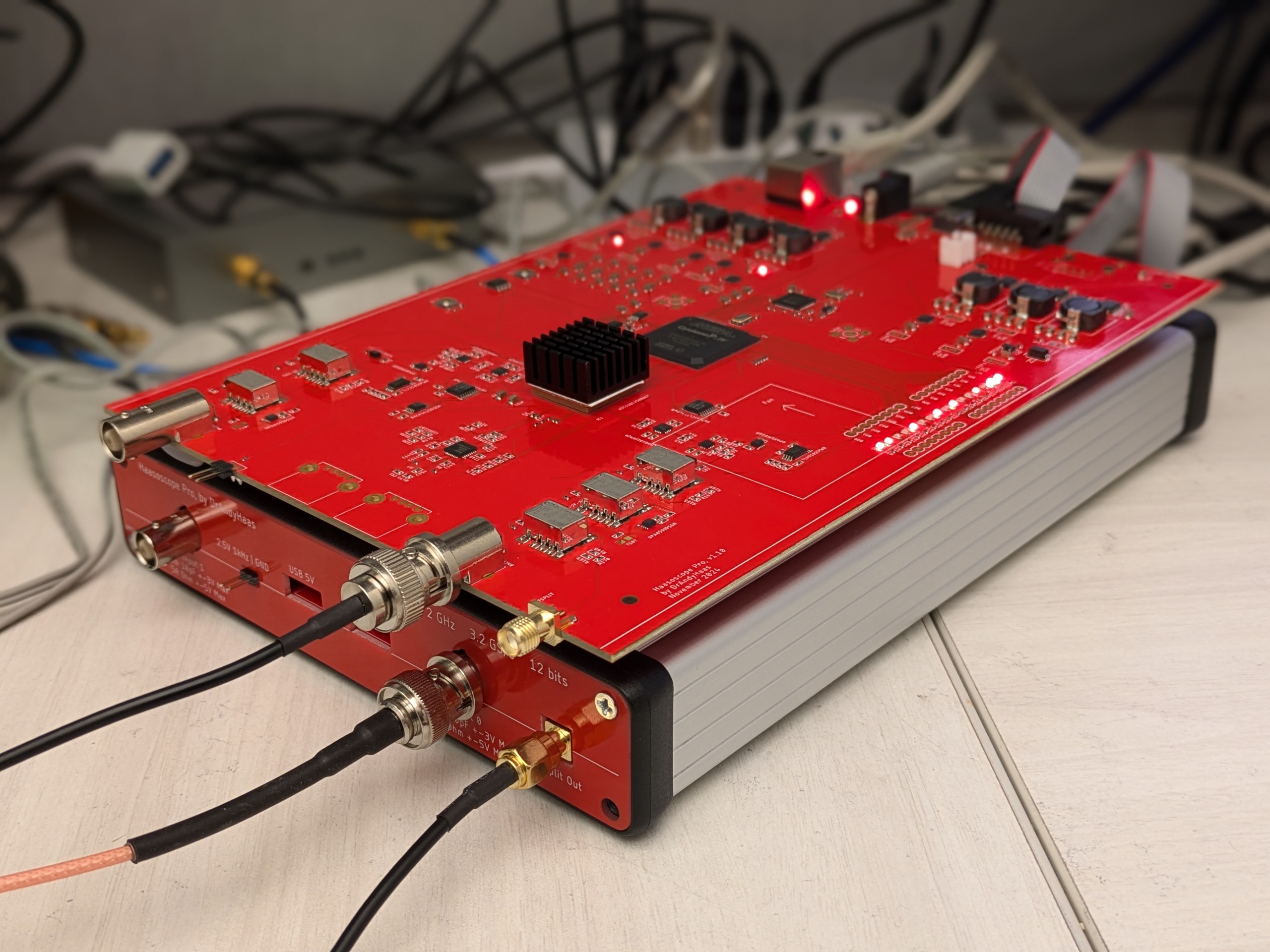

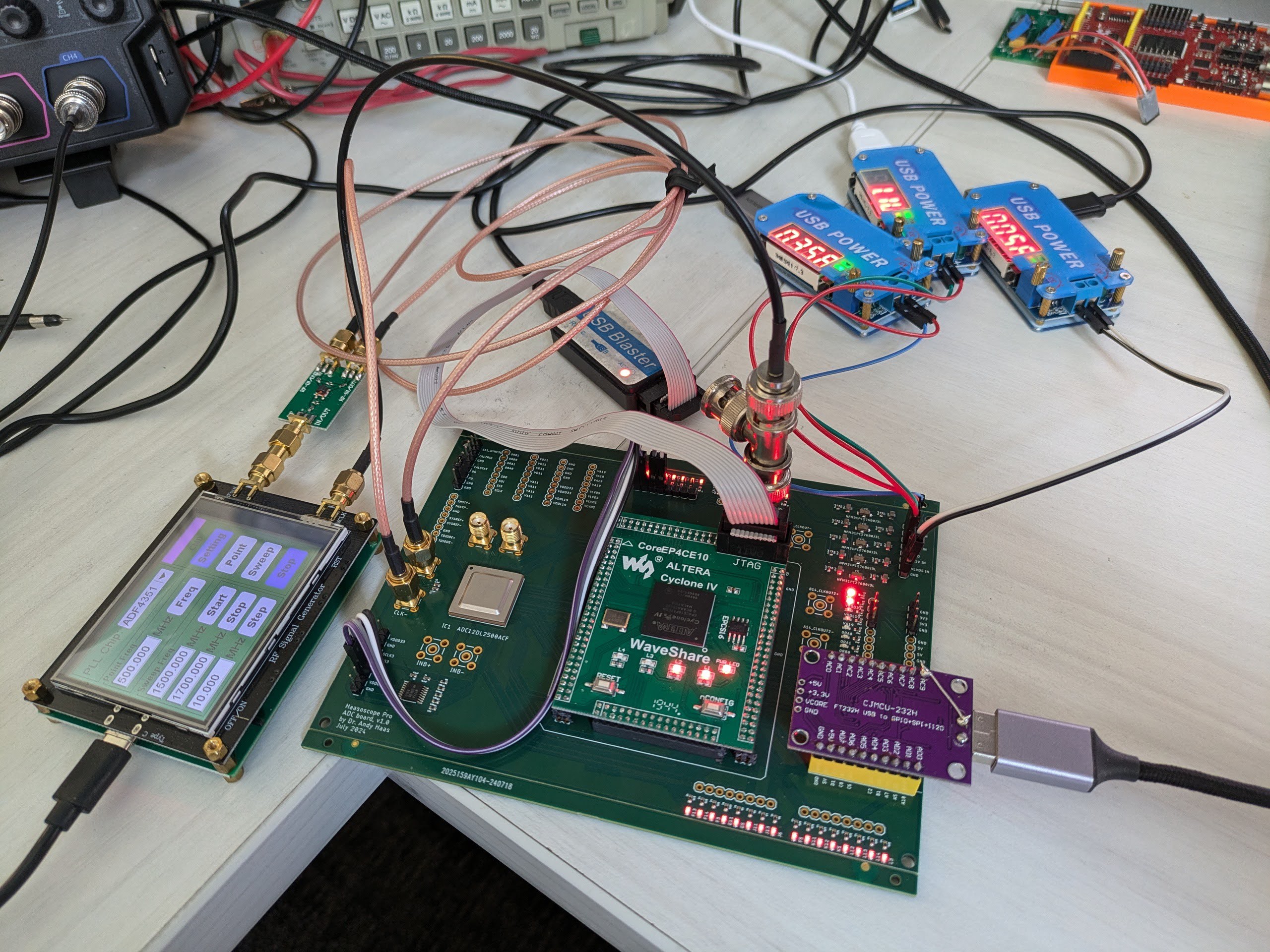

Haasoscope Pro:

- 2 analog input channels

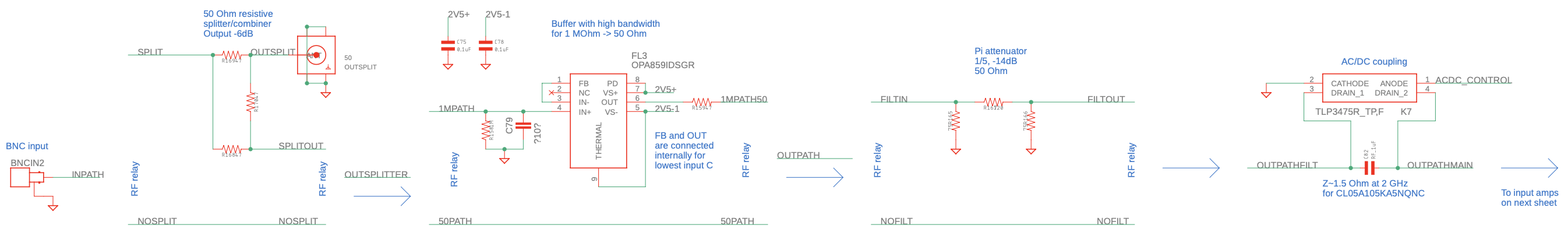

- 50 Ohm (<1 pF) or 1 MOhm (10 pF) input impedance

- 2 GHz analog bandwidth at 50 Ohm, 500 MHz at 1 MOhm

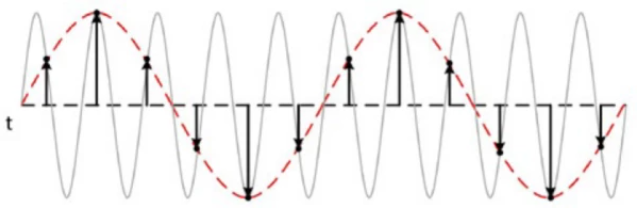

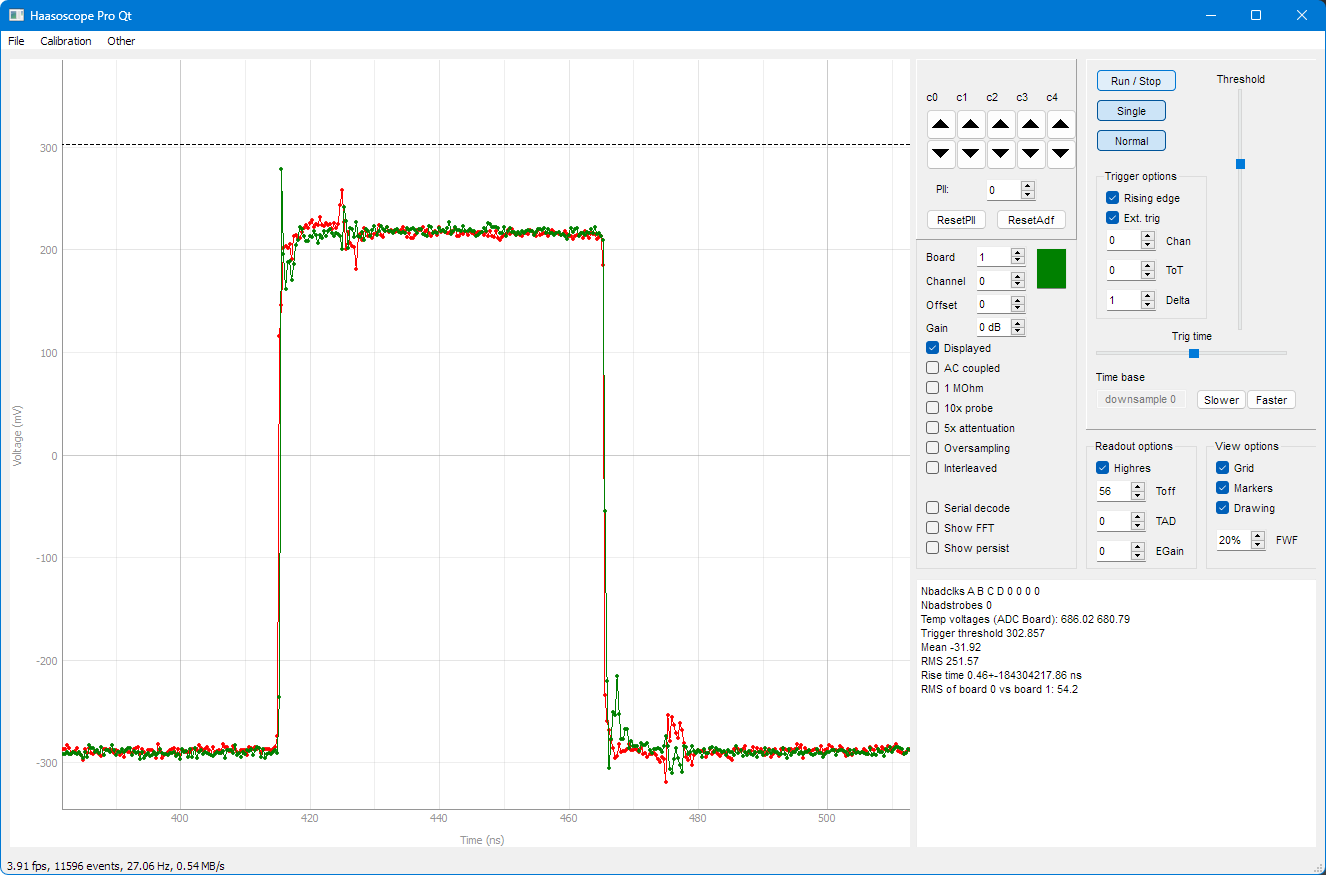

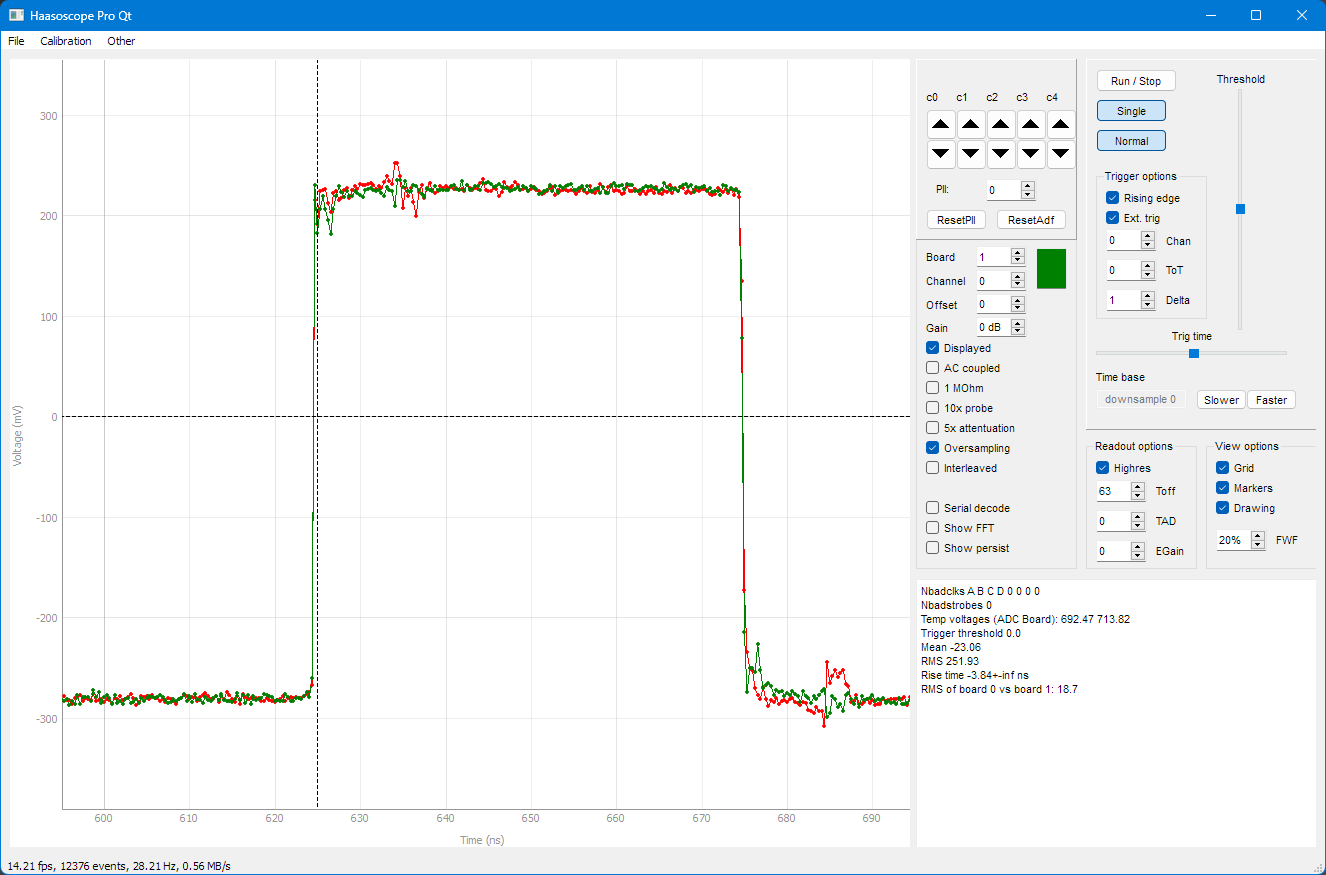

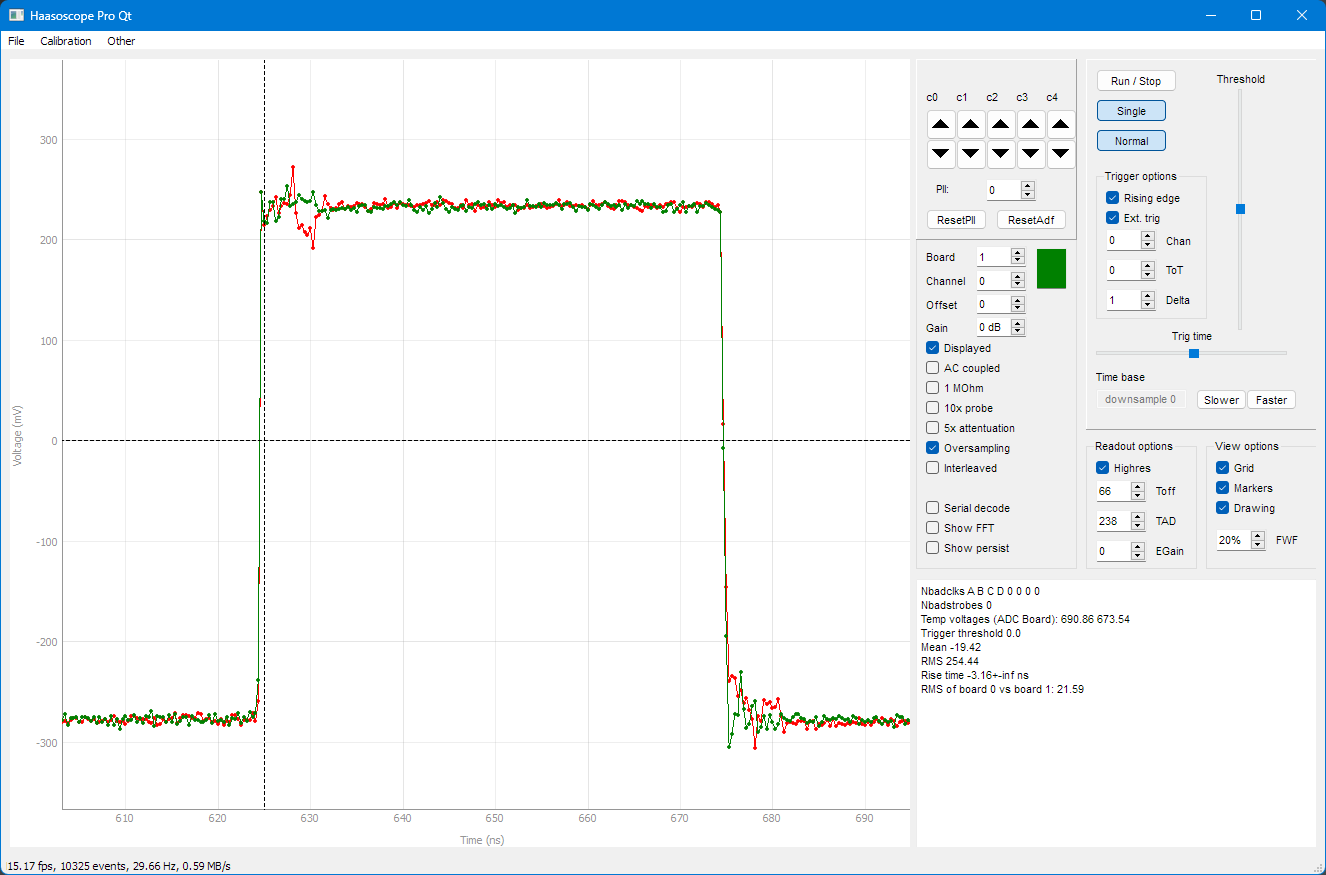

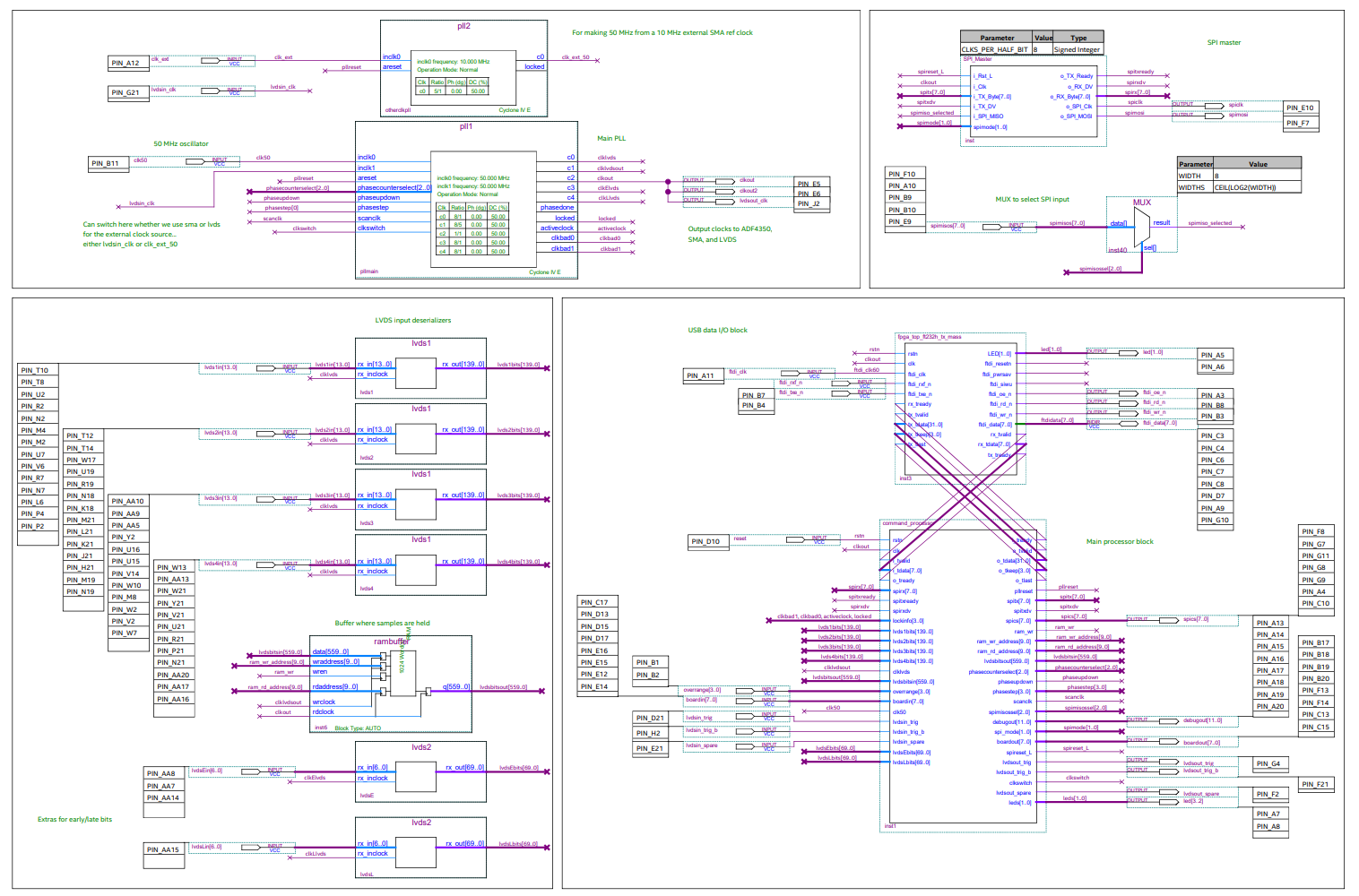

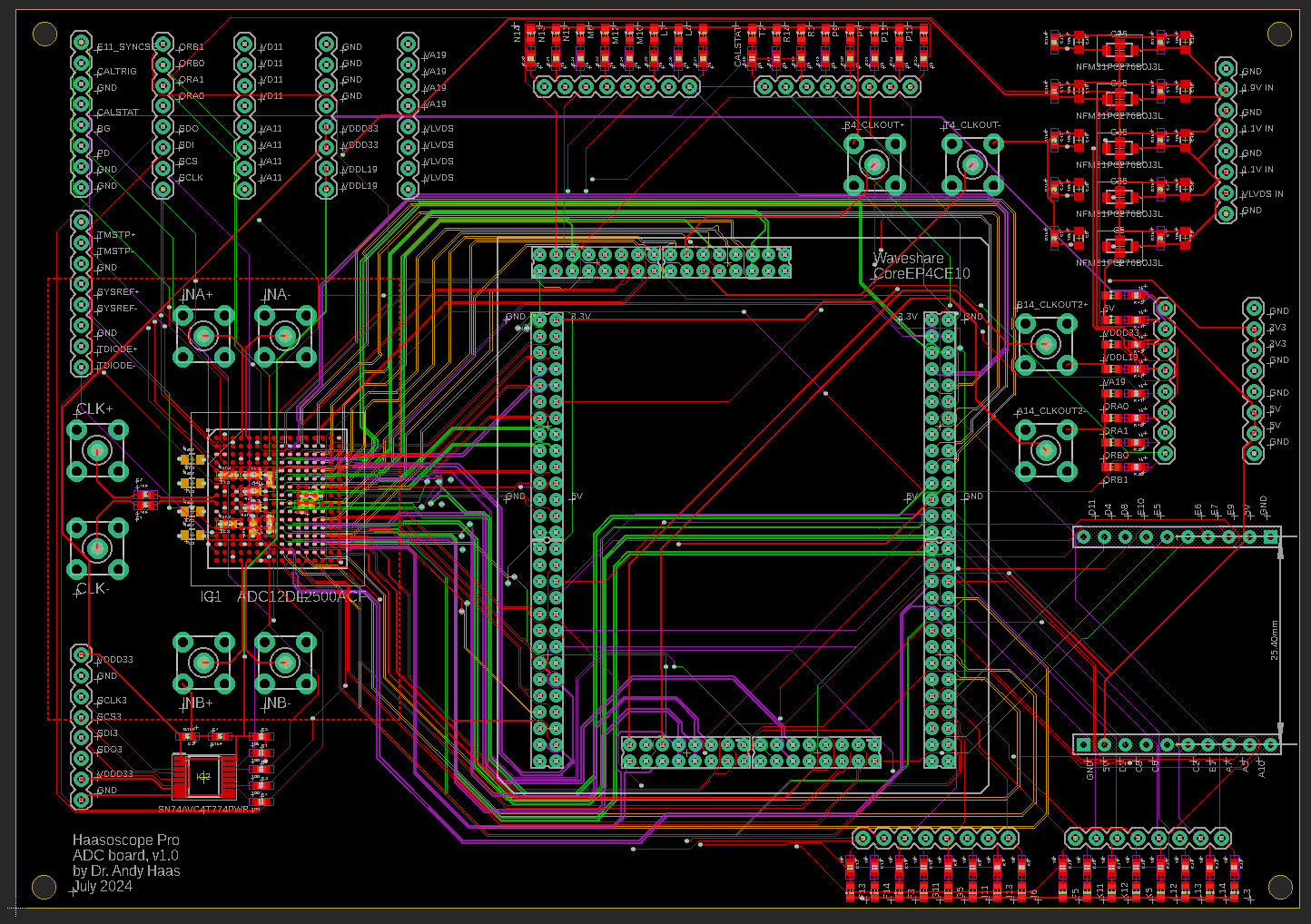

- 3.2 GS/s for 1 channel or 1.6 GS/s for 2 channels, doubled to 6.4 GS/s with two synced Haasoscope Pro's

- 12 bits of real-time vertical resolution per sample

- Up to 40k samples per trigger, with adjustable trigger time offset

- 100 ps/div to 24 hour/div, for 10 div

- Max analog input of +-5V (50 Ohm) or +-3V (1 MOhm), +-50V or +-30V with x10 probe

- Sensitivity of 1.6 V/div down to 8 mV/div, for 10 div, in x1 mode

- Programmable AC or DC input coupling

- Programmable DC offsets per channel

- External trigger in and aux trigger out

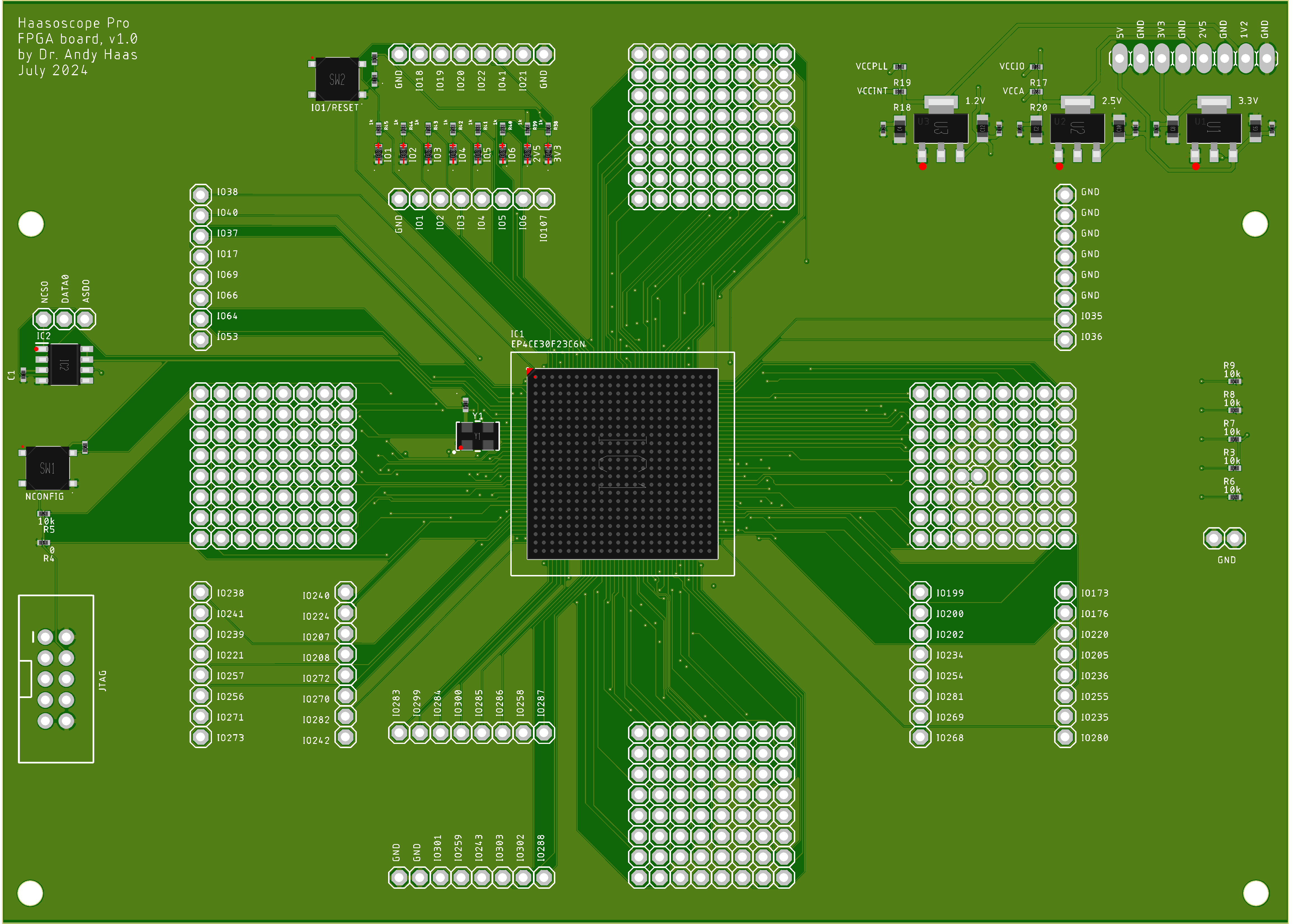

- Multiple Haasoscope Pros can be connected for more channels or to oversample at 6.4 GS/s, with synchronized timing and triggers

- Standard set of triggers (rising / falling edge, time over threshold, etc.), customizable in firmware

- Qt-based python software interface for Windows/Mac/Linux

- Standard set of signal measurements in software

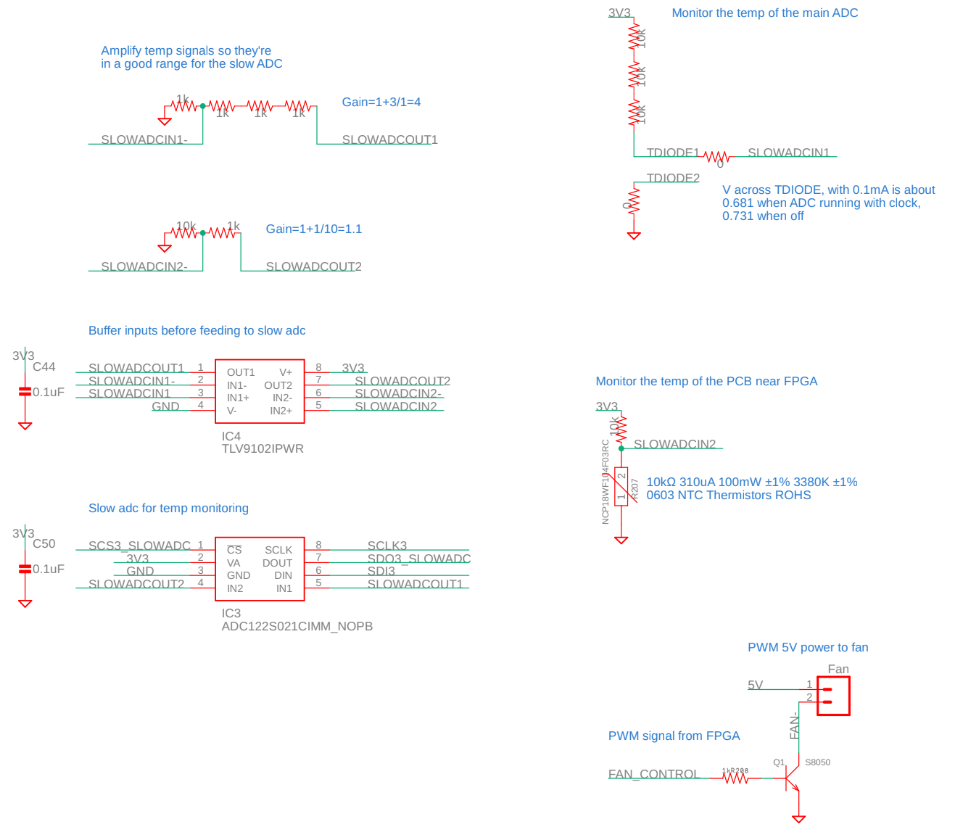

- 5 V 1.5 A USB Type-C powered (or using 12 V 1 A 2.1 mm barrel connector)

- Aluminum case with quiet 40 mm internal fan

- 220 x 165 x 35 mm (8.66 x 6.5 x 1.38 in), 0.9 kg (1.98 lbs)

Active Probe:

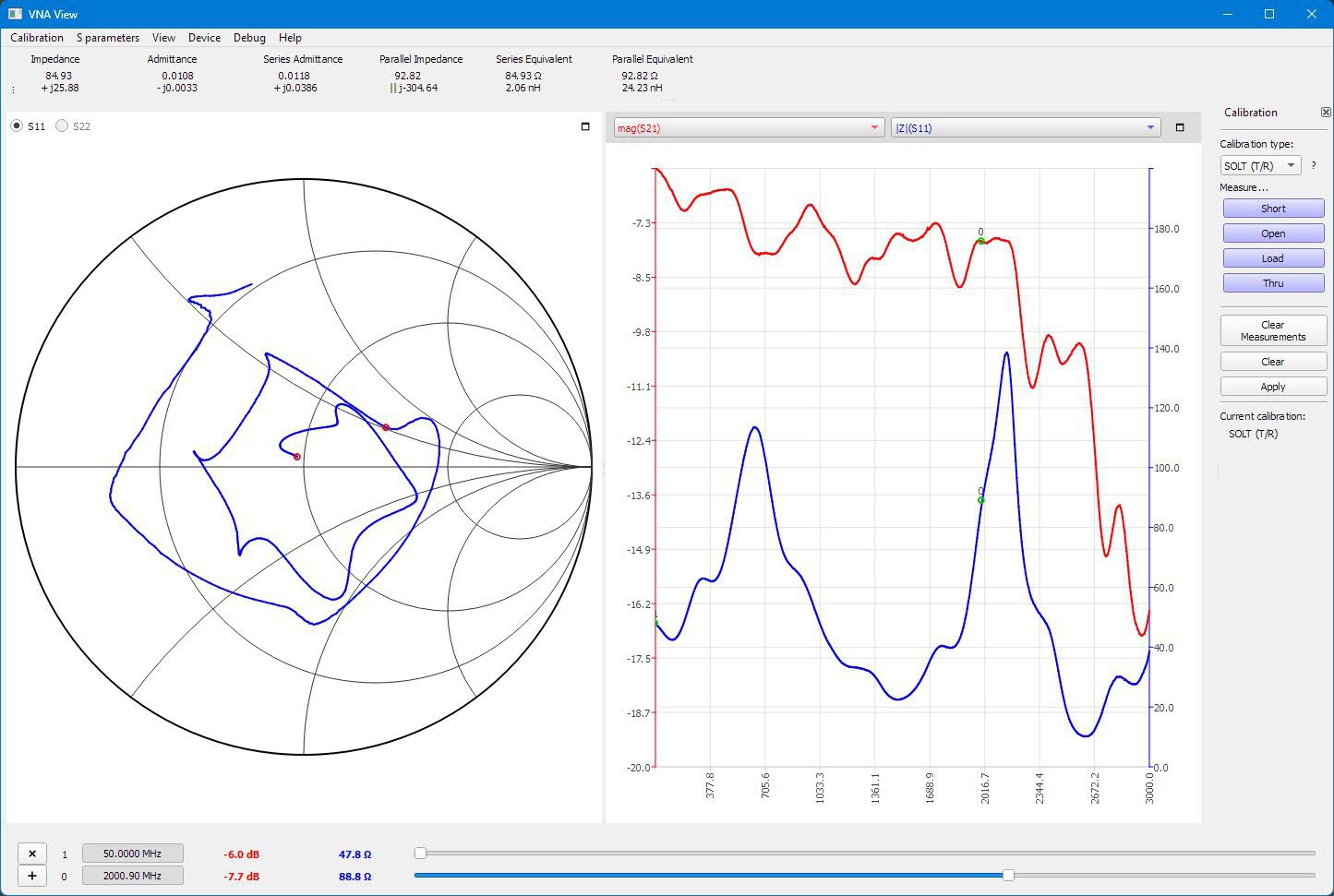

- DC - 2 GHz analog bandwidth

- Flat response from DC -1 GHz within 0.3 dB

- 1 MOhm input resistance

- 1.1 pF input capacitance

- 100 Ohm minimum impedance, near 1.6 GHz

- x10 probe attenuation, input voltage range +-30V

- 50 Ohm SMA output, 1m cable

- 12 V power at ~80 mA, via 2.1 mm barrel connector, or 5V 200 mA USB using included cable

haas

haas

Catch the YouTube Livestream with CrowdSupply next week...

https://www.youtube.com/live/iFVRcHPmOKk?si=uV00BP1ANXJQ_4-S