-

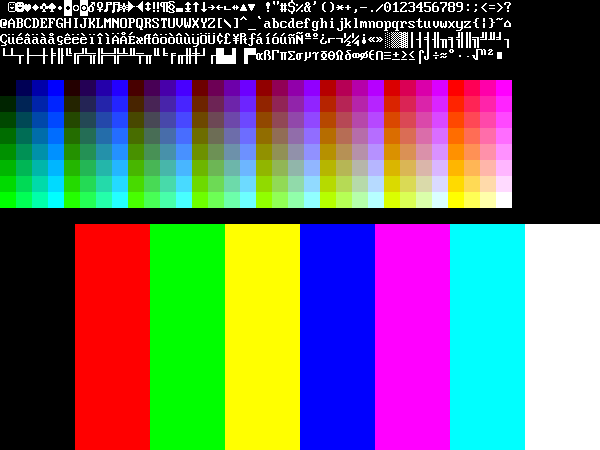

New Font ROM

07/22/2017 at 03:06 • 0 commentsI adjusted the font ROM to accomodate the full 256 character Code Page 437 and now load it via $readmemb from a list file. The font_test_gen and ntsc_test modules are also adjusted to print a 64-by-4 character array, vice the 64-by-2 from the old font ROM.

![]()

-

Project Article

07/15/2017 at 13:17 • 0 commentsNuts & Volts magazine has expressed interest in a project article for the NTSC Shield. I've already written an outline and should hopefully have a draft to them soon

-

NTSC Shield Test

07/10/2017 at 03:10 • 0 commentsThe SRAM and Video tests are now combined into a unified test.

-

SRAM Test

07/09/2017 at 02:26 • 0 commentsThe SRAM test is complete for the NTSC Shield. The test benches have also been complete updated for the sram-only branch.

-

SRAM Test - Device

07/05/2017 at 21:16 • 0 commentsThe Device Test is now functional. The final module is the Address Test Bus (I saved the most difficult for last). Hopefully I'll be done with that shortly and I can start working on the project write-up.

-

SRAM Test - Data Bus

07/01/2017 at 15:43 • 0 commentsA new branch has been added (sram-only) to test the NTSC Shield onboard SRAM. Currently a working Data Bus Test and appropriate test bench is functioning. Working on the Address Test now!

-

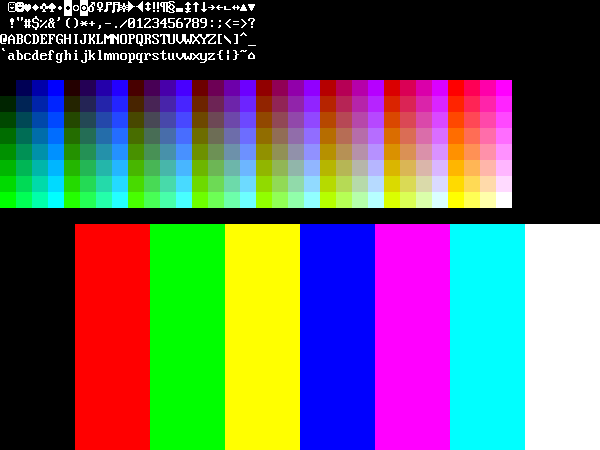

BMP File Output

06/28/2017 at 03:26 • 0 commentsI did some project restructuring, to include:

- Directory structure: moved src/ files to rtl/ and sim/

- Created ntsc_test and restructured mojo_top to reflect it

- Updated comments in several files

- Deleted no-serial branch and replaced with video-only branch

The biggest change is the addition of BMP file output to the following test benches:

- ntsc_test_tb

- rgb_332_palette_tb

- color_bars_tb

Below is what you should see for the ntsc_test_tb output, which matches what you'd see on the television:

![]()

-

Verilog Uploaded to Github

06/24/2017 at 02:05 • 0 commentsThe working Verilog code for the NTSC Shield is available on Github. There are two branches:

- master: video test and basic SRAM test (activated via serial port)

- no-serial: video test only

Current working progress is to integrate the SRAM test results to the television, which will run on startup.

-

Video Test Complete

06/22/2017 at 01:24 • 0 commentsWell, it's been a long time coming. I started this project in February 2017 and have finally had a successful text, palette, and color bar test. Life got in the way and slowed down my progress, but progress has been made!

There is a little bit of pixel jitter on the output, which I'm pretty sure is due to the fact that the FPGA is running asynchronous with the AD723. The FPGA outputs pixels at 12.5 MHz and the AD723 is running at 14.31818 MHz. I can fix this in the future with a board revision and some clock domain management, but it's not important right now.

With the video test complete, I now need to work on a comprehensive SRAM test and output the results to the television. I've already ran a basic error check on the SRAM and output the results via serial, but I want to display everything on the television. Coming soon!

![]()

Ryan

Ryan