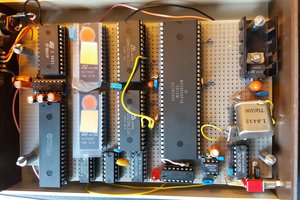

Mackerel-08

This SBC combines the 52-pin PLCC MC68008, a 512KB EEPROM, 3.5MB of SRAM, and a XR68C681 DUART on a single PCB. The DUART provides two serial ports and three bit-banged SPI connections. One of these connections is used with an SD card breakout board to act as permanent storage for the system.

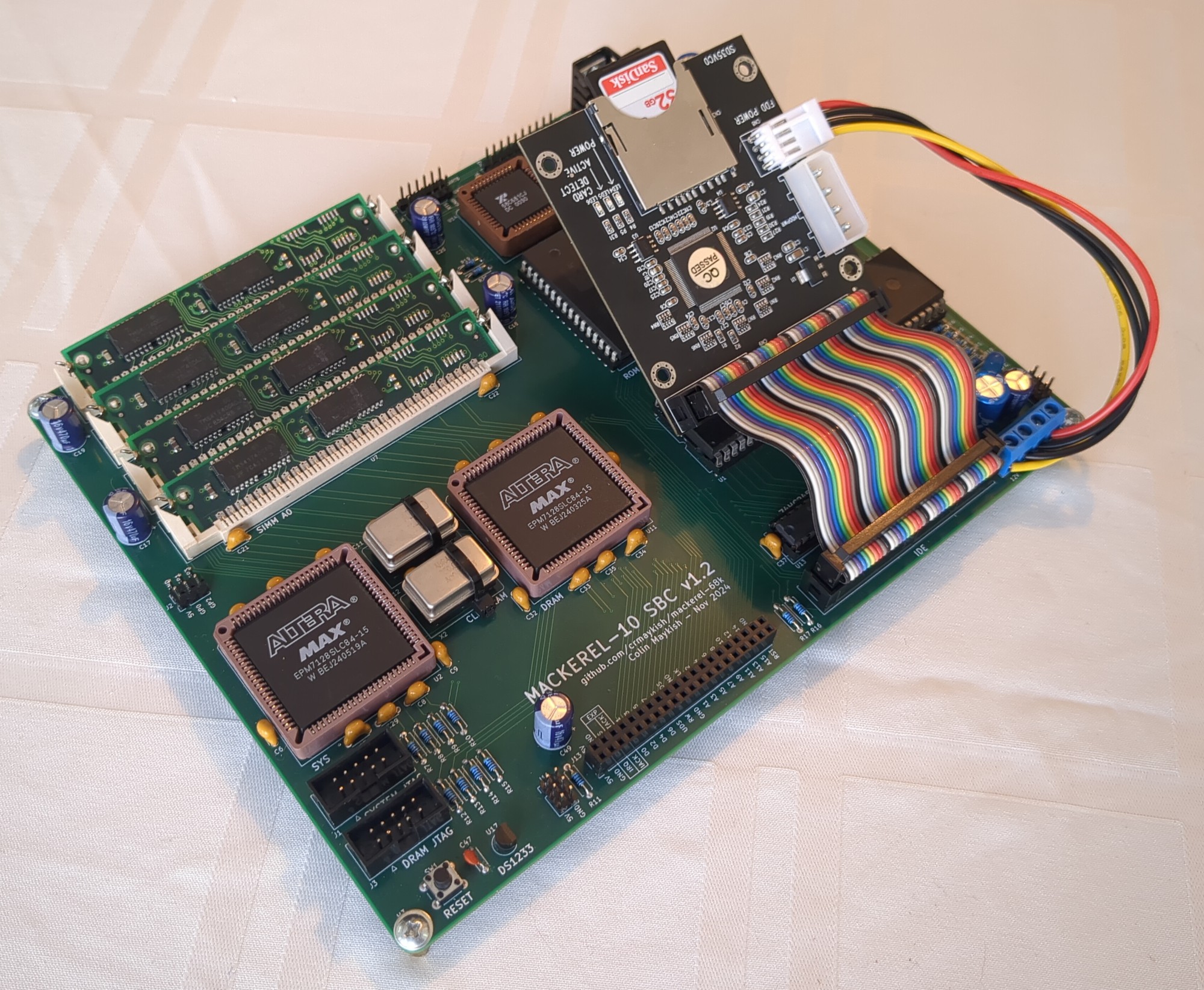

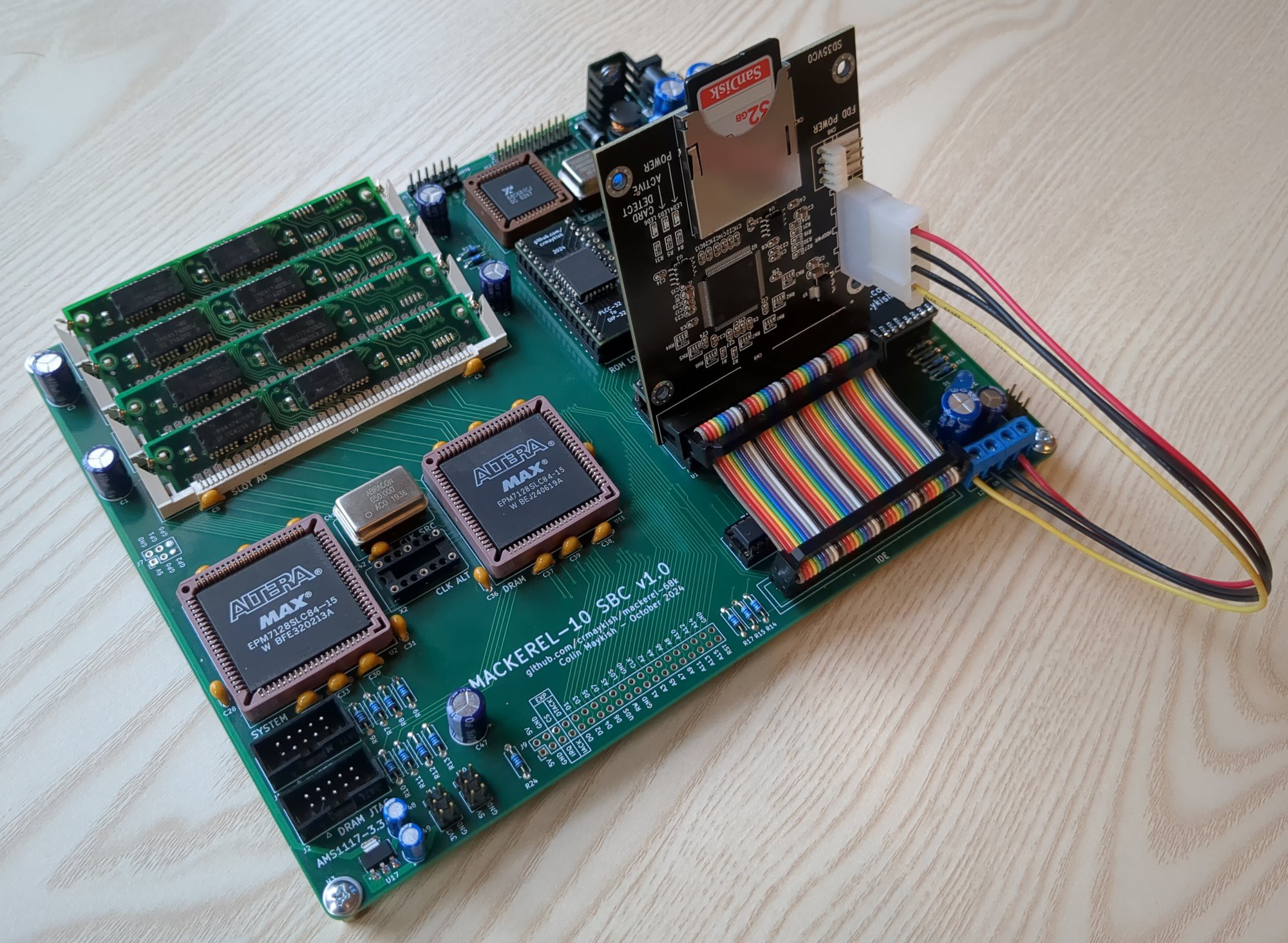

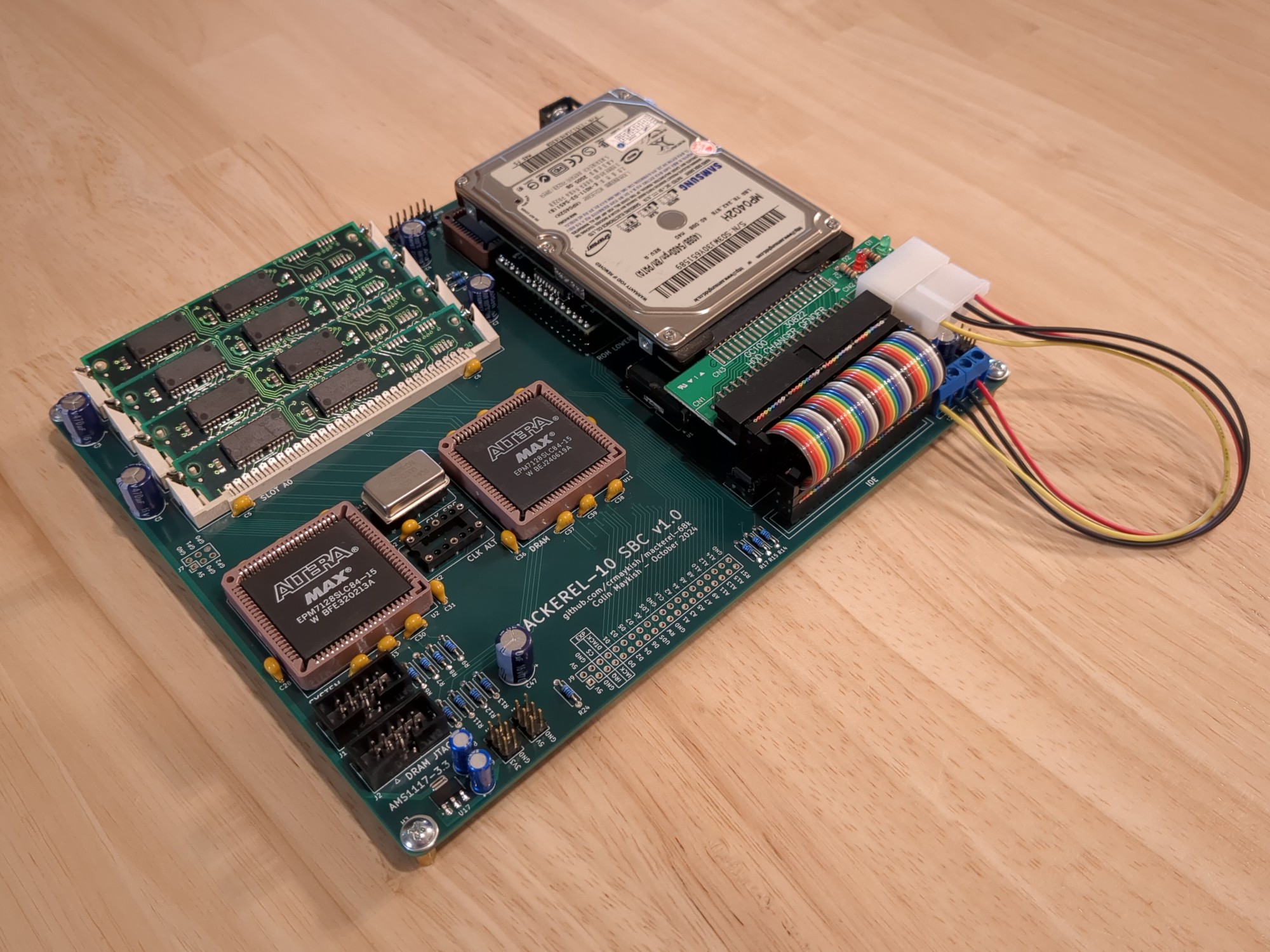

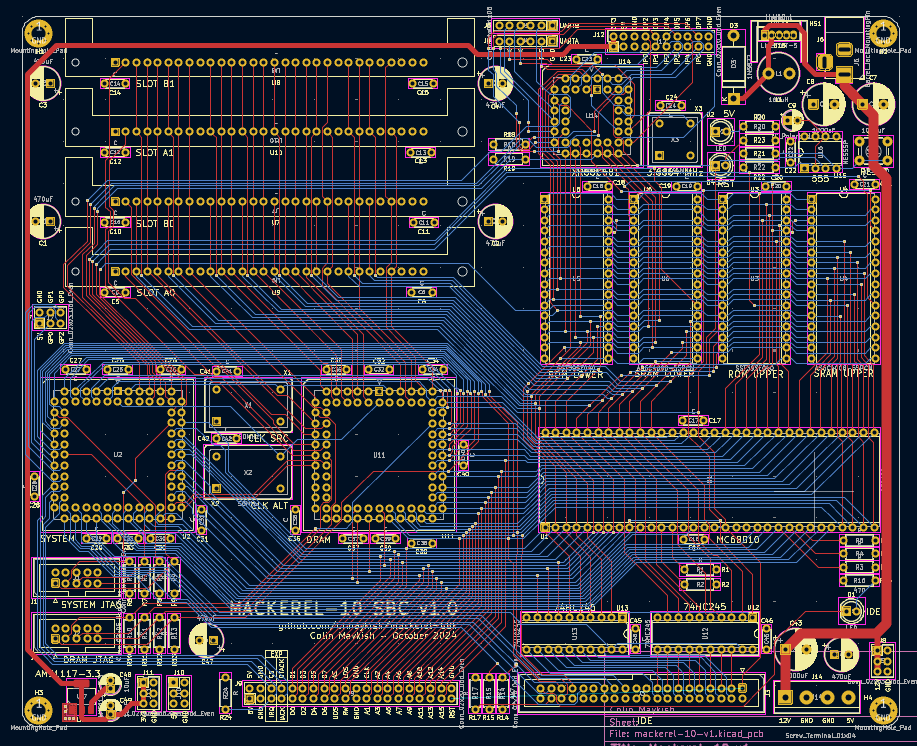

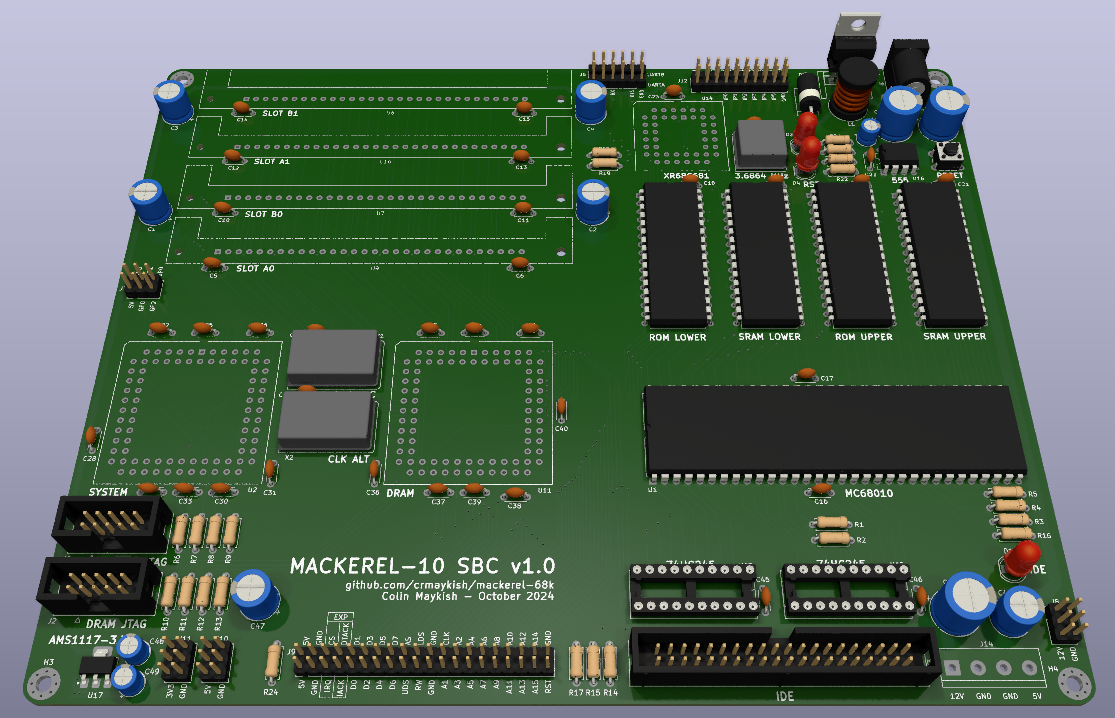

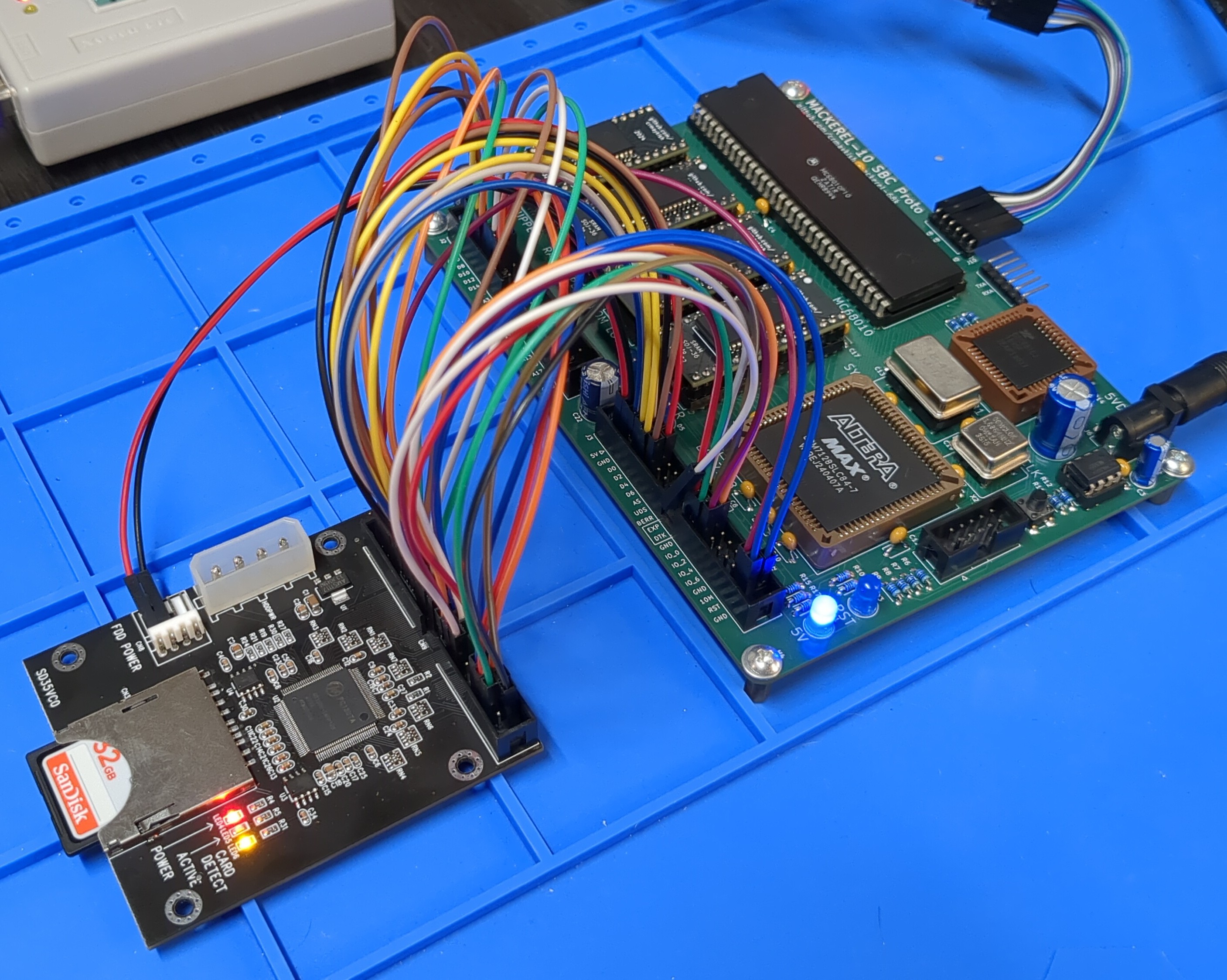

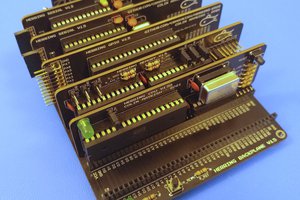

Mackerel-10

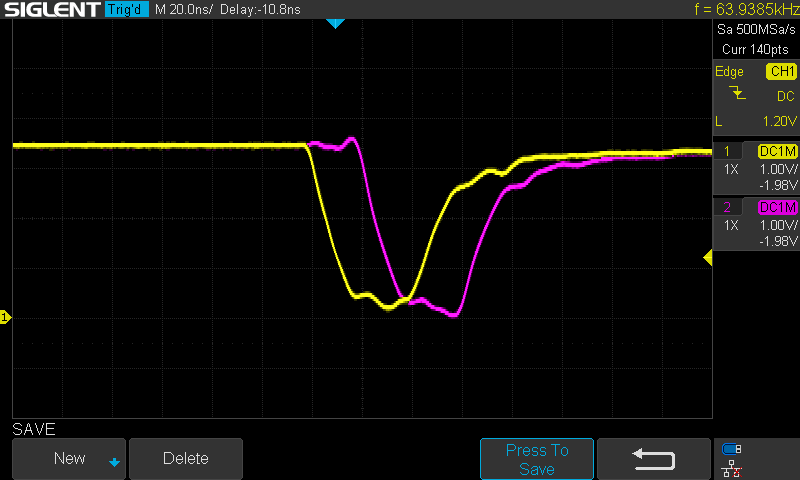

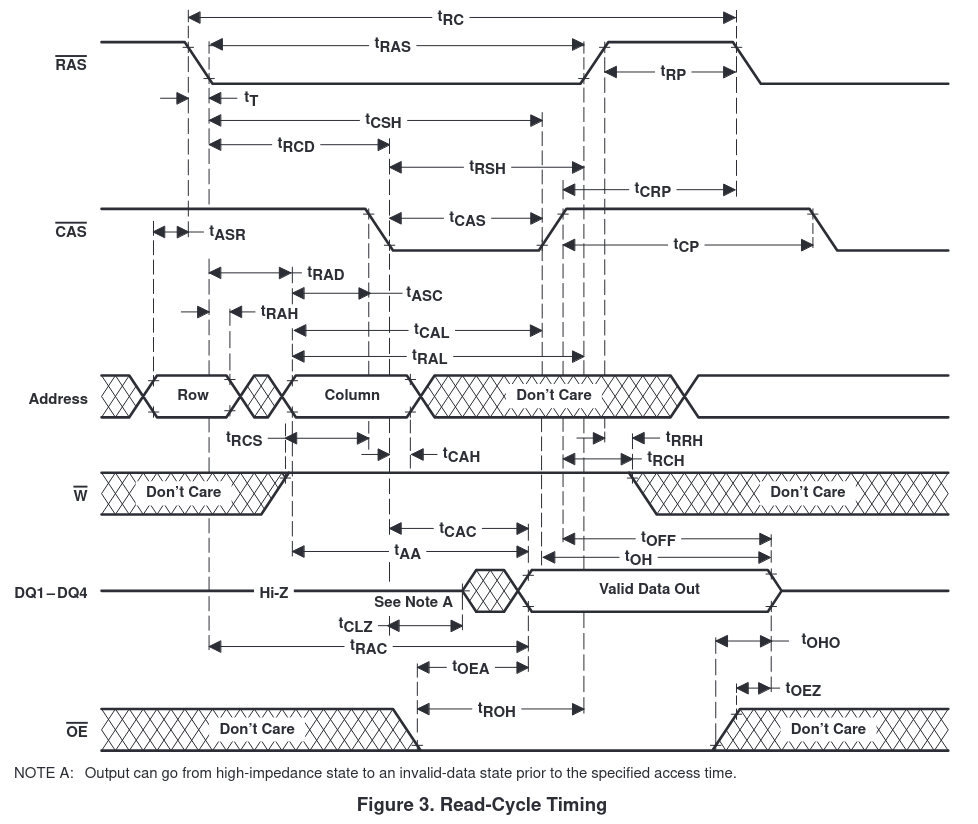

Mackerel-10 is the second phase of the project, It expands the design of Mackerel-08 with a 68010 CPU and 16-bit databus. Additionally, it increases the memory capacity with a DRAM controller implemented in a CPLD and up to 16 MB of 30-pin DRAM. The onboard IDE header allows a real hard drive or SD-to-IDE adapter to be used as a block device in uClinux.

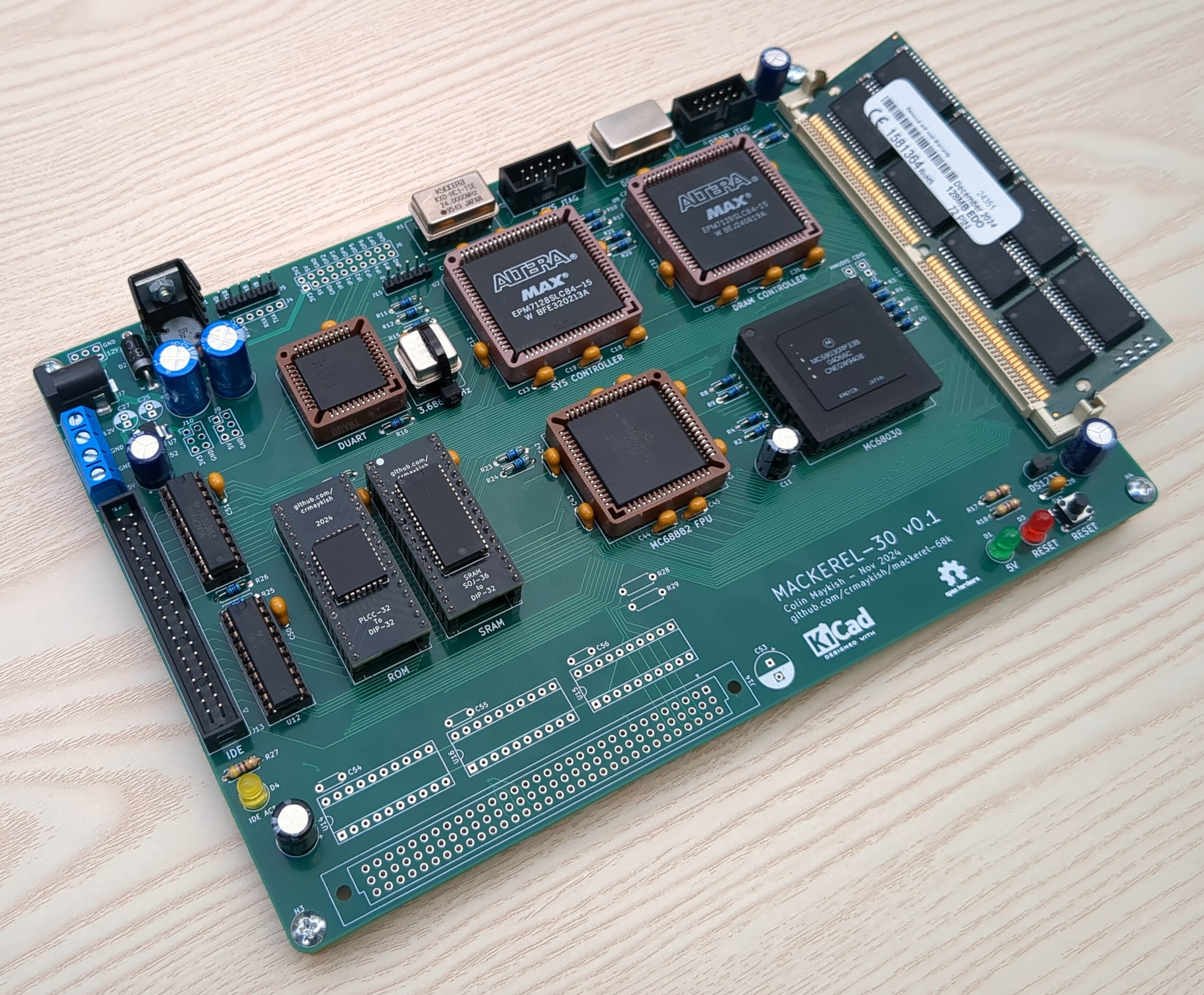

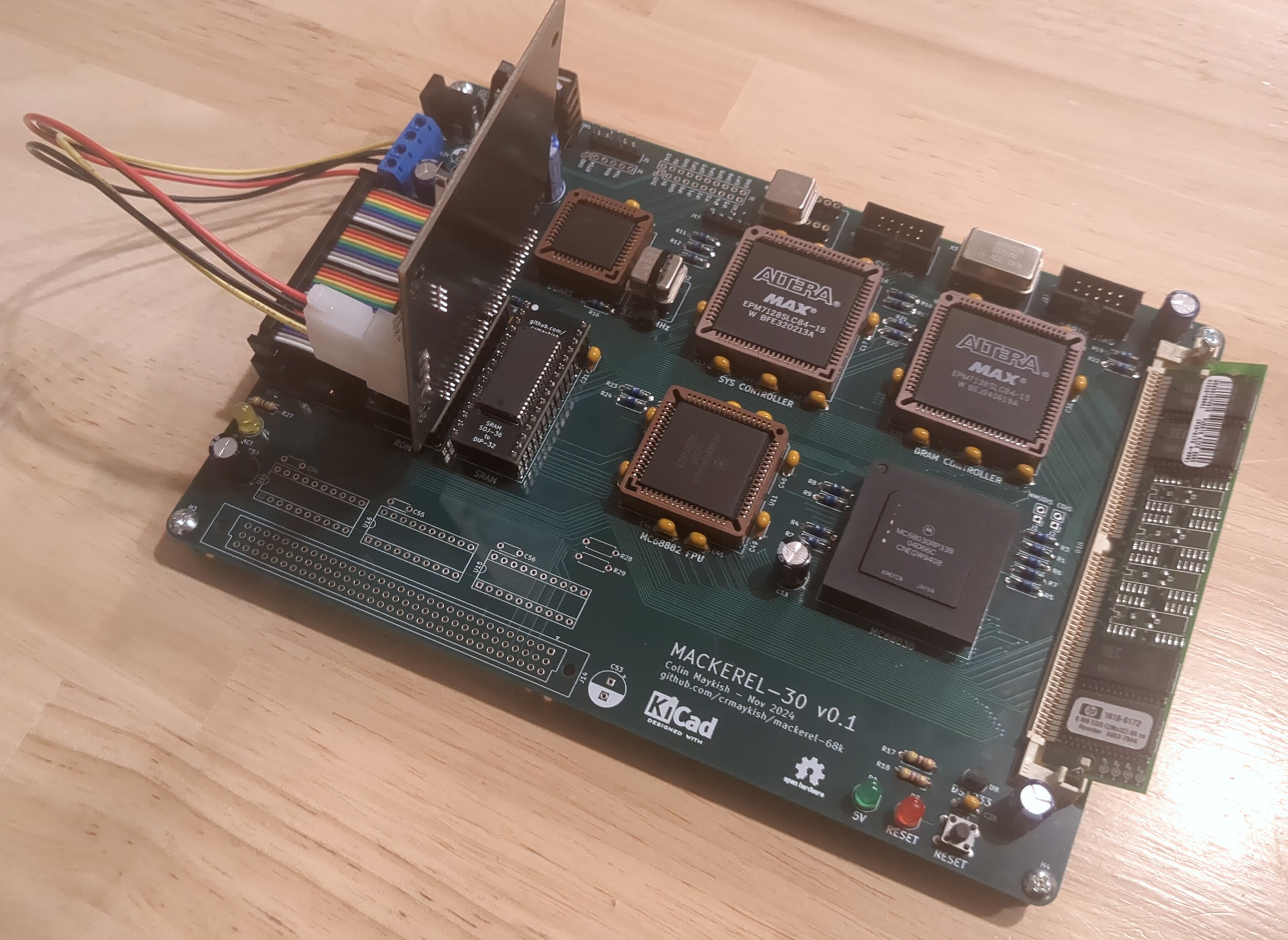

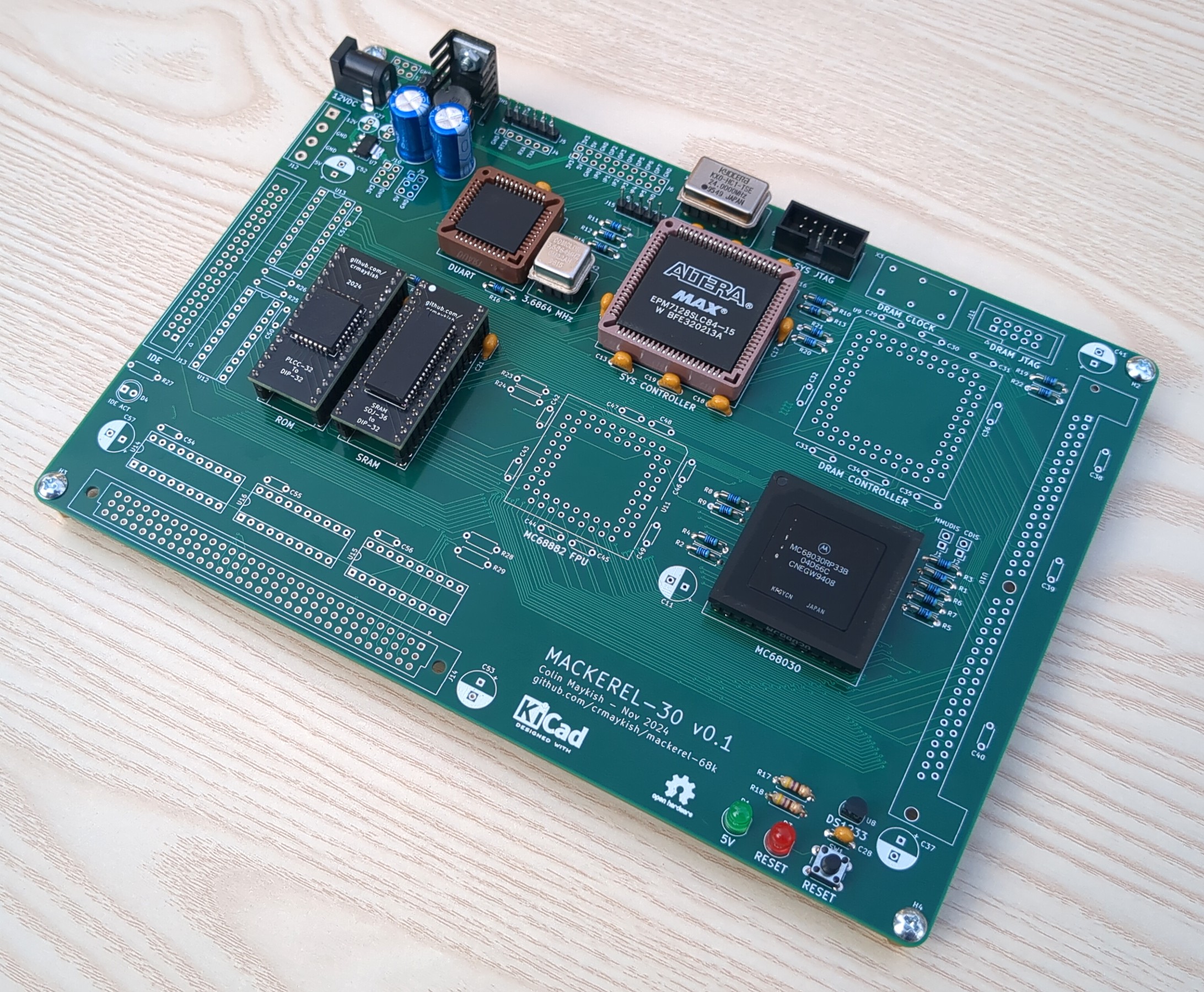

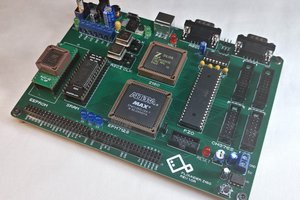

Mackerel-30

The first fully 32-bit system, this SBC is based on the 68030 CPU with an MC68882 FPU. The DRAM controller now uses 72-pin SIMMs allowing up to 128 MB of DRAM.

Colin M

Colin M

Jason Westervelt

Jason Westervelt

The 030 board is looking very nice ! Why do you use SOJ memory chips on a header rather than native DIP32 5v memory chips - is it speed ? Same question for the flash ..