There has been a lot of DIY effort to make a good, cheap constant current electronic load. I must give homage to the efforts of past attempts, mostly successful, to create something useful for evaluating a power supply's capability or a battery's capacity. It's not easy.

One of the best is Dominik's: https://github.com/Dominik-Workshop/Electronic_load/tree/master

His implementation covers most of the bases and we used it as a benchmark. But it is a bit lacking in user stupidity protection. (And we wanted more.)

Another implementer worth mentioning (besides our eminent Hackaday colleagues) is John Sculley with his excellent treatise on YouTube: https://www.youtube.com/playlist?list=PLUMG8JNssPPzbr4LydbTcBrhoPlemu5Dt

But alas, Mr. Sculley descends into the mire of fixing unforeseen predicaments in a seemingly never-ending fix-it scenario. I guess a nice way of putting it is "Feature Creep".

We recommend viewing Kerry Wong's excellent YouTube videos (https://www.youtube.com/watch?v=WUPrj03UbTM) on Linear MOSFETs for an education in the reality of "Safe Area of Operation", or SOA, for the uninitiated.

This is a Team Effort:

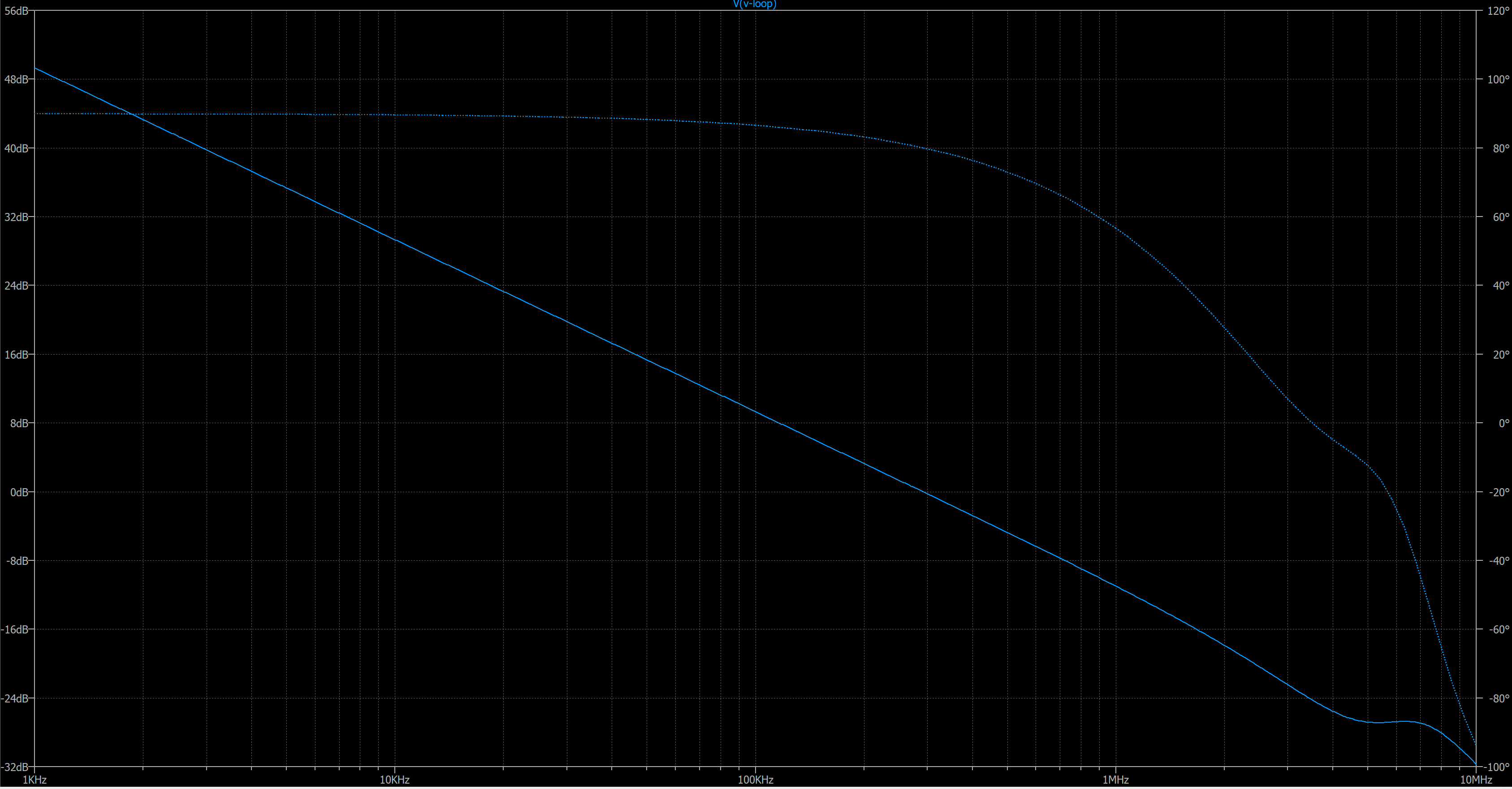

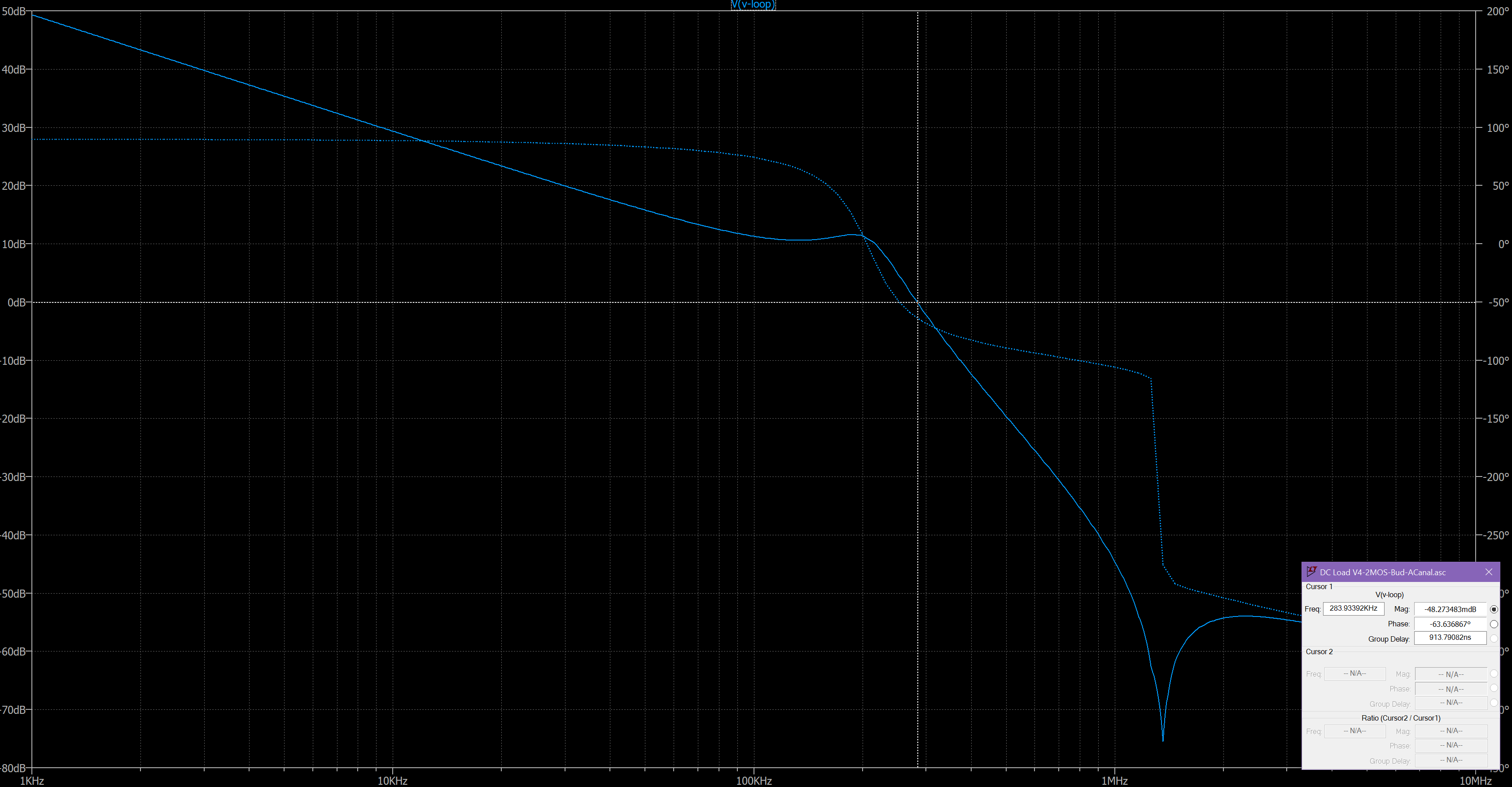

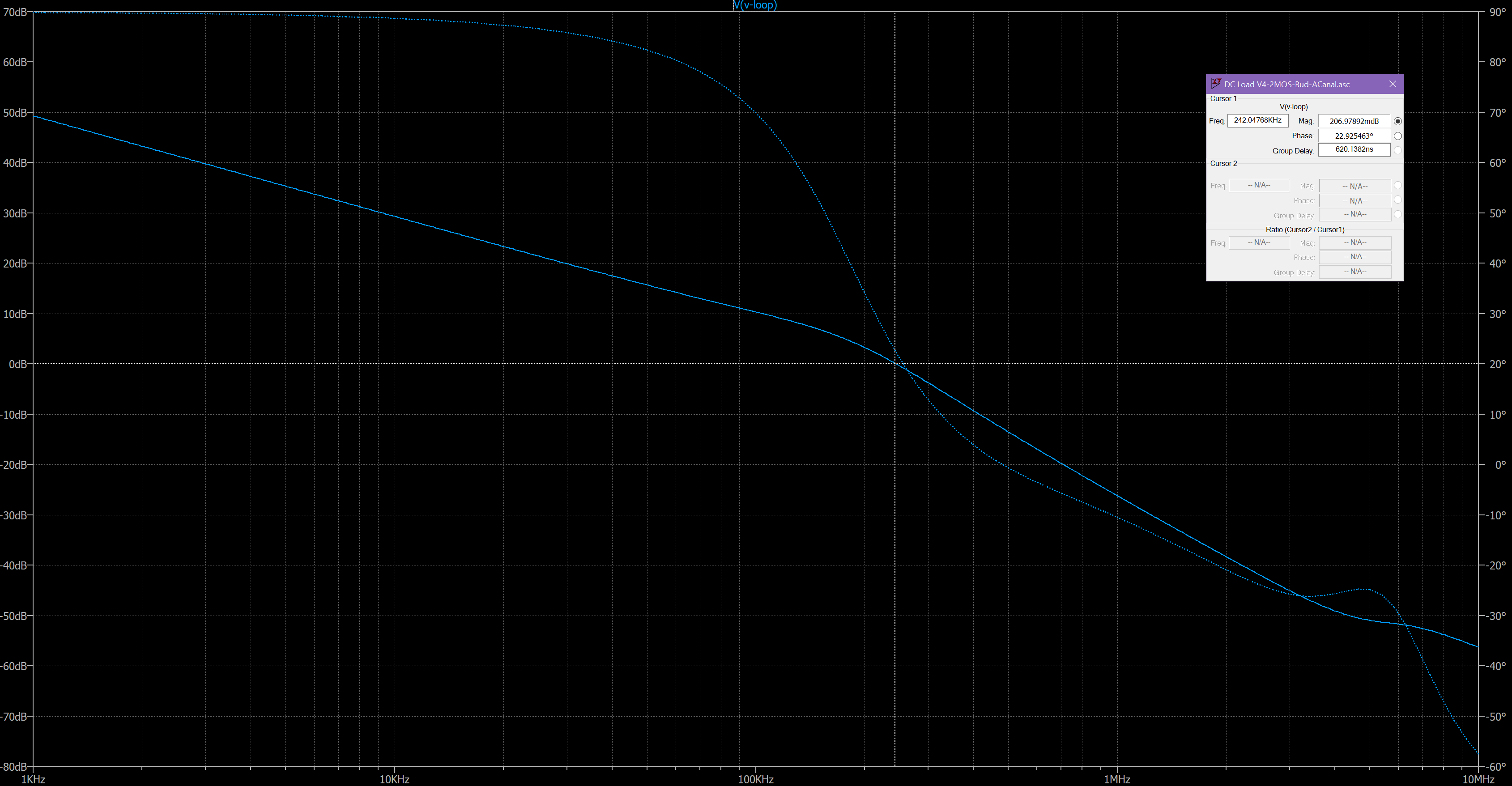

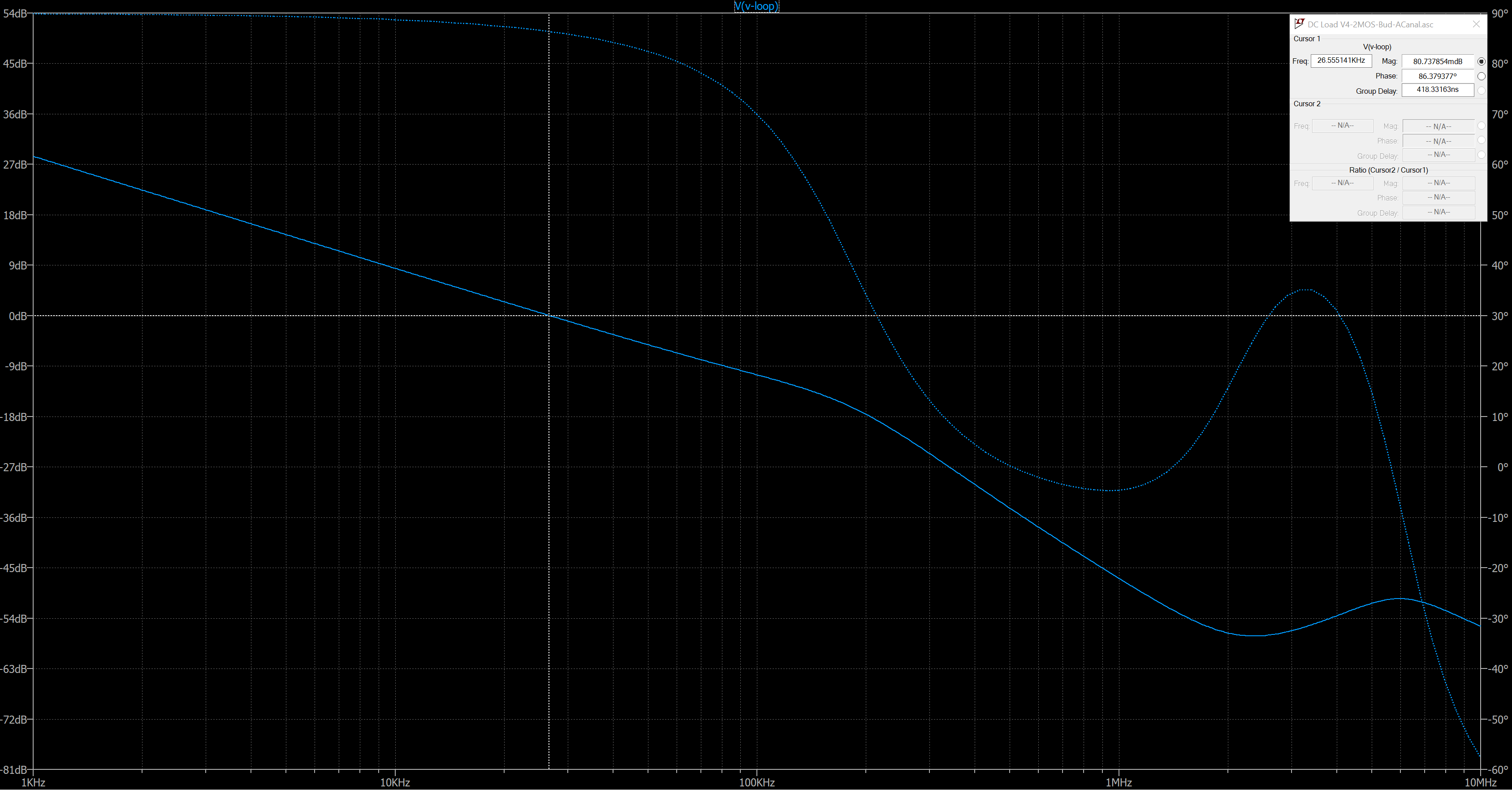

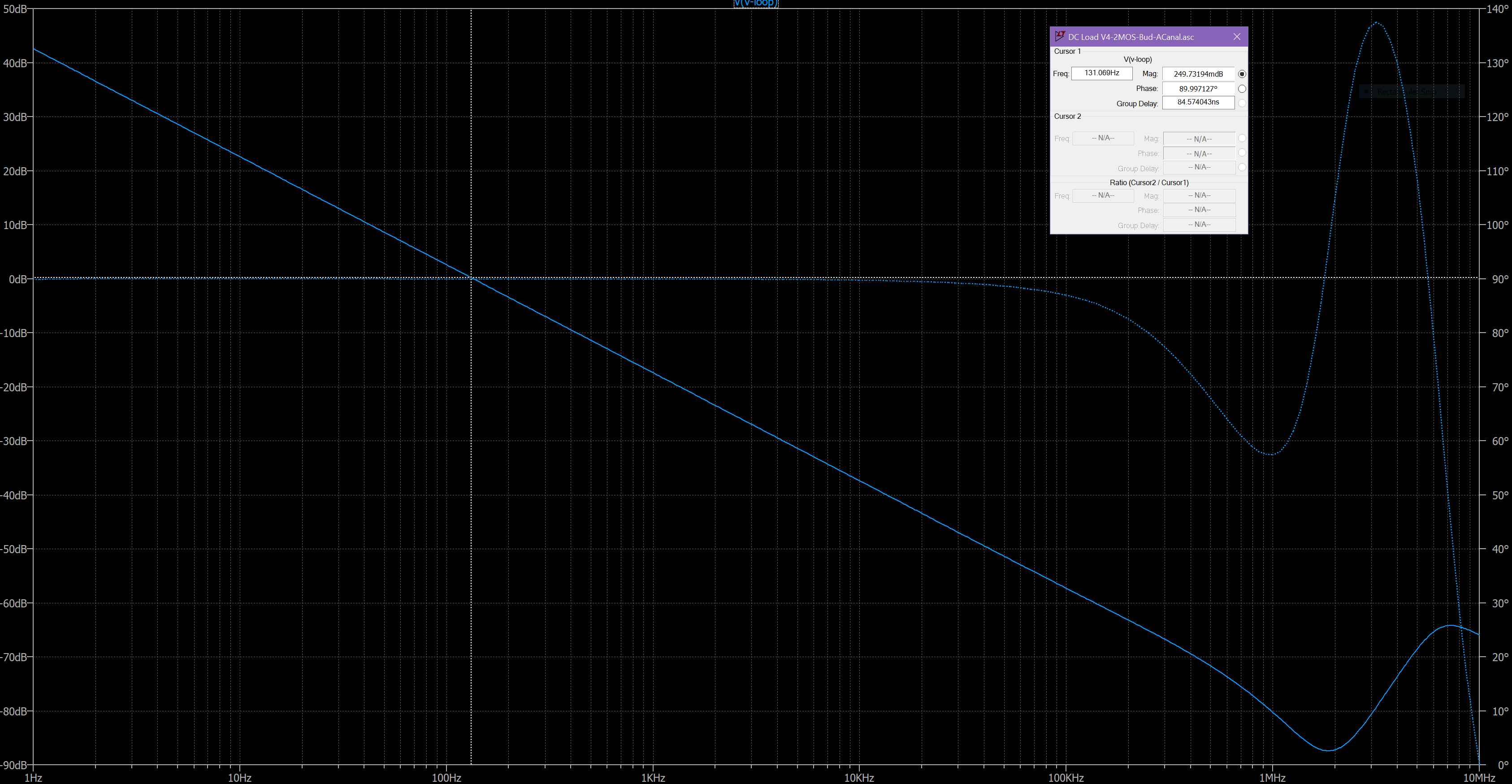

Paul has been working on this for a while. I entered the scene when he had a problem with oscillation that he couldn't explain while evaluating his latest prototype. Paul's blog on this subject is here: https://www.paulvdiyblogs.net/2024/09/building-diy-dynamic-dc-load.html

He covers the build process in a lot more detail and has the Gerber files and BOM, along with a supplemental BOM for specialty parts and their sources. What you find here is just the circuit design aspects.

Project Status (2024-12-02):

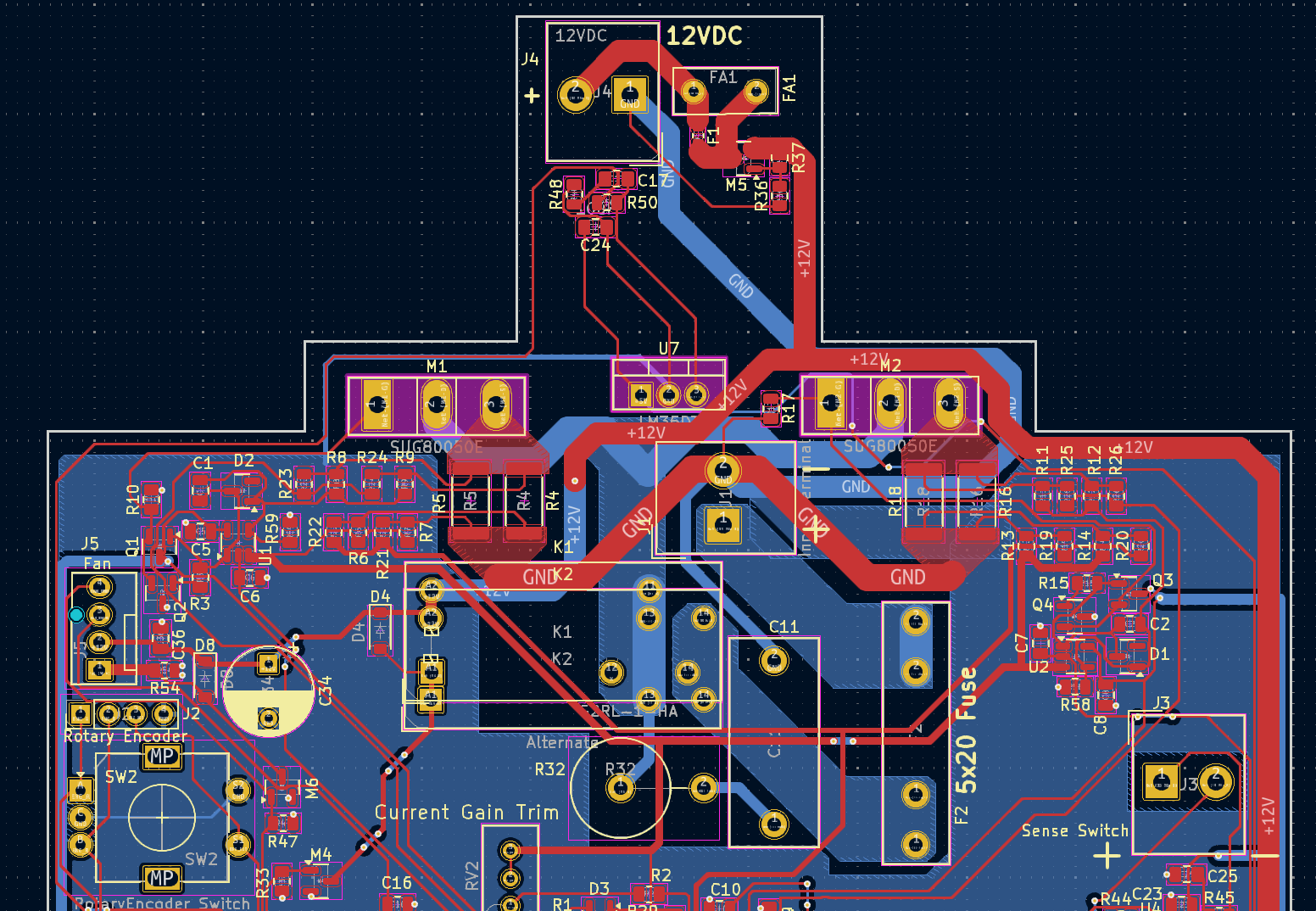

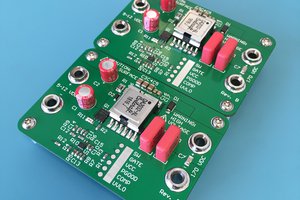

The PCB (rev 5.1a) is the our final version, which fixed the problem with second fan not running.

There are now two fans for thermal management. The two fans are wired in parallel -- there are two 4-pin fan connectors on the PCB. One fan, 92mm, sits below the heat sink and blows cool air up into the fins. The other 92mm fan is mounted at the rear of the enclosure and suck hot air out of the enclosure. This has been tested to 185W, the limit of my power supplies.

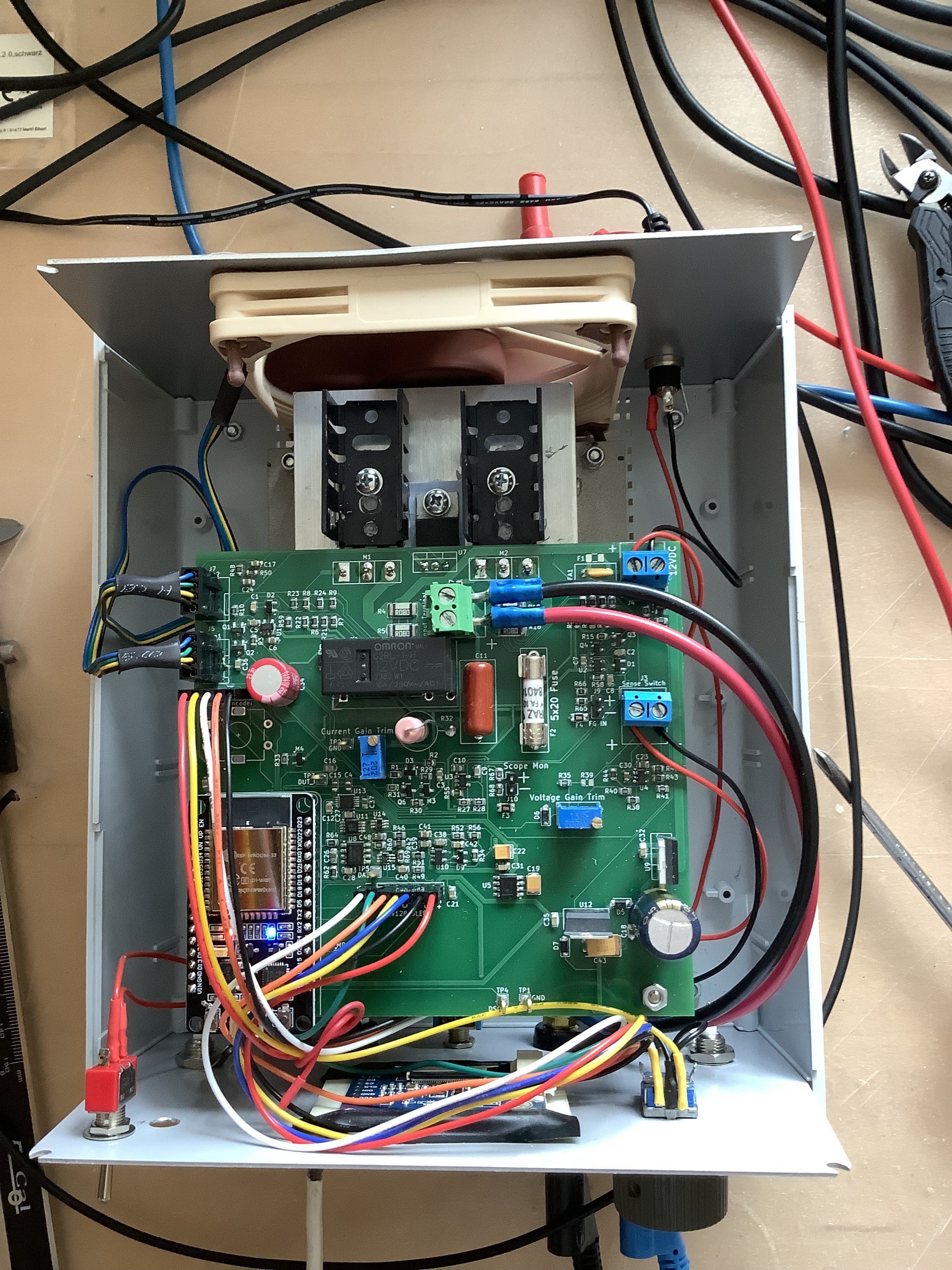

The enclosure is another problem. It should be plastic, to isolate the heatsink (which is connected to the output terminal) from the user. Paul found an acceptable enclosure -- a Teko AUS 33.5 (198x178x108mm) -- but it is not readily available in the USA and the shipping is costly. Paul is going to create PCB panels for the front and back to make it look less DIY, so this is the only enclosure we recommend that you can purchase (though there is an option to print your own, or have somebody else print it). This is what the inside of the enclosure looks like with the current PCB revision:

Target Specs:

Input Voltage: 1V - 100VDC

Input Current: 1mA - 4A for 40V < Vin < 100V, 1mA - 10A for 1V < Vin < 40V.

Maximum Power Dissipation: 150-200W (Depends upon heatsink and Fan.)

Voltage Accuracy: 0.4% (Trimmed, but there are temperature drift terms.)

Current Accuracy: 0.4% (Trimmed. Mostly temp drift error.)

Lowest Conductance: Untested. (Current NFETs + Sense R + Relay contact R = 75mR)

Ripple: Untested.

Protection: Reverse polarity to -100V. 15A fast blow fuse at input.

Power Input: 12VDC/1A Wall Adapter. Reverse polarity protected to -24V.

Cost: $200 (Aproximate. $35 Case, $38 Fans, $23 OLED, $12 Heat Sink, $6 ESP32, ~$75 Assembled PCB, $10 Misc Hardware.)

User Interface:

Display: 128x128 Color OLED.

User Input: Rotary Encoder with push switch. Remote/Local voltage sensing switch on front panel.

The Software:

Pretty much done at this point (rev 26b). See Paul's Github page to download files.

The Hardware

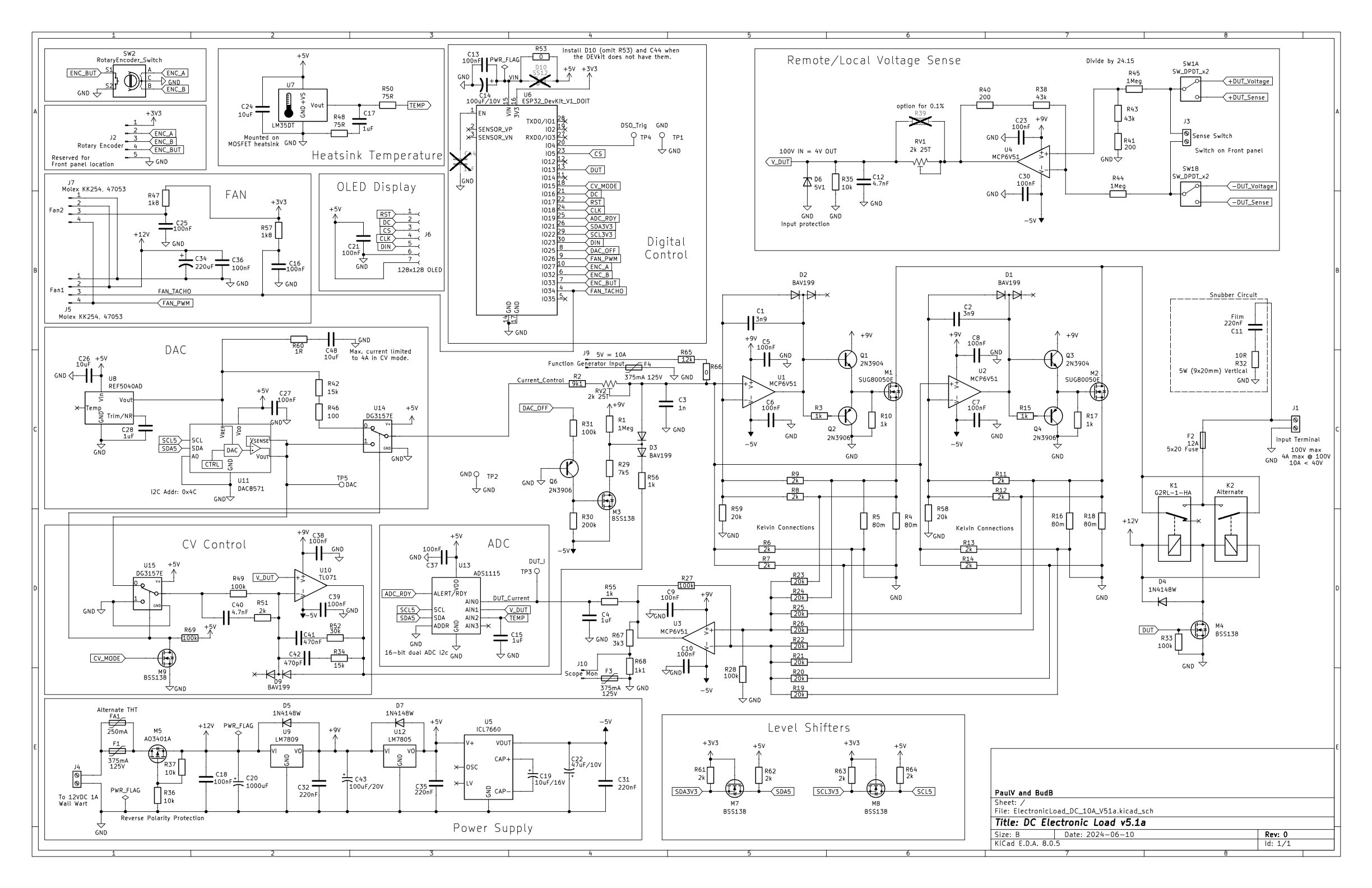

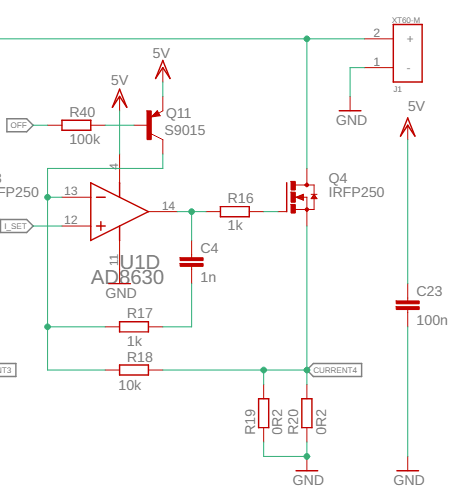

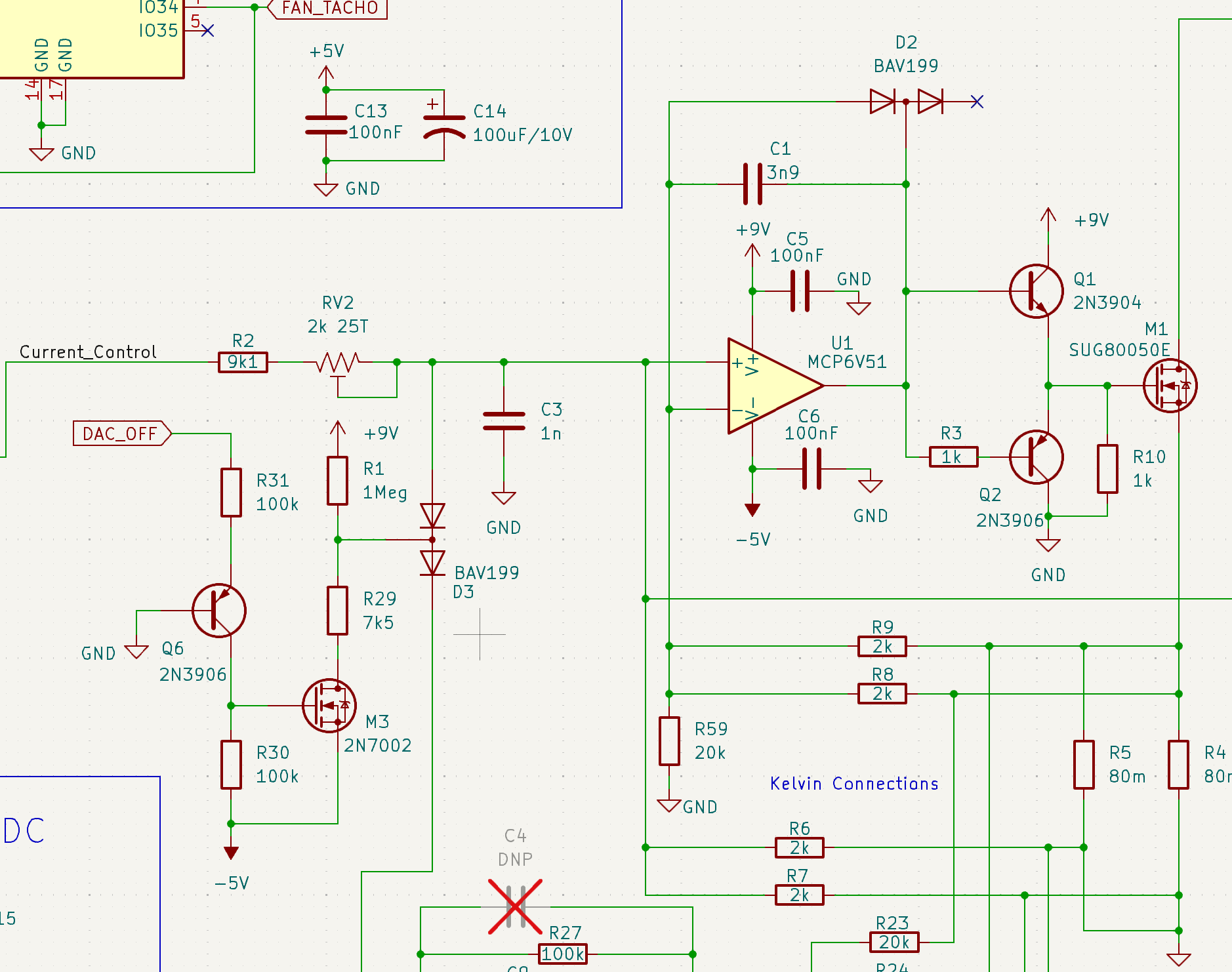

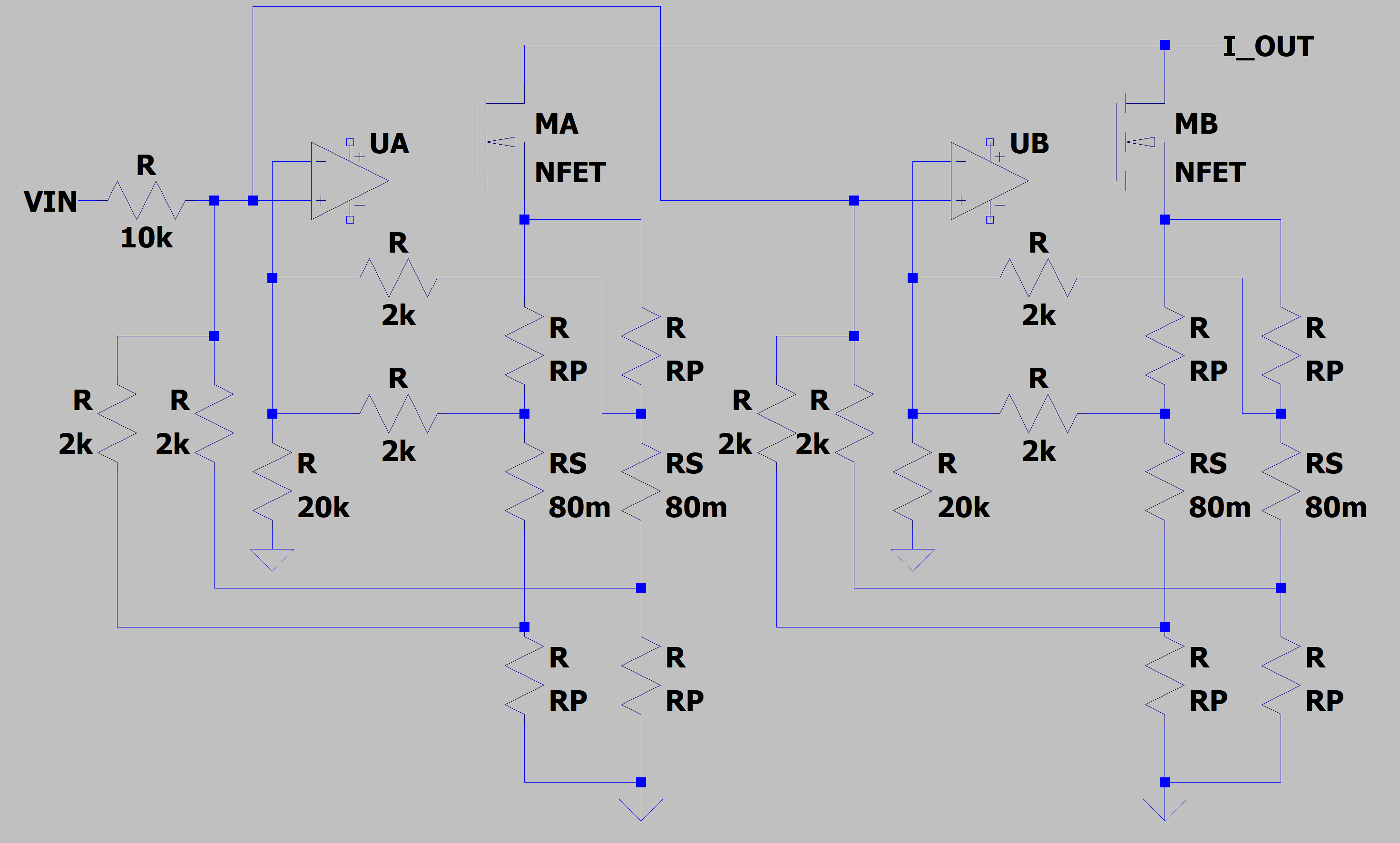

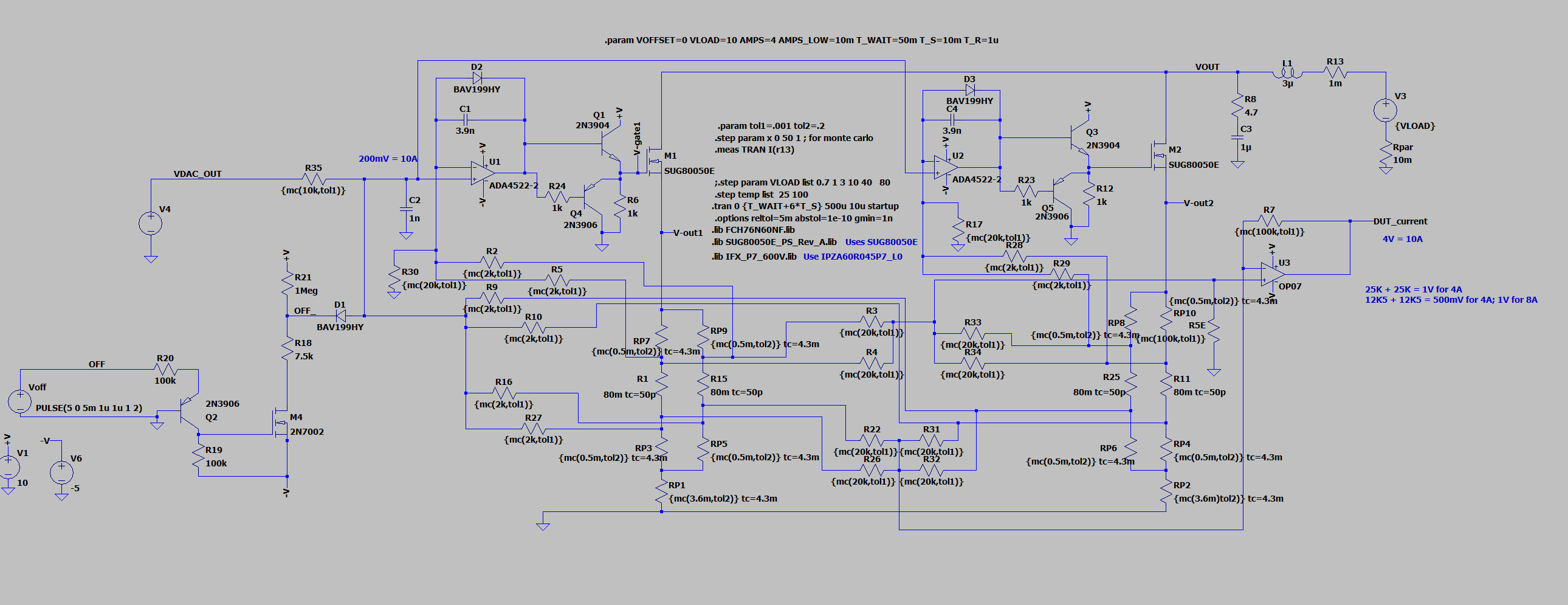

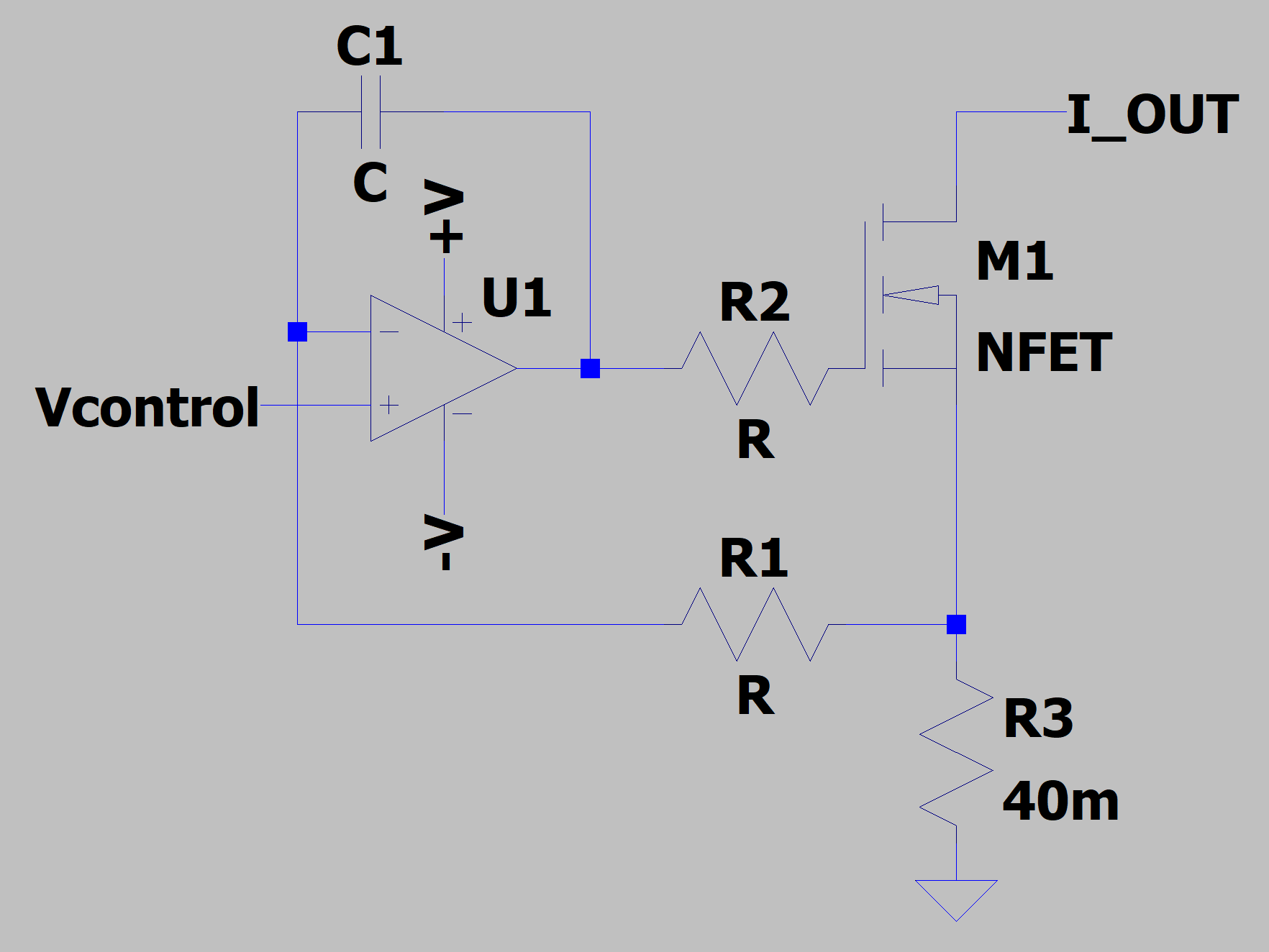

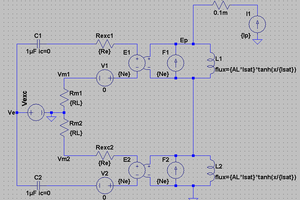

Here is our final schematic (as of 2024-06-10).

The first thing to notice is that there is a relay and fuse to protect the circuit guts against inadvertent stupidity. It's better to replace a fuse than toss an entire circuit in the trash. The nice things about relays are that...

Read more » Bud Bennett

Bud Bennett

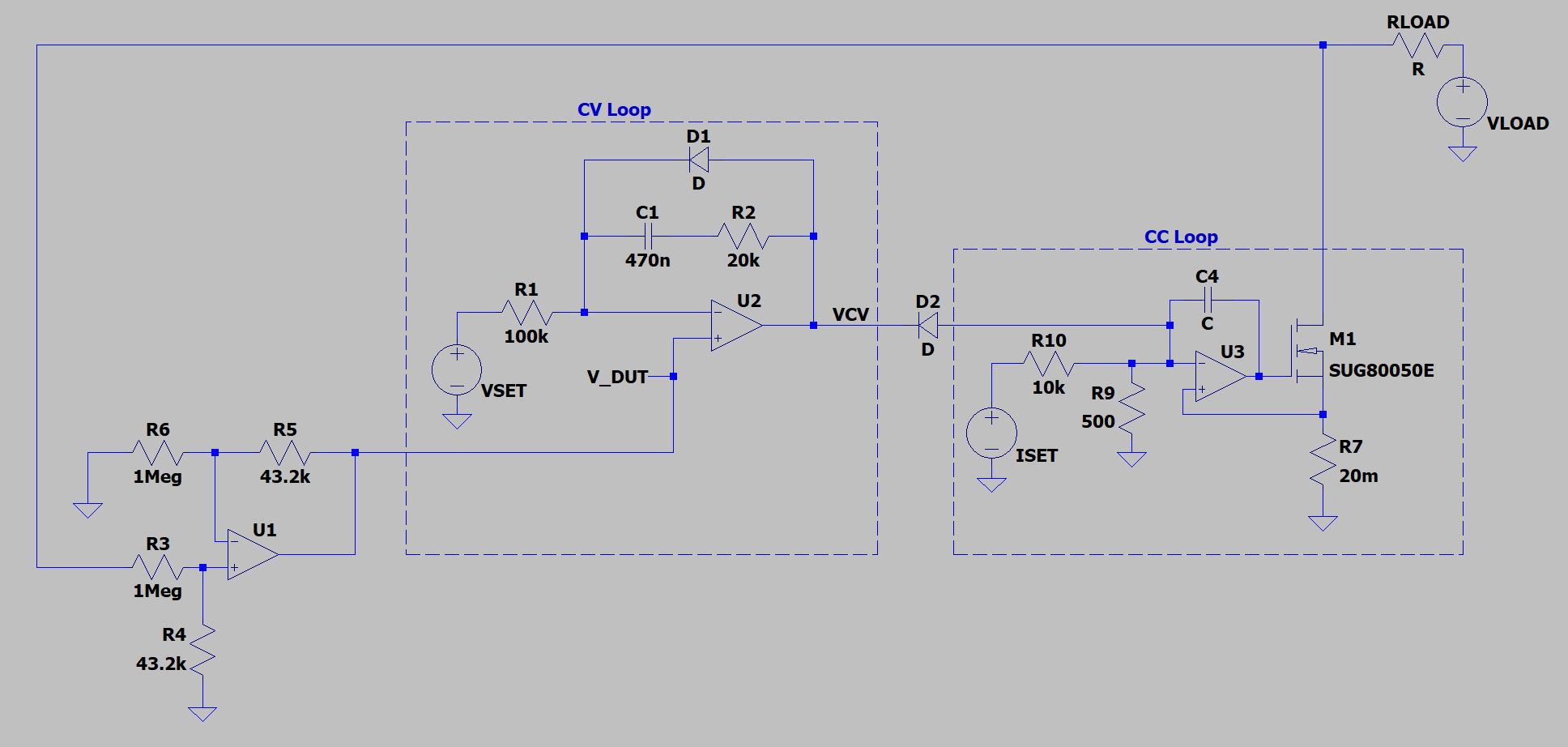

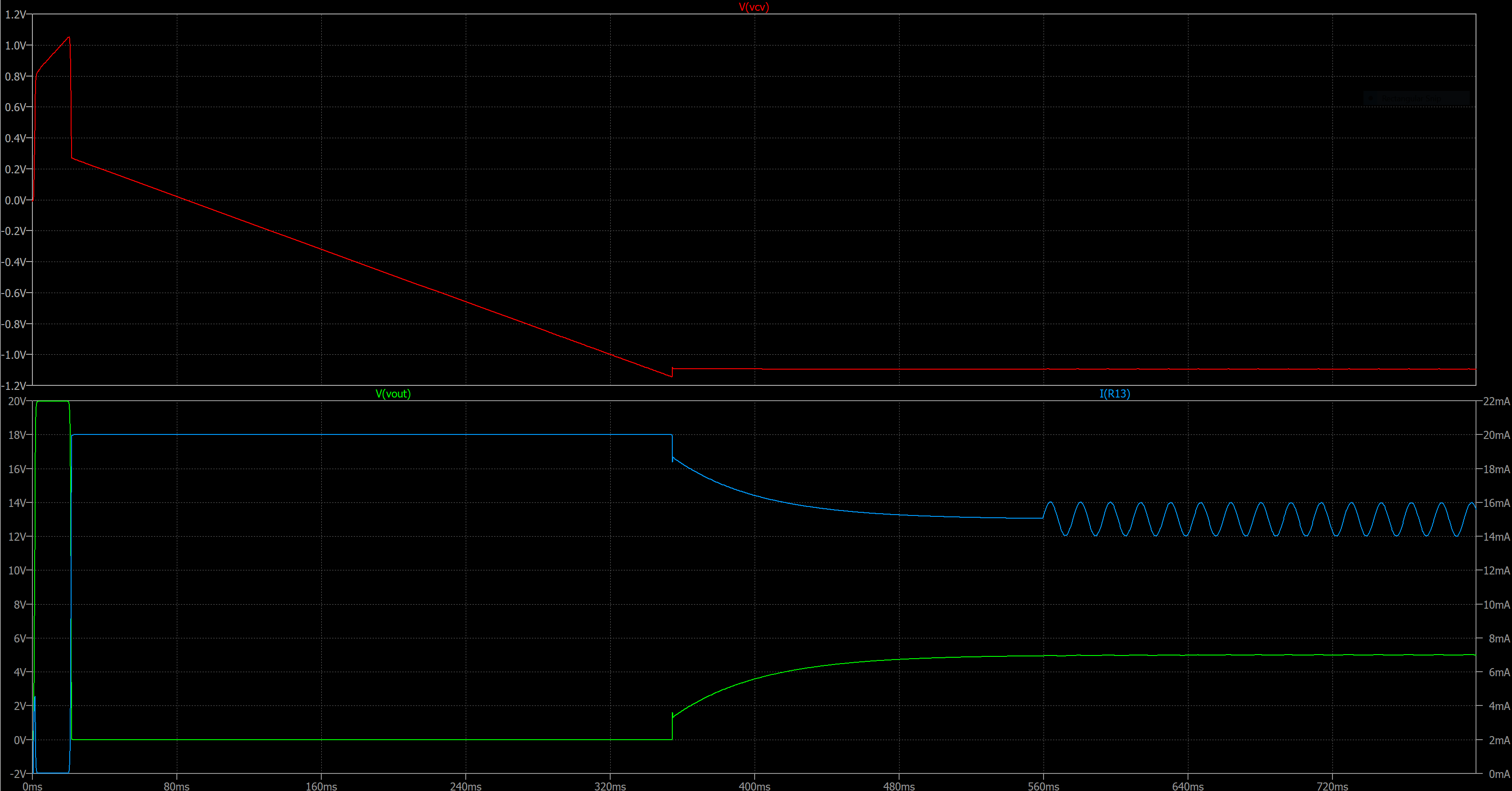

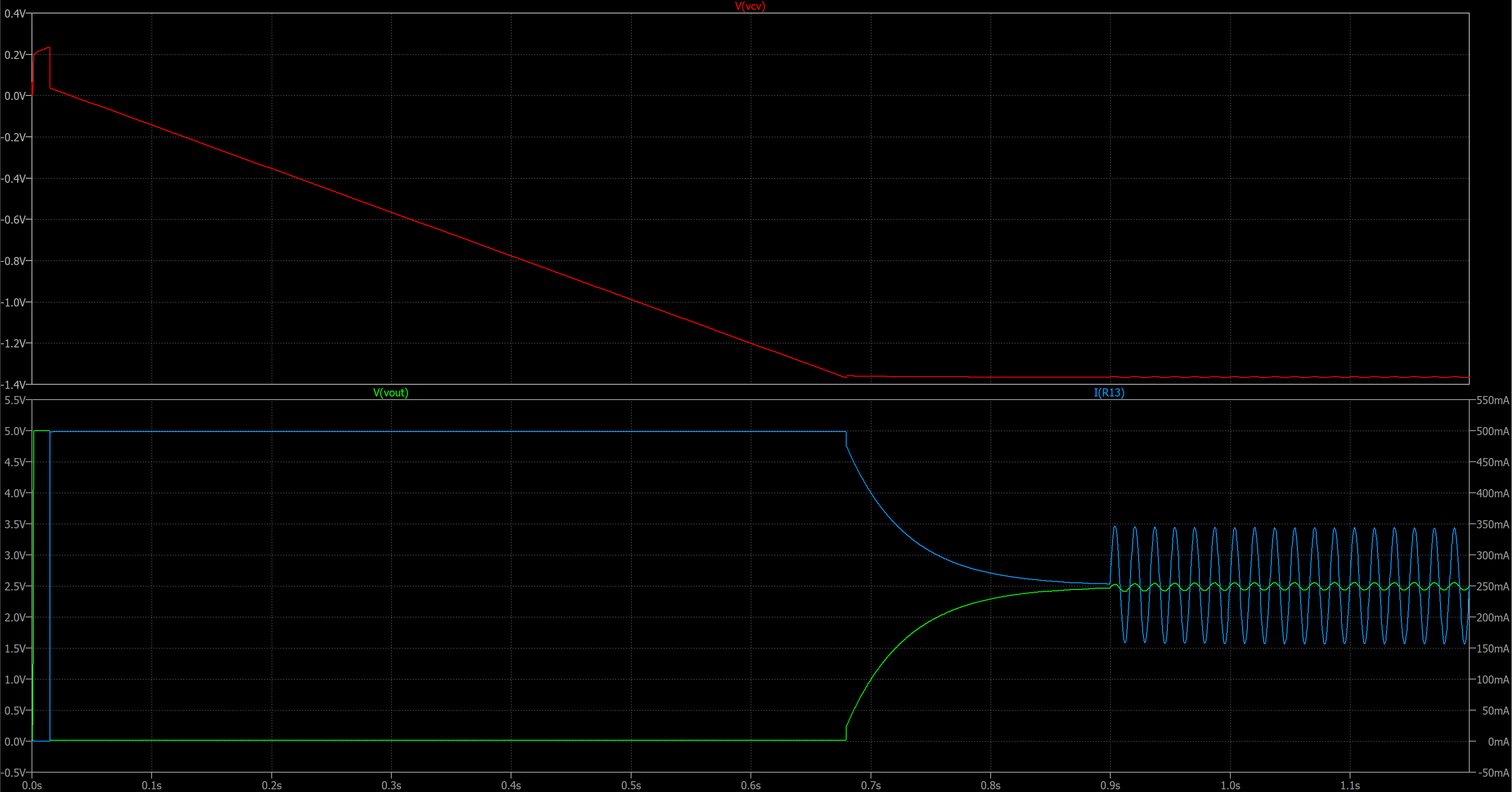

The system is held at zero output current for 5ms and then released. The CV opamp is out of control until VSET changes from zero to 0.2V, but it has to slew to 1.2V below GND before it takes control from the CC loop. Since the CC loop can output 125mA it drives the output voltage to zero (125mA x 1k = 125V, but only 20V is applied). Once the CV loop overcomes the CC loop the current decreases in the CC loop and the load voltage rises to the set point (5V). A 1V-peak sinusoid on top of VLOAD is applied at 560ms to show that the CV loop can keep the output voltage stable when disturbed. I think it performs pretty well, if slowly.

The system is held at zero output current for 5ms and then released. The CV opamp is out of control until VSET changes from zero to 0.2V, but it has to slew to 1.2V below GND before it takes control from the CC loop. Since the CC loop can output 125mA it drives the output voltage to zero (125mA x 1k = 125V, but only 20V is applied). Once the CV loop overcomes the CC loop the current decreases in the CC loop and the load voltage rises to the set point (5V). A 1V-peak sinusoid on top of VLOAD is applied at 560ms to show that the CV loop can keep the output voltage stable when disturbed. I think it performs pretty well, if slowly.

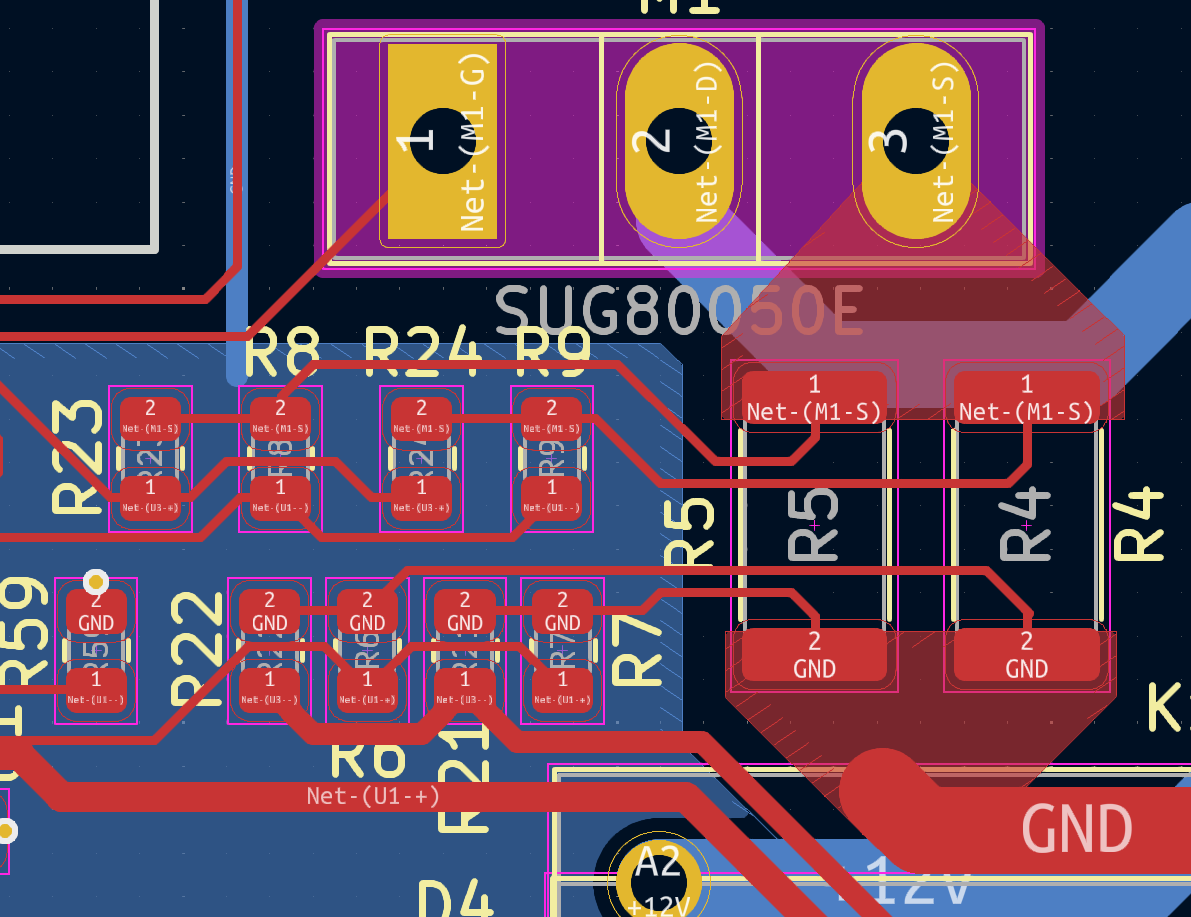

The current tends to spread in 45 degree funnels from a single point to a connection point, such as a pad on a component. In order to make the Kelvin connection the current should be zero at the point of the Kelvin connection. I made triangular copper pours to distribute the current to the two sense resistors. The back-side of the pads should have zero current flowing to it and therefore a good place for a Kelvin pickup. The pickup points are on the middle-inside of the pads on the sense resistors. Those traces connect the feed resistors for sensing the voltage across the sense resistors.

The current tends to spread in 45 degree funnels from a single point to a connection point, such as a pad on a component. In order to make the Kelvin connection the current should be zero at the point of the Kelvin connection. I made triangular copper pours to distribute the current to the two sense resistors. The back-side of the pads should have zero current flowing to it and therefore a good place for a Kelvin pickup. The pickup points are on the middle-inside of the pads on the sense resistors. Those traces connect the feed resistors for sensing the voltage across the sense resistors.

Sagar 001

Sagar 001

James Wilson

James Wilson

jbb

jbb

Tron9000

Tron9000

Hi Bud!

I've gone over the project logs and had a quick question.

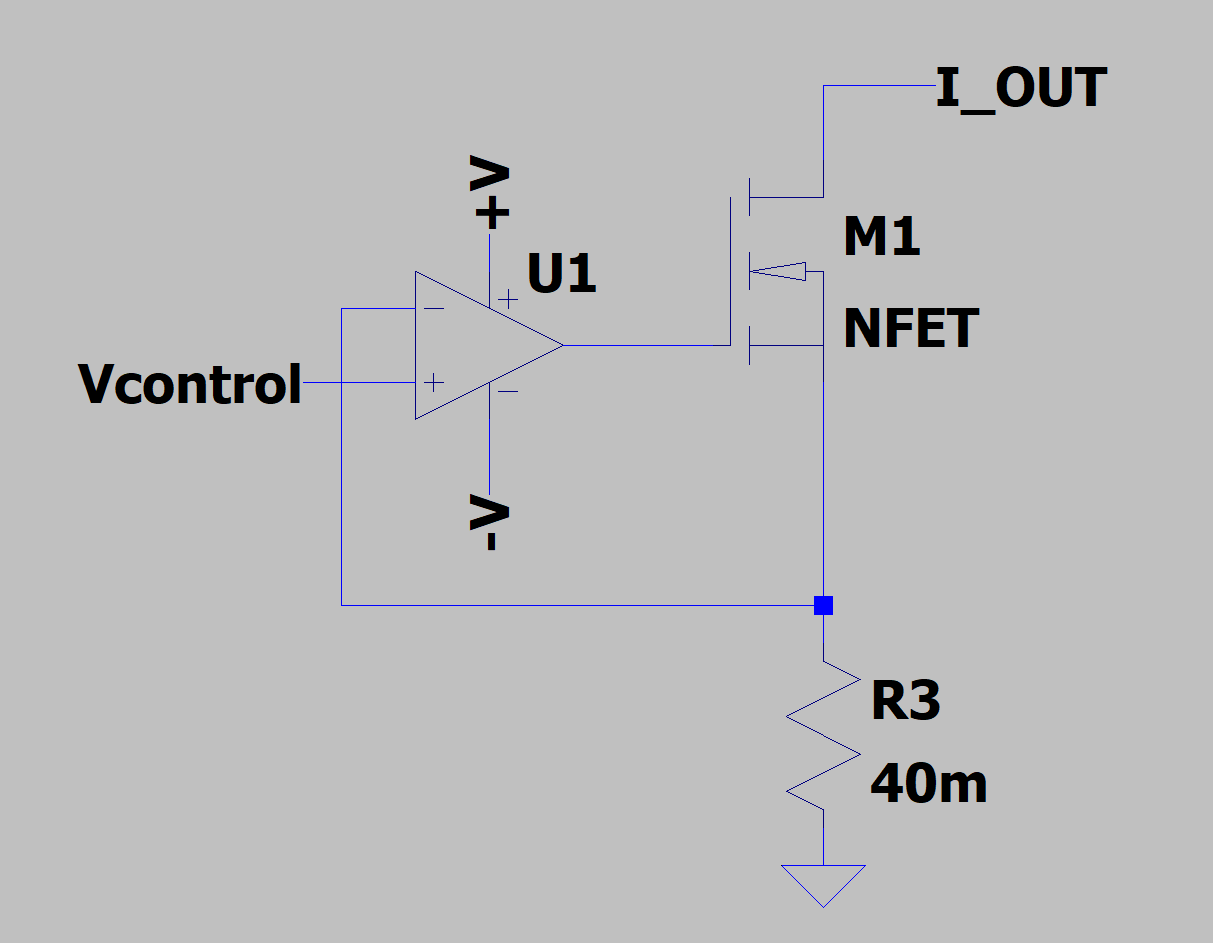

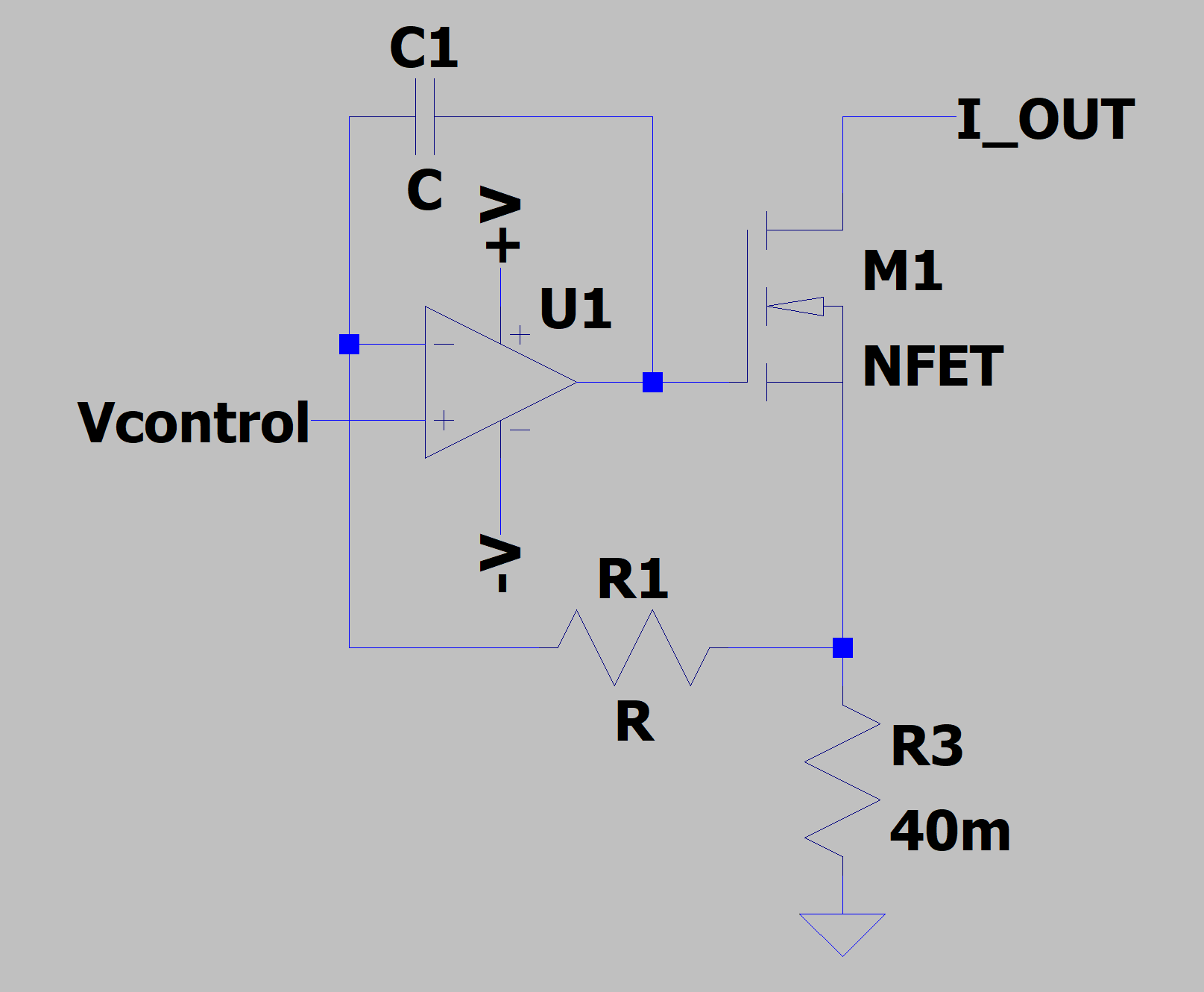

I've wanted to do my own current load for ages, but getting the current loop right always made me run away from the project as it seems too daunting a task. I was interested in doing my own take on this, but learning from your current loop.

My goals are slightly different from yours and I was aiming for a minimum of 20A current (I'm not decided on voltage yet) as that's more within the range of what I want to test.

Would I be correct in saying that simply tripiling up the current sense resistors (R6,R7,R13,R14) would triple the current in the loop?

If so, it would be a simple change to get the loop into the spec I'm looking for.

The only other thing I see that I'd need to change is the gain around U3 which I believe would be as simple as changing R27 to soimething like 33K or lower?

Great work on the project by the way!

JB