Mackerel-08

Based on the original prototype hardare, this SBC combines the 52-pin PLCC MC68008, a 512KB EEPROM, up to 3.5MB of SRAM, and a XR68C681 DUART on a single PCB. The DUART exposes two serial ports and three bit-banged SPI headers. One of these headers is currently used with an SD card breakout board to provide bulk storage to the system.

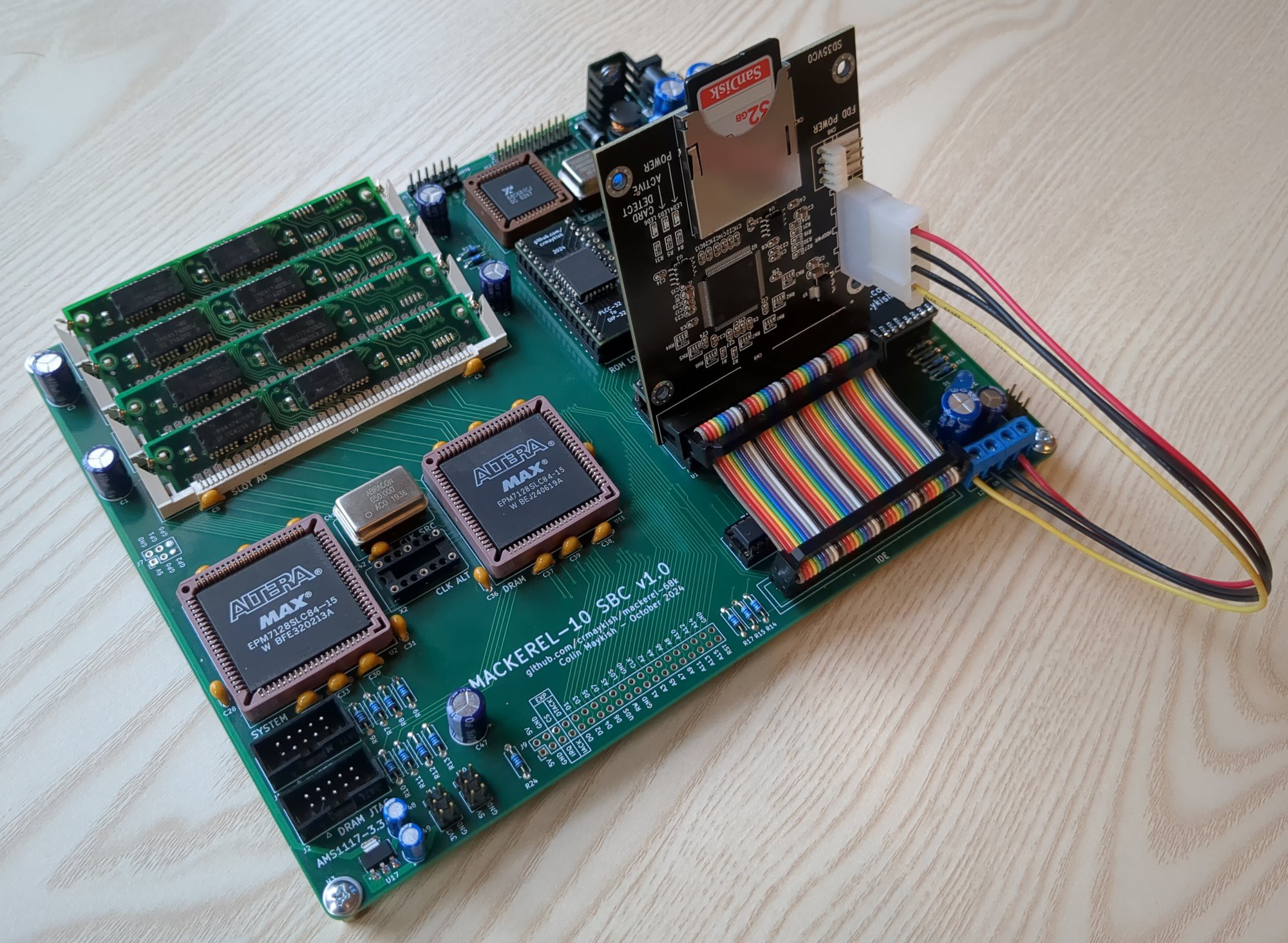

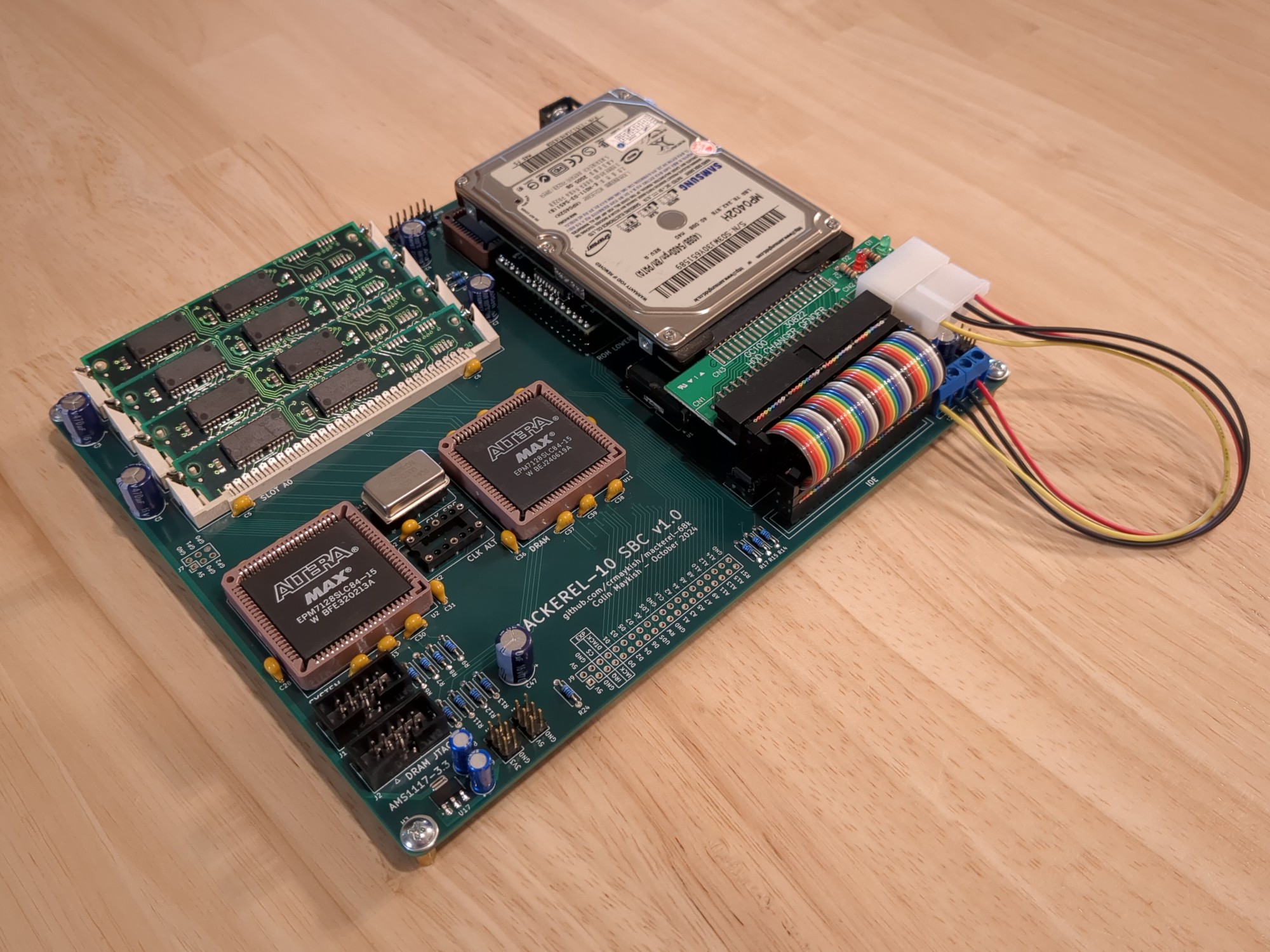

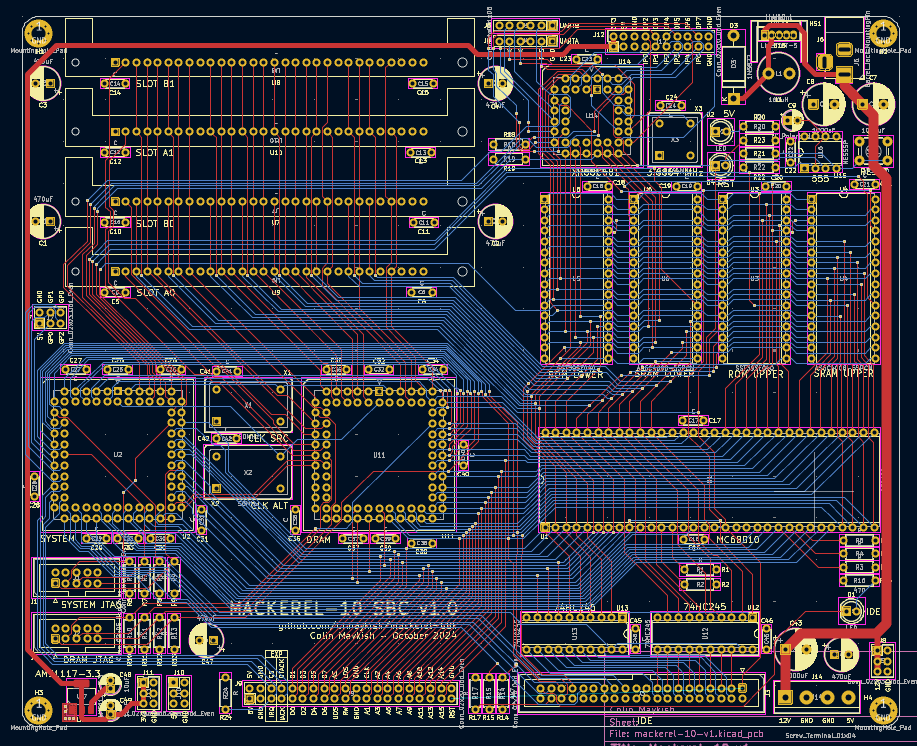

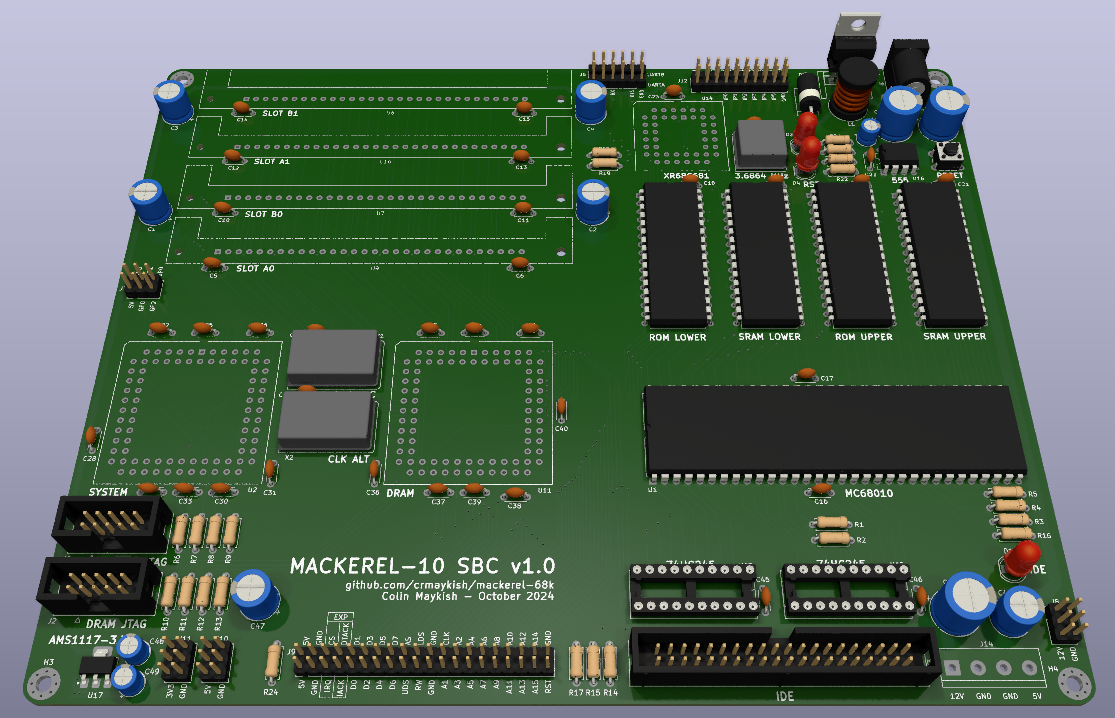

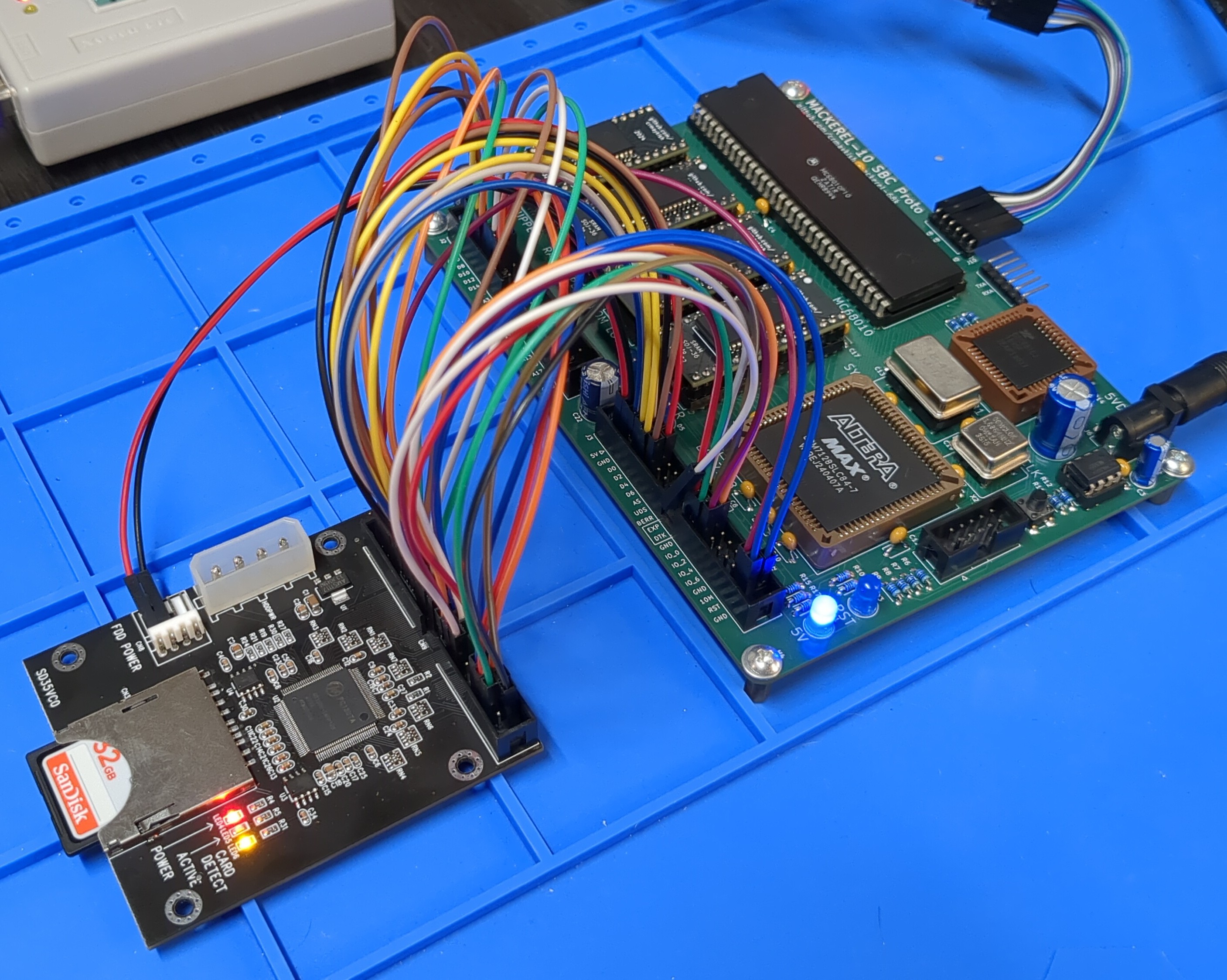

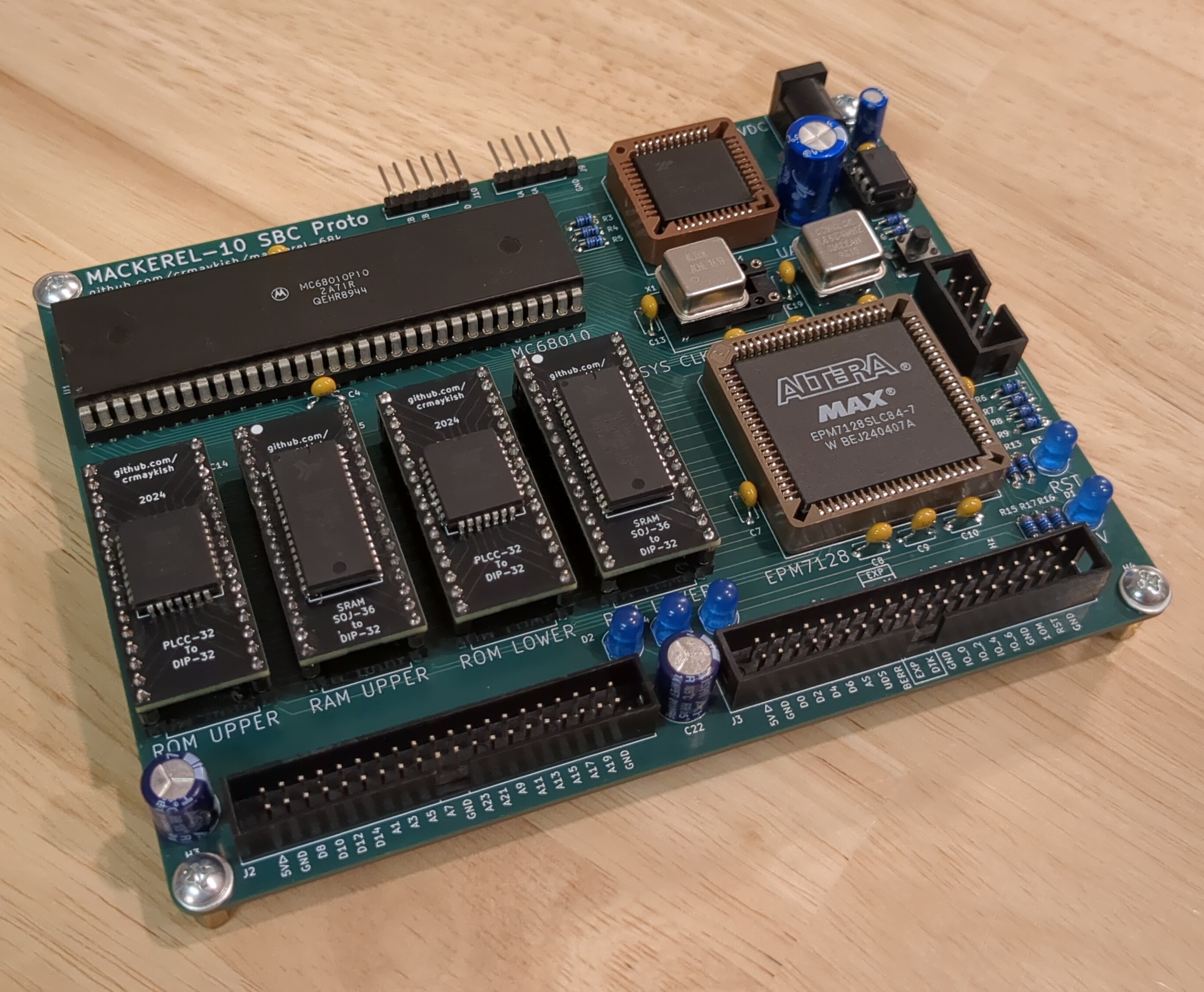

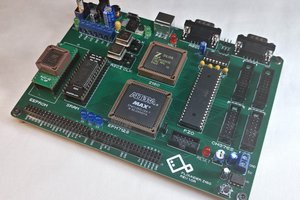

Mackerel-10

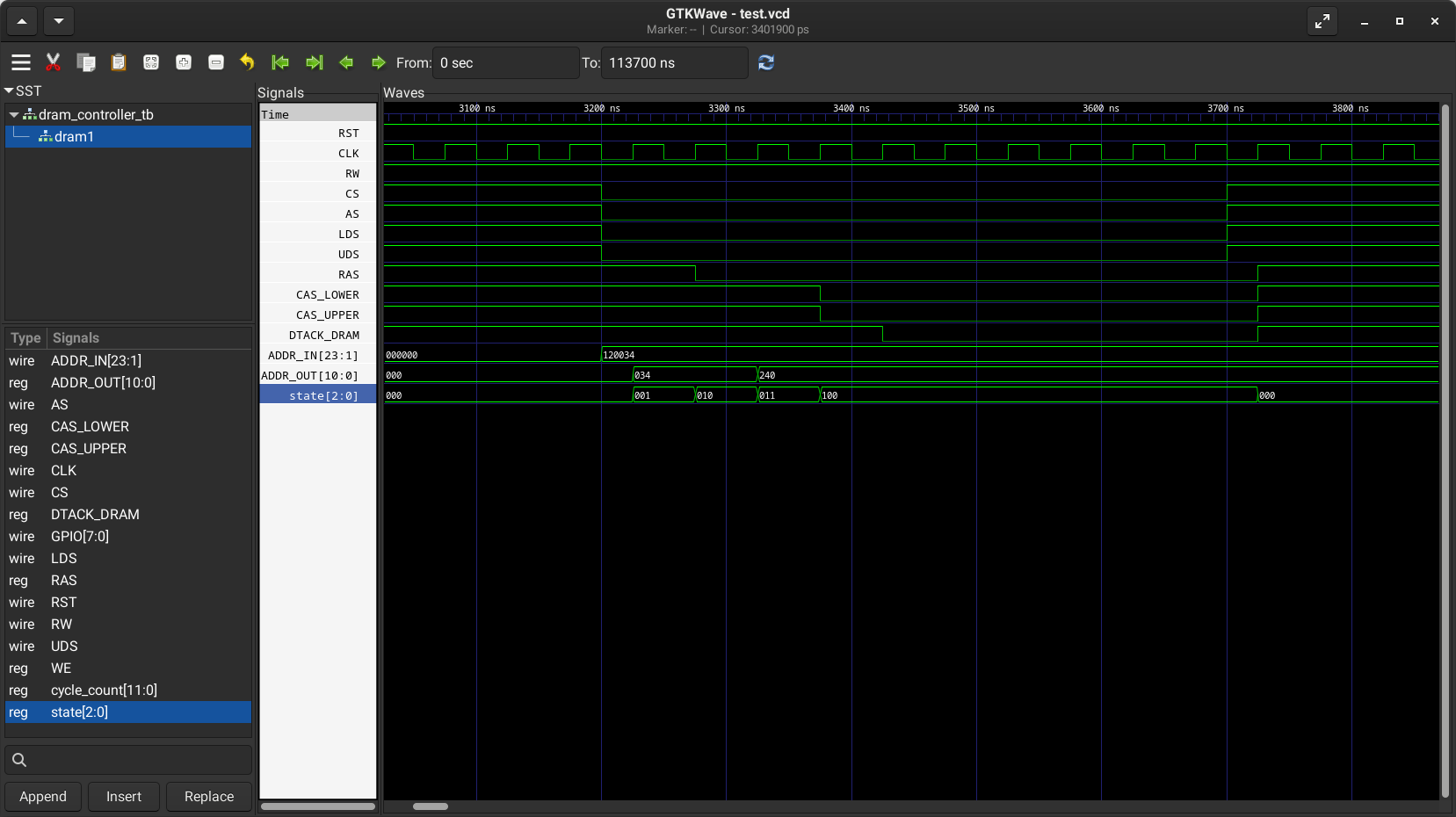

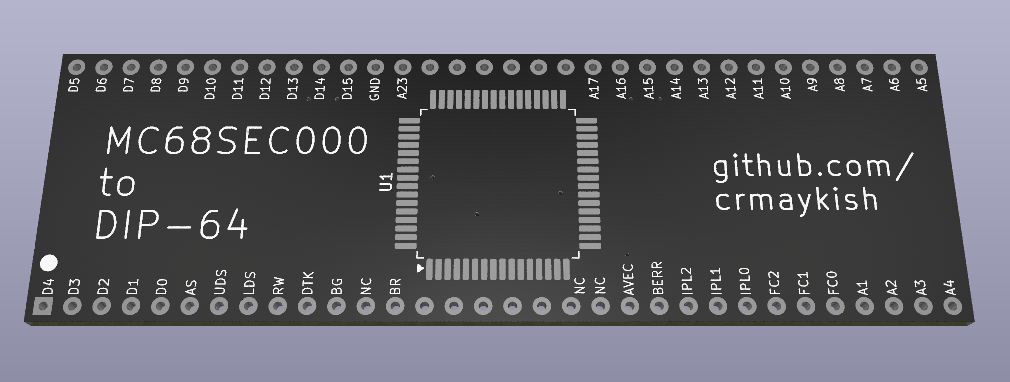

Mackerel-10 is the second phase of the project, It expands the design of Mackerel-08 with a 68010 CPU and 16-bit databus. Additionally, it increases the memory capacity with a DRAM controller implemented in a CPLD and up to 16 MB of 30-pin SIMM DRAM. An IDE header allows a hard drive or CF card to be connected as persistent storage.

Mackerel-30

Based on the fully 32-bit 68030, Mackerel-30 adds a MC68882 floating point unit, 64 MB of 72-pin DRAM and support for modern Linux.

Colin M

Colin M

Tobias Rathje

Tobias Rathje

Jason Westervelt

Jason Westervelt

Tom

Tom

What speed are the 22v10c parts, on your BOM you left off the speed