SELLING KITS

Now, there is a KIT available, to build your own Isetta !

You can order your kit at the new Envionic website ! (No HTTPS yet)

The first kit was successfully built by Vadim.

(If you want a complete Isetta, without soldering it yourself, contact me. If there is enough interest, I want to supply fully built Isetta computers, expected for around 200 euros.)

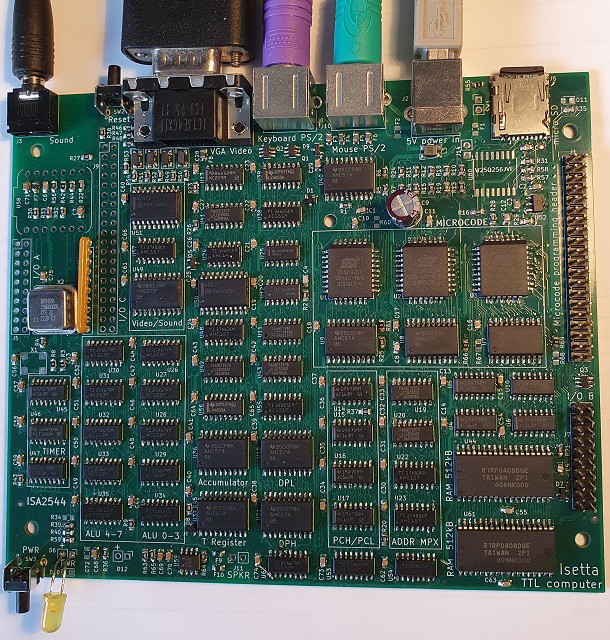

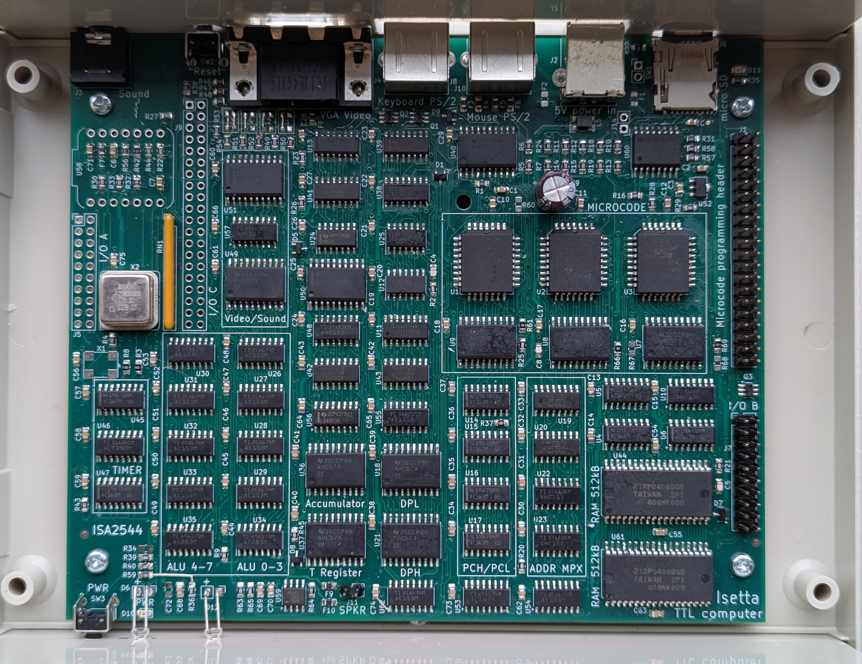

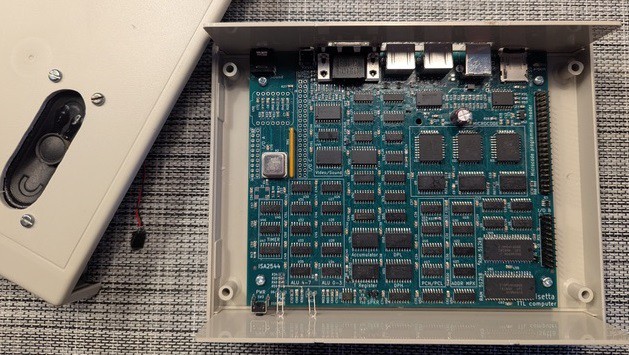

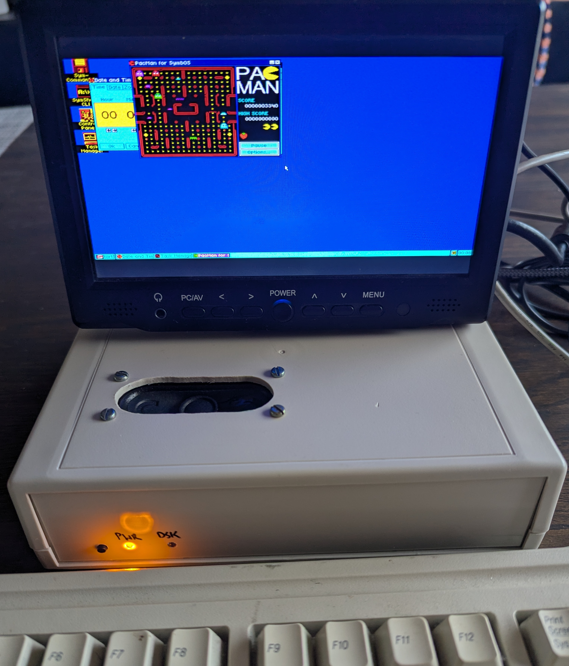

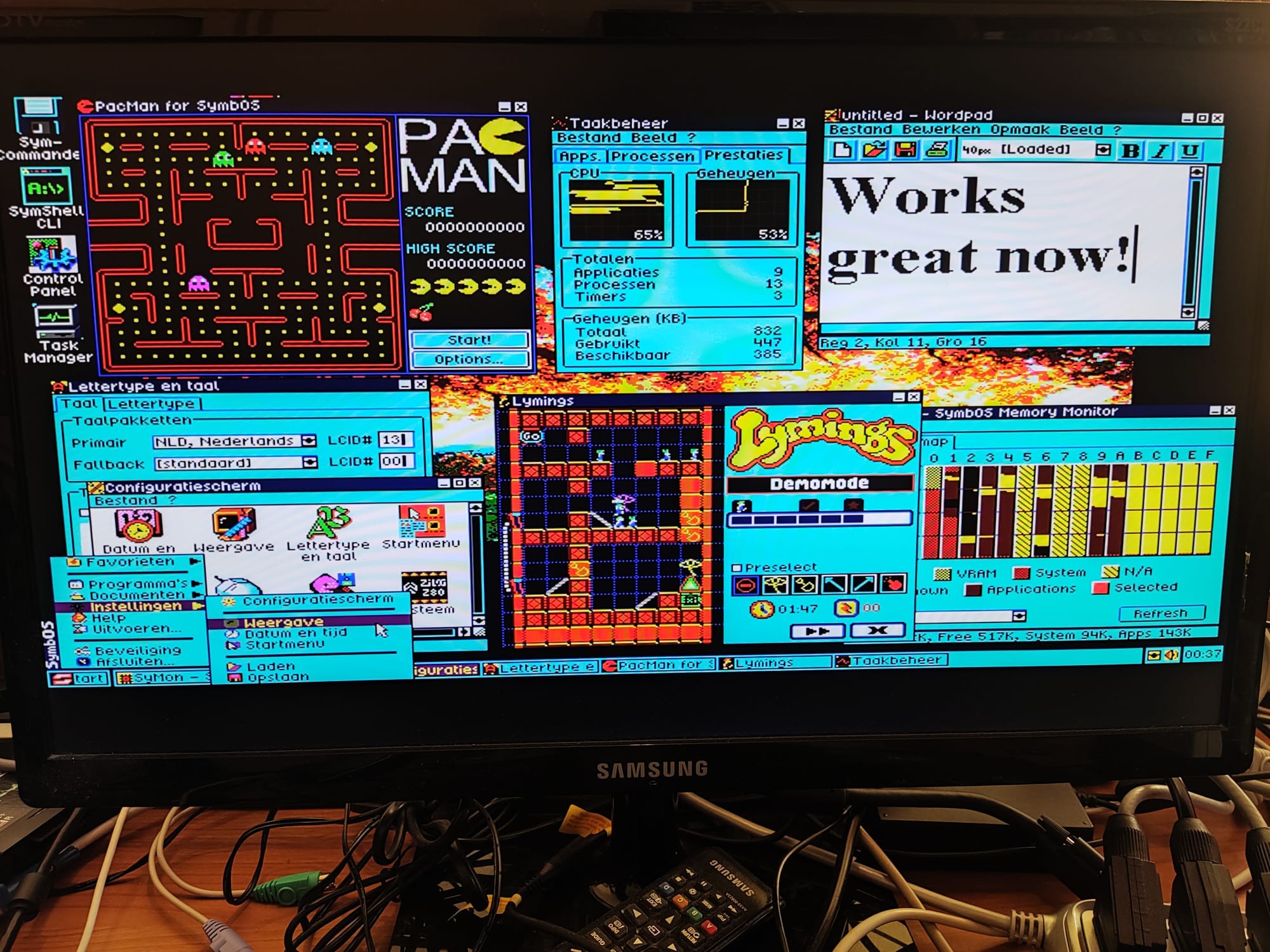

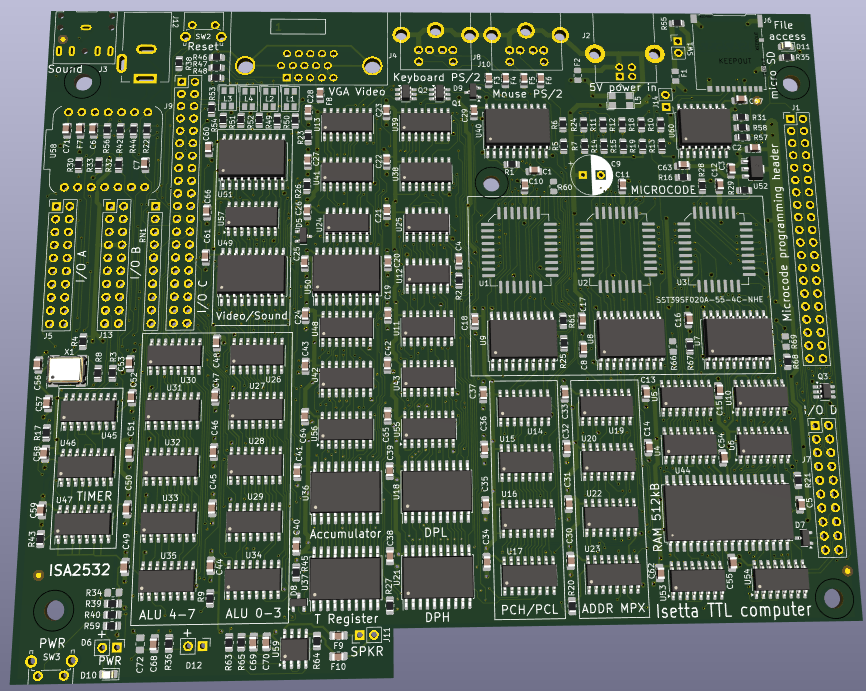

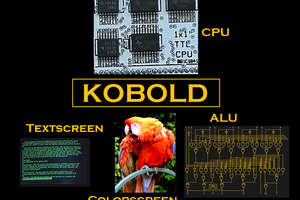

HOW DOES IT LOOK

SPECIFICATIONS

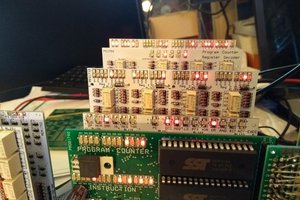

CPU:

- Runs Z80 and 6502 code

- Speed 12.5 MHz (80 nS cycle time)

- Memory 1024 kByte RAM (with bankswitching)

- programmable/upgradeable microcode (3 flash chips)

- 42 integrated TTL circuits. No microprocessor or FPGA.

I/O:

- video VGA 320 x 200 (64 colors), or 640 x 400 (16 colors)

- keyboard and mouse (both PS/2)

- sound generator (AY-3-8910 compatible)

- real time clock

- microcoded video processor, sound processor, I/O processor

- 9 integrated TTL circuits for the I/O

Storage:

- micro-SD card (removeable)

Connectivity:

- WiFi on-board (future)

- Bluetooth BLE (future)

- LoRaWan (future)

Applications:

- SymbOS operating system

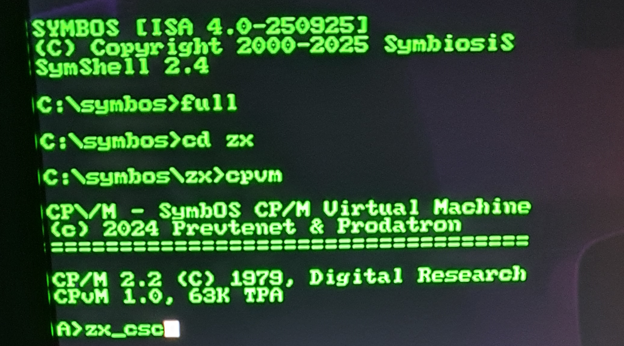

- Runs CP/M (as SymbOS application)

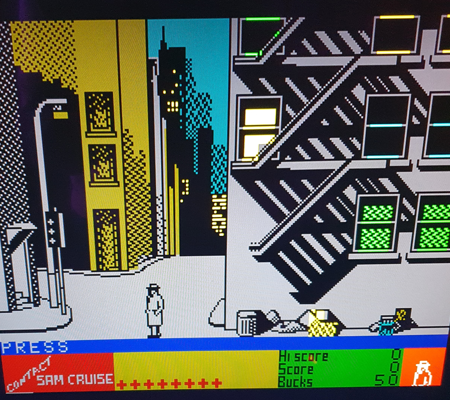

- Runs ZX Spectrum games

- Runs several BASICs (Apple I, Altair, TRS80)

Other:

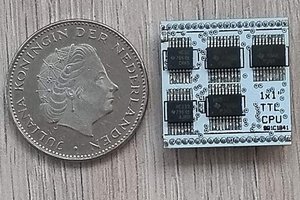

- pcb 152 x 127.5 (6 x 5 inch), 4 layers.

- powered by 5V USB

Principles for the design:

- No microprocessor, microcontroller, SOC, FPGA, CPLD, GAL, PAL or 74181

- All components have good availability at the big distributors

- Low number of components

- No fine-pitch devices that are difficult to solder (resistors, capacitors are all 0805 types)

DISCUSSION

For questions or tips/remarks you can use the discussion section at the end of the main page. Or you can send a PM, join the discussion at the RetrocomputingForum / Isetta, or use the email address at the contact page of envionic.com.

BTW, where do you come from ?

IDEA

The idea for this design was born at the end of januari (2023).

The heart of a computer is the CPU. In most computers, the CPU is a single integrated circuit (a Microprocessor). But it is also possible to build your own CPU from parts that perform simple functions. I wanted to build the CPU from parts of the TTL family. That are integrated circuits, that can perform elementary logic functions. They were first used in the 60's of the previous age. I use a modern version of these circuits, that use less power.

There are many homebuilt CPU's, and most of them have their own, unique instruction set. But when such a computer is built, you must make all software yourself ! It would be nice if existing software could run on the homebuilt CPU.

Therefore, I decided that for this project the CPU would use an existing instruction set.

So which instruction set to use ? The CPU inside your laptop or cellphone is much, much too complex to build. But it is possible to use an older CPU from the time when microprocessors just became available. There were two processors that can be regarded as the Beetle and the Deux Cheveaux of the beginning of the homecomputer age.

These processors are the MOS Technology 6502 and the Zilog Z80.

The 6502 is famous because it was the heart of the Apple 1, the Apple ] [, the Commodore 64, the Nintendo NES and many others. The Z80 is well known because it was used in the TRS-80, the ZX Spectrum and the MSX computers, and it was widely used to run the CP/M Operating system, see also this Z80 introduction video.

So now, I had to decide whether to use the instruction set of the 6502 or that of the Z80. But then I thought... why not build...

Read more »

Marcel van Kervinck

Marcel van Kervinck

Dr Matt Regan on YouTube has an entire series on microcoded TTL computers, and has done 6205 emulation, culminating in an Apple II clone) as well as the Z80, culminating in both Sinclair ZX80+ and Spectrum clones.

https://youtube.com/@drmattregan?si=3HBWGR9niP8KzCvZ