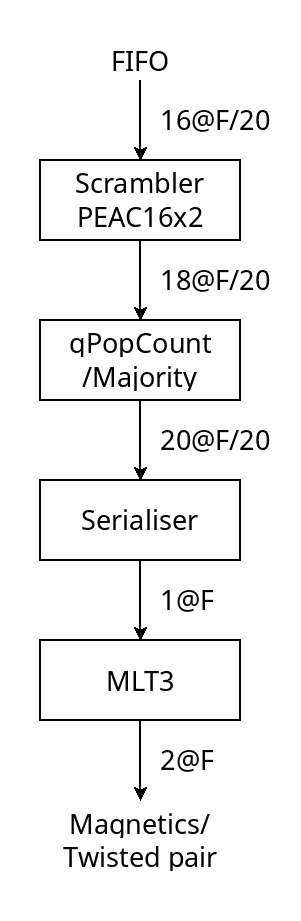

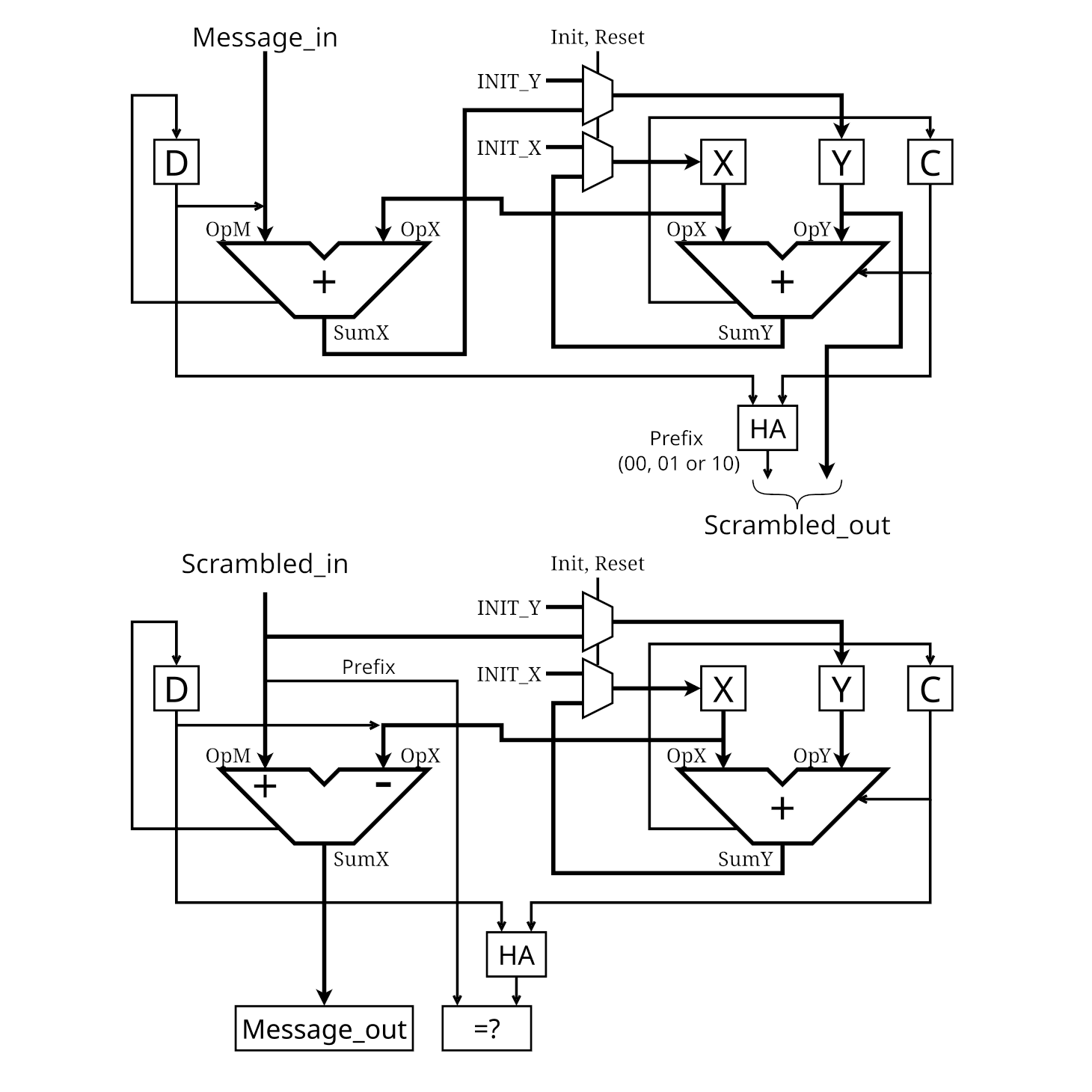

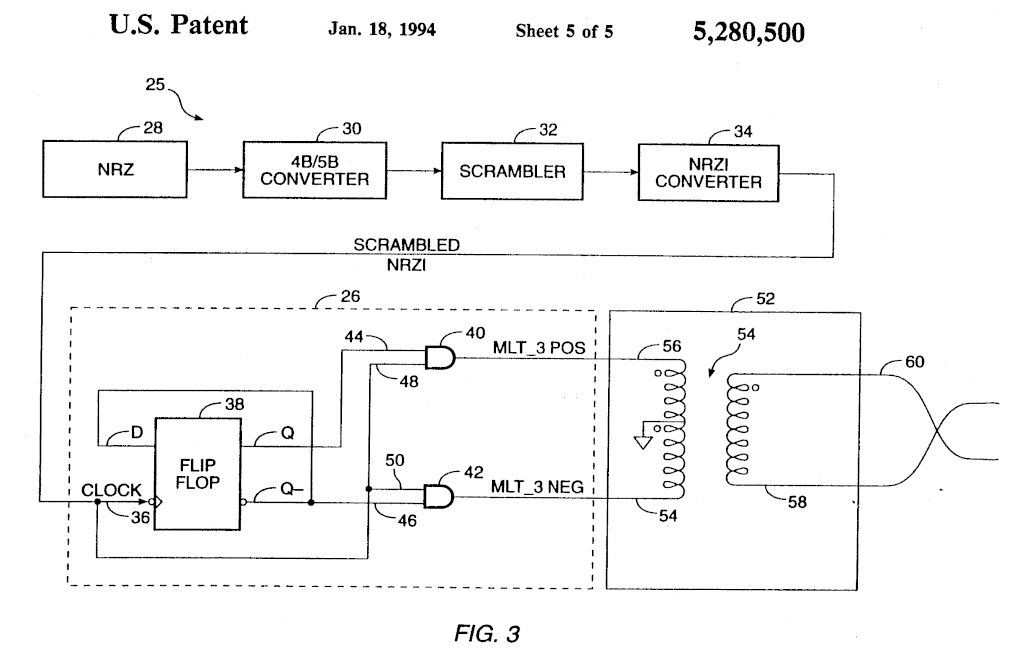

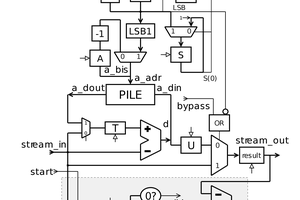

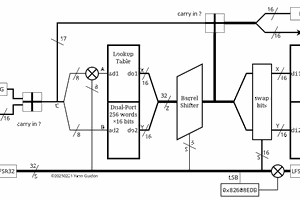

So this is an extension and application of #PEAC Pisano with End-Around Carry algorithm because the PEAC algorithm replaces the scrambler and the 4b/5b table, see

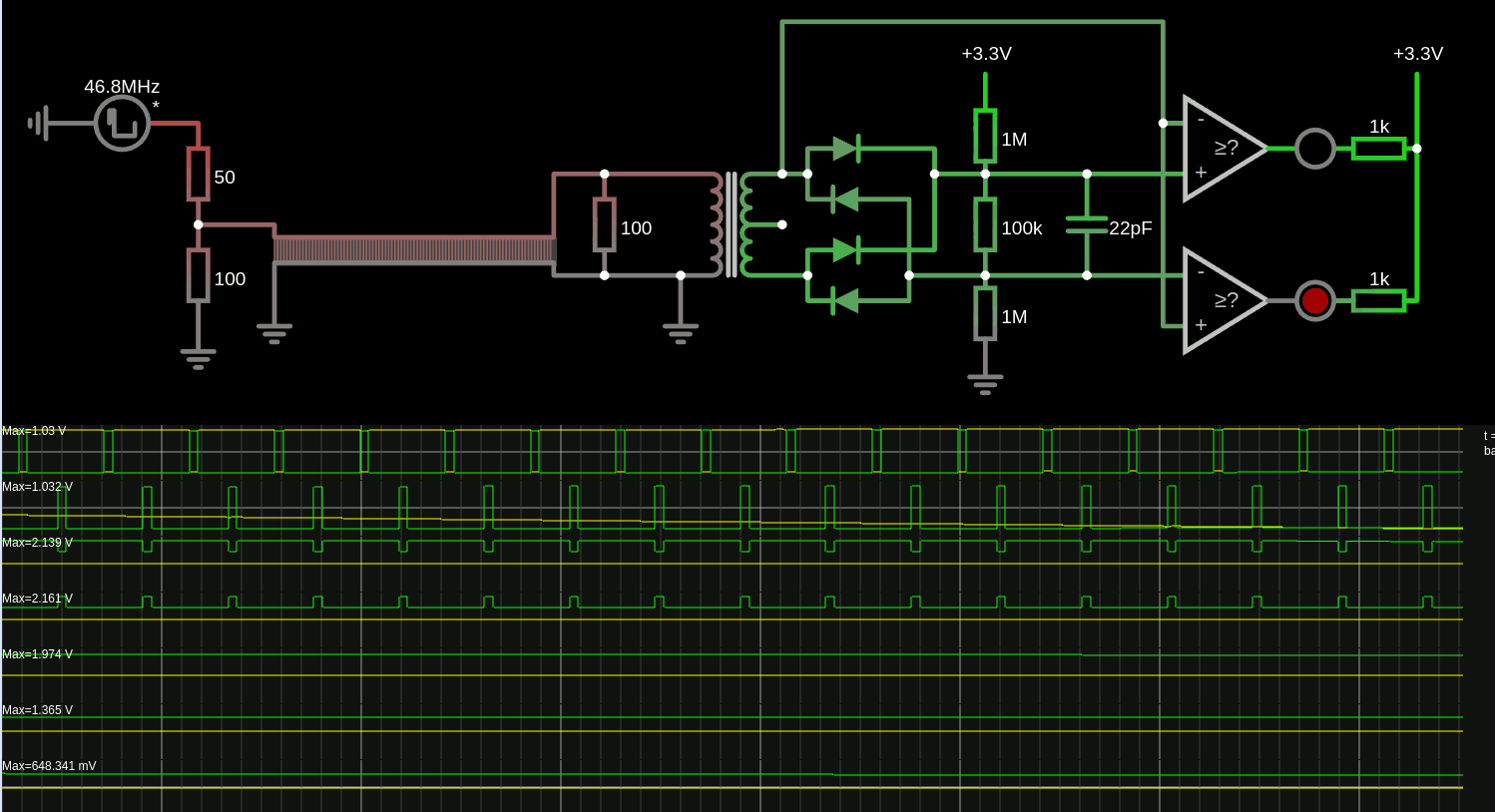

166. Line encoding with PEAC : OK

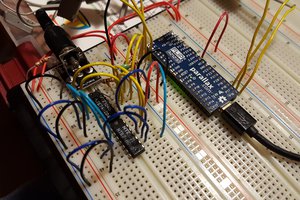

167. Line encoding with PEAC: it's alive

168. PEACLS error detection (and correction?)

169. TODO: scan

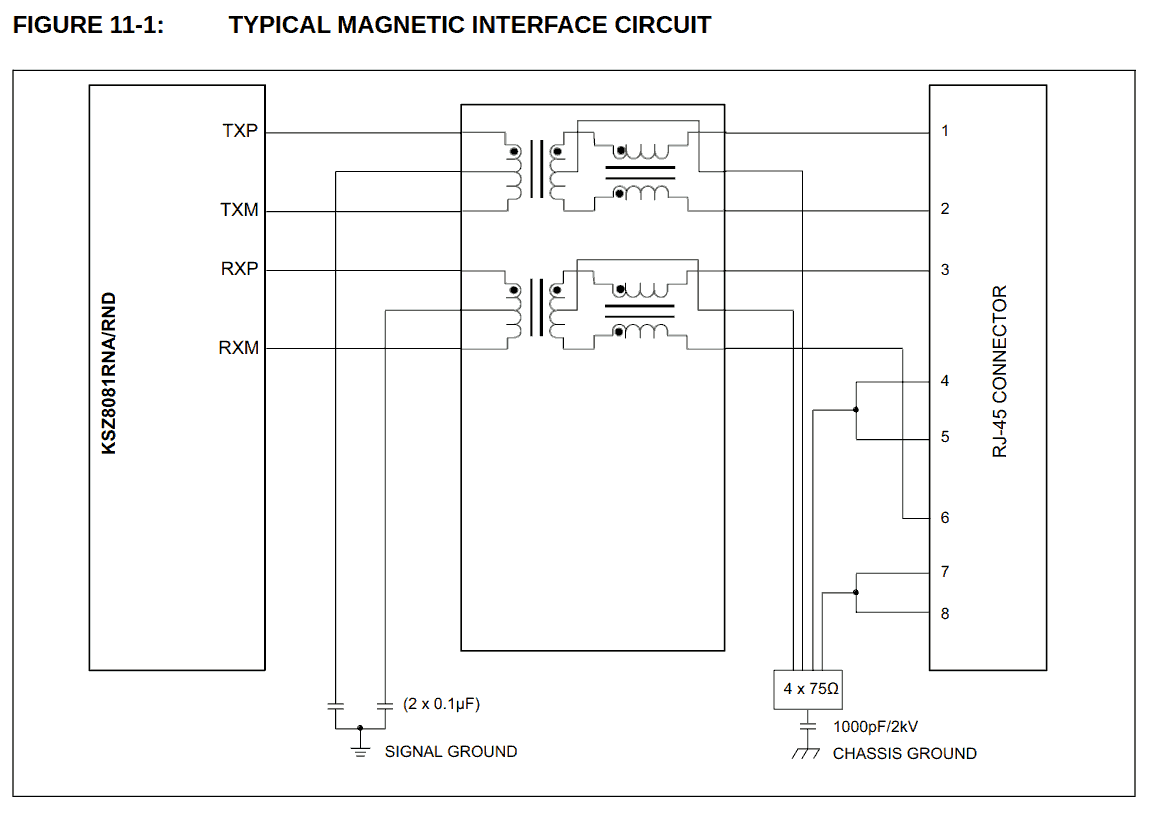

Application is for embedded/custom data transfers over RJ45/Cat5 UTP/STP where the whole TCP/IP stack is not required and a simple FPGA/microcontroller are more than enough.

.

.

-o-O-0-O-o-

Logs:

1. Let's start.

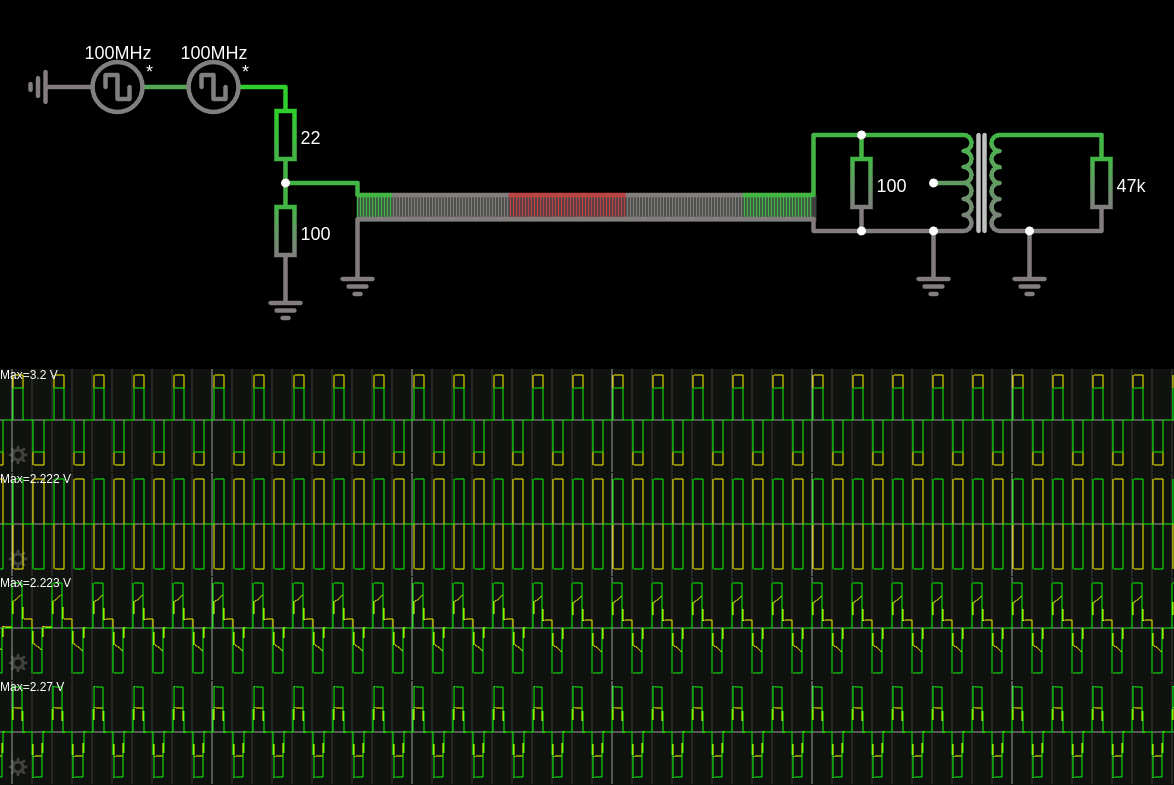

2. Tinkering with CircuitJS

3. AGC

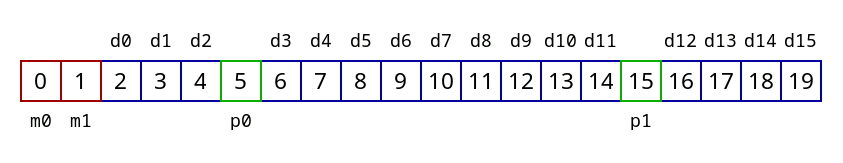

4. Serial vs Parallel

5. Sender-side droop/wander prevention with MLT-3

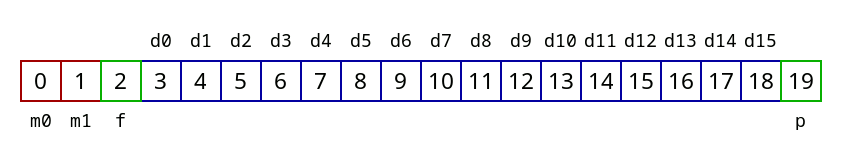

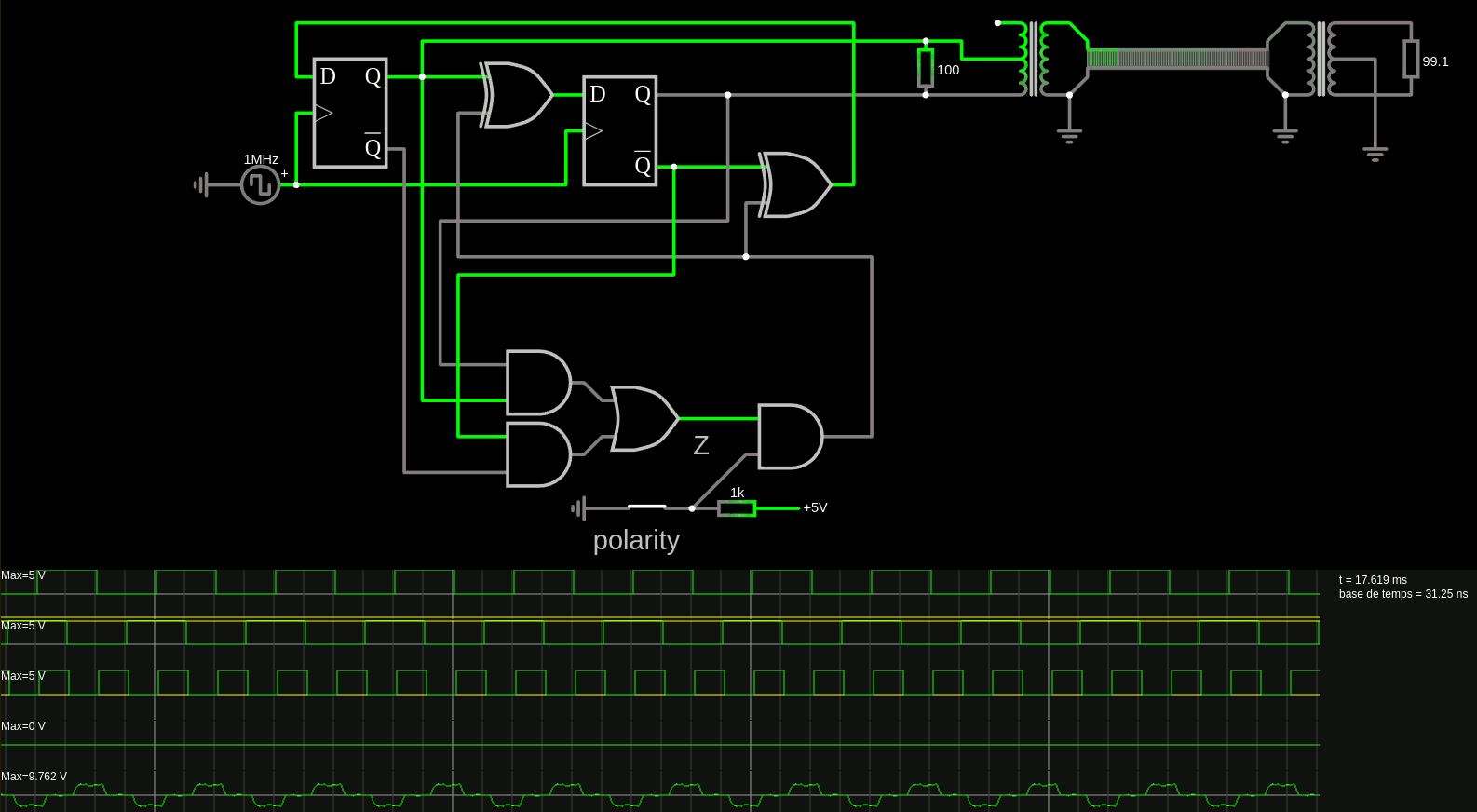

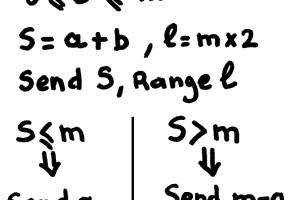

6. Double parity

7. Flipping

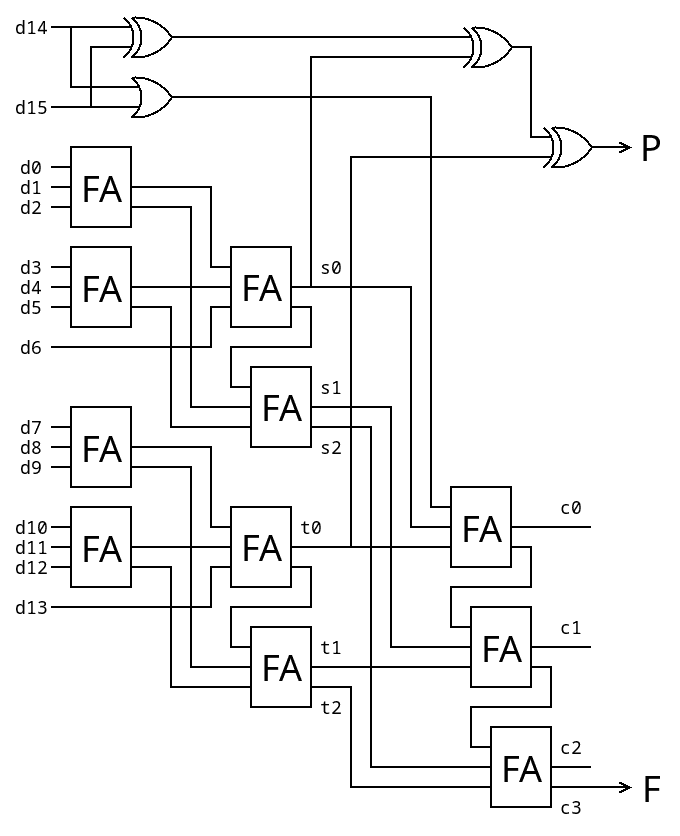

8. a Quasi-Popcount

9.

10.

.

Yann Guidon / YGDES

Yann Guidon / YGDES

Jac Goudsmit

Jac Goudsmit

The seminal 64b/66b paper : http://www.omnisterra.com/walker/pdfs.talks/dallas.pdf